Method for analyzing and increasing yield of semi-conductor production line

A yield and production line technology, applied in the field of analyzing and improving the yield of integrated circuits, can solve the problems of different sensitivities, low efficiency of measuring equipment, and increase the difficulty of setting effective sensitivity, so as to achieve the effect of improving the speed of improvement.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

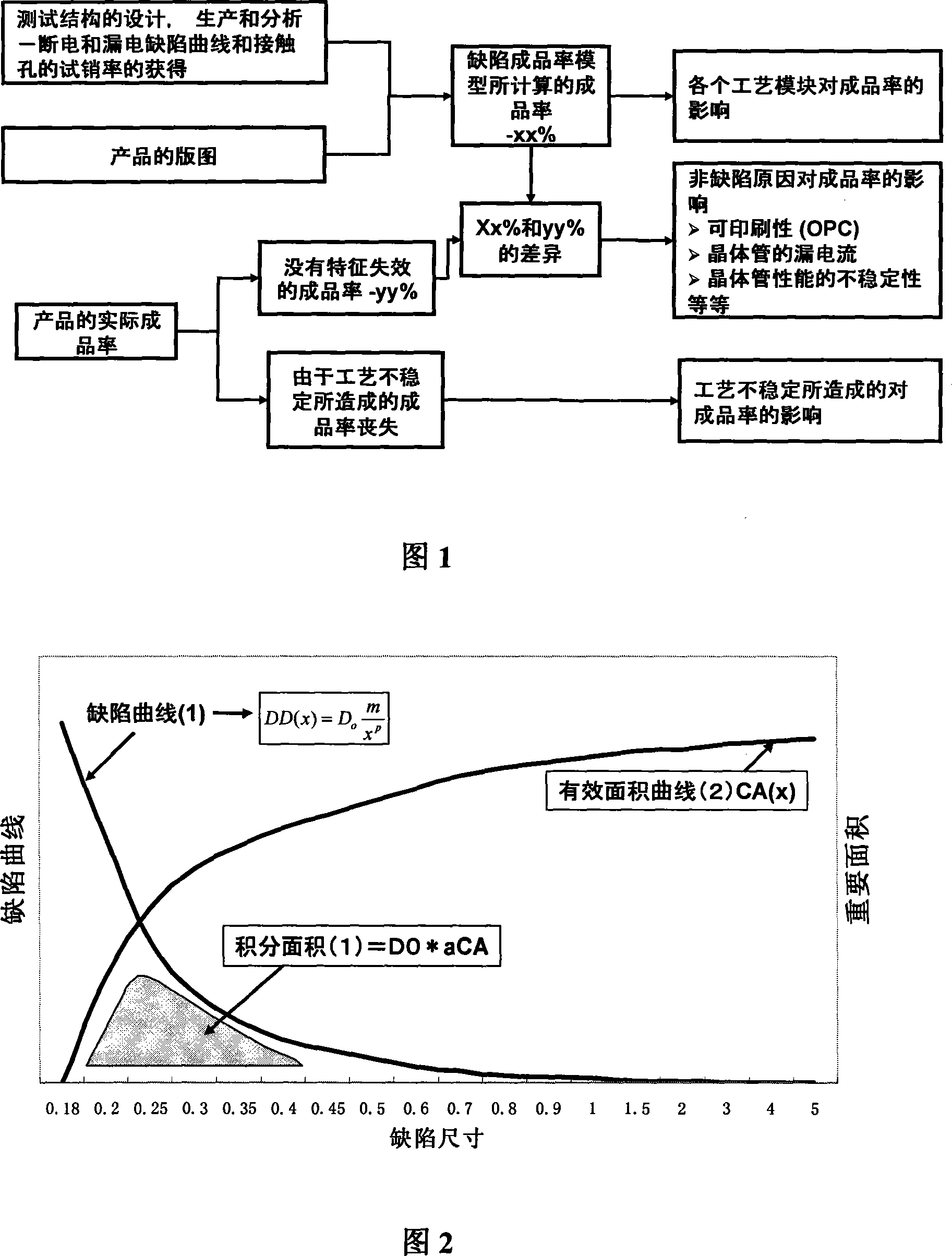

[0118] Now adopt typical data to illustrate the present invention in conjunction with the program flow of Fig. 1:

[0119] 1. Acquisition of defect curves of various process modules in semiconductor production lines

[0120] FIG. 7 shows a test circuit in a test chip for obtaining the defect rate of the first-layer metal M1 of power-off and leakage. This is a collection of comb-shaped and P snake-shaped metal wires.

[0121] Here, P=4 is used to illustrate how to obtain the defect rate curves of power failure and leakage through electrical measurement.

[0122] For the power down measurement, there will be 4 measurements - Line 1, Line 2, Line 3 and Line 4.

[0123] For leakage measurement, there will be 3 measurements - leakage from line 1 to line 2, leakage from line 2 to line 3, and leakage from line 3 to line 4.

[0124] For the measurement of power failure, in a tested circuit unit, the following situations will occur:

[0125] 1) A single line is broken (no adjacent ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More