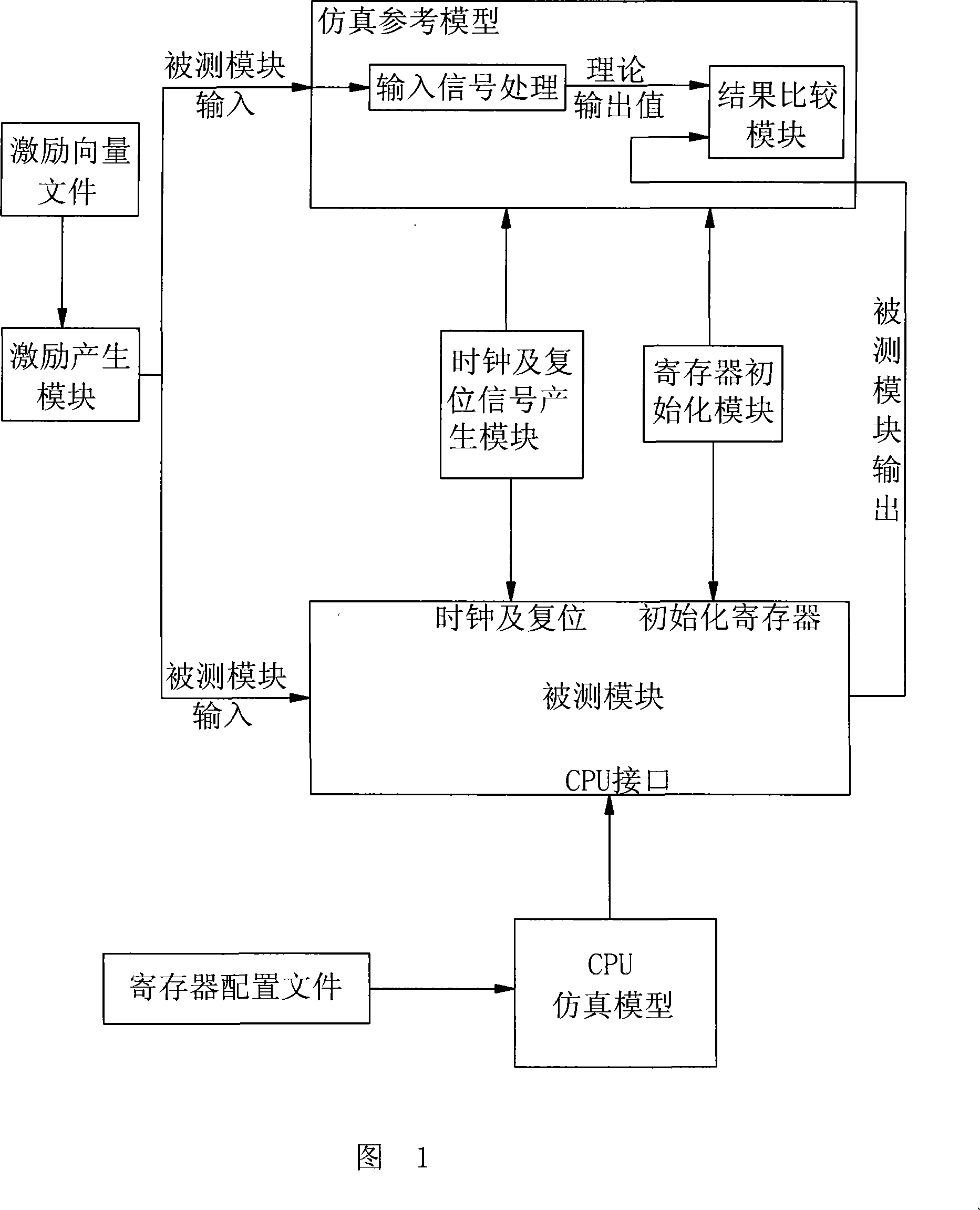

Method for establishing network chip module level function checking testing platform

A test platform and network chip technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as huge workload and time-consuming, and achieve the effect of clear structure, reduced setup time, and easy to understand

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] Most of the steps of the establishment method of the network chip module-level function verification test platform are completed by using the perl language.

[0042] First create a register table file based on all externally accessible registers of the module under test. The register table file should include: address of the register, read / write type, data bit width of the register, valid bits of the register and initial value of the register. This step is done manually according to the definition of the register.

[0043] Use the perl language to read the register table file line by line, and generate the register initialization module and register configuration file according to the register name and initial value;

[0044] Using the perl language, according to the syntax of the hardware description language, the instantiation of the tested module is generated according to each input and output port of the tested module;

[0045] Use perl language to give different v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More