Information processing device

An information processing device and source information technology, which is applied in the direction of machine execution devices, electrical digital data processing, program control design, etc., can solve inconvenience and other problems, and achieve the effect of avoiding repeated access and shortening the memory access time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

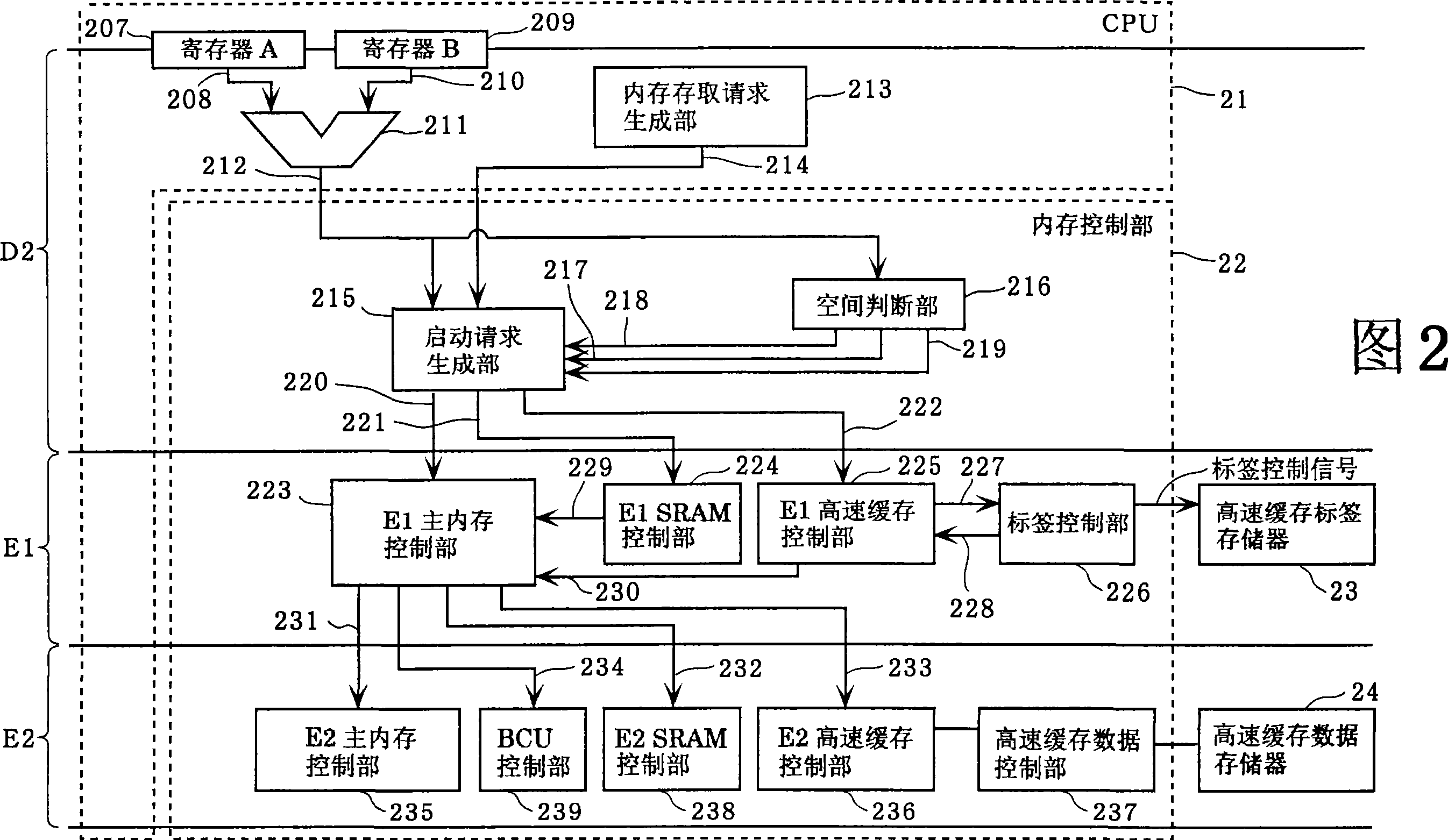

[0134] First, the information processing device of Embodiment 1 will be described.

[0135] FIG. 4 shows the structure of the information processing device of the first embodiment.

[0136] In the first embodiment, it is assumed that the memory access command executed by the CPU 21 instructs memory access using an access address generated by adding the value of the register A 207 and the value of the register B 209 . In addition, when generating the address by the above-mentioned addition, it is assumed that the address is generated by adding the 32-bit value of the register A207 and the lower 16-bit value of the register B209.

[0137] The register A output 208 output from the register A 207 is input to the spatial prediction unit 401 .

[0138]The space prediction unit 401 predicts which space the access address 212 should belong to based on the value of the register A output 208 .

[0139] The space prediction unit 401 outputs part of the SRAM space prediction signal 402 ...

Embodiment 2

[0181] Next, an information processing device according to Embodiment 2 will be described.

[0182] FIG. 10 shows the configuration of an information processing device according to the second embodiment.

[0183] The information processing device of the second embodiment is a device capable of controlling the clock supply to the cache tag memory 23 , that is, a device in which the clock control unit 803 stops the clock supply to the cache tag memory 23 by using the tag clock permission signal 801 .

[0184] In the second embodiment, as in the case of the first embodiment, the space prediction unit 401 performs space prediction to control access to the memory and also controls the clock supply to the cache tag memory 23 .

[0185] The E1 cache control unit 225 supplies the tag clock permission signal 801 to the clock control unit 803 only when controlling access to the cache. That is, the tag clock permission signal 801 becomes valid only when the E1 cache control unit 225 is ...

Embodiment 3

[0195] Next, an information processing device according to Embodiment 3 will be described.

[0196] FIG. 13 shows the configuration of an information processing device according to the third embodiment.

[0197] The information processing device of Embodiment 3 will quickly perform spatial prediction.

[0198] In the information processing device of FIG. 13 , when writing a value to the register A207, when the value of the register A207 is used to generate an access address for accessing the memory, the judgment result indicating which space it belongs to is first held. This judgment result is used in the spatial prediction in the D2 stage in another holding unit.

[0199] The register A write data generation unit 111 generates register A write data 112 which is data to be written into the register A 207 . The register A write data 112 is input not only to the register A 207 but also to the decoding unit 113 which judges which address space it belongs to when it is used as a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More