FPGA circuit fault detecting apparatus

A technology for detecting device and circuit faults, which is applied in the direction of redundant code error detection and response error generation, which can solve the problems of long fault detection delay, large system overhead, complex implementation, etc., and achieve power consumption optimization and system overhead Small and easy to achieve

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] In order to make the purpose, technical solution and advantages of the present invention clearer, a FPGA circuit fault detection device of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0037] The invention proposes an efficient FPGA circuit fault detection device aiming at the problems of large system overhead, long fault detection delay, complex implementation and the like in the current FPGA circuit soft fault detection method.

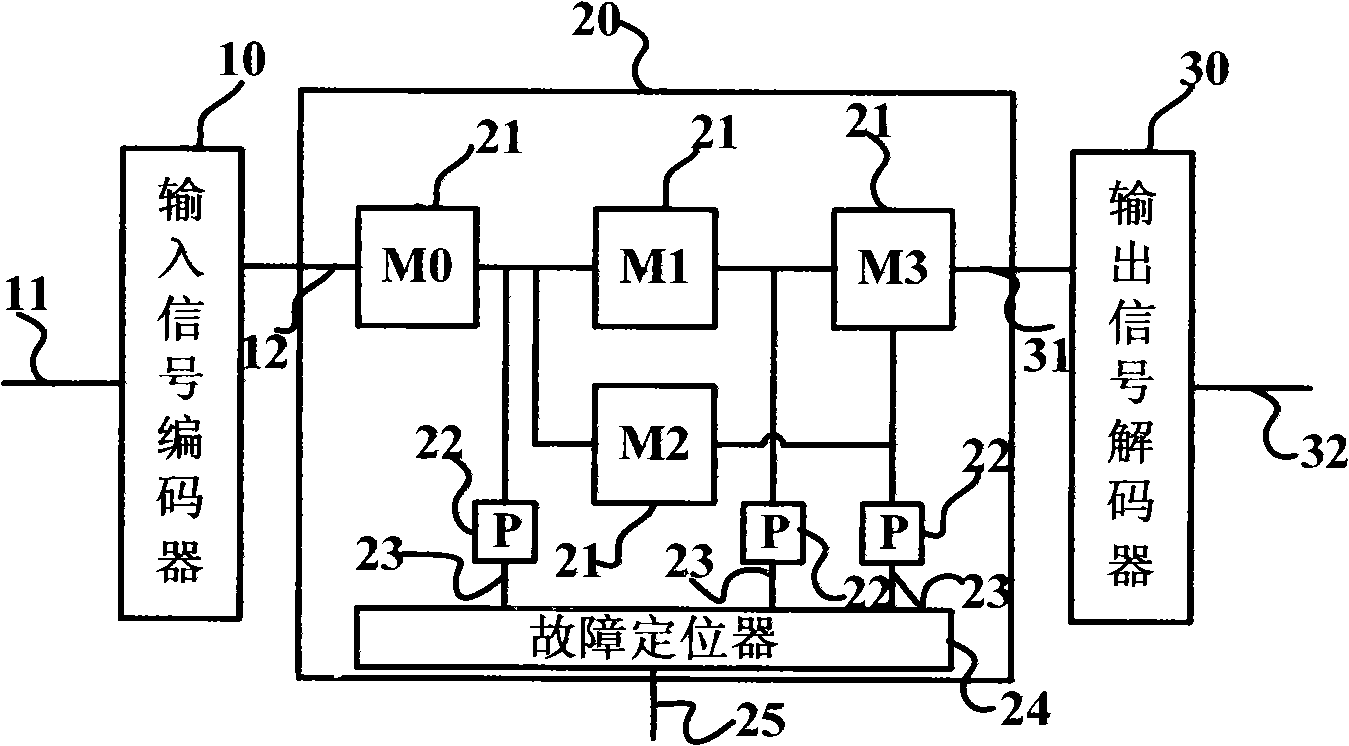

[0038] Such as figure 1 As shown, the FPGA circuit fault detection device of the present invention includes an input signal encoder 10 , an output signal decoder 30 , at least one fault probe 22 , and a fault locator 24 .

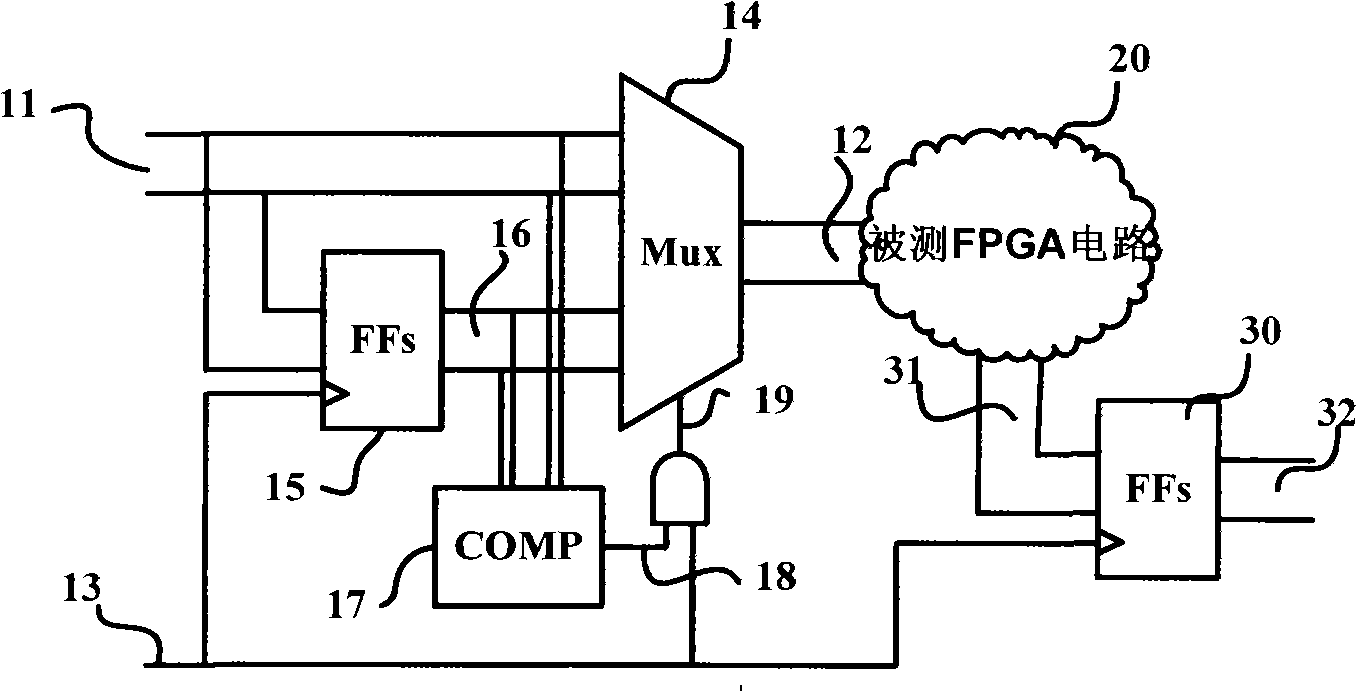

[0039] The input signal encoder 10 is configured to perform time redundant encoding on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com