Method for mapping video processor video data and memory space

A video processor and video data technology, which is applied in the field of digital video coding and decoding, can solve the problems that no solution is given, and the data access rate cannot be better improved, so as to achieve the effect of improving access bandwidth and ensuring normal operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0049] Example 1: Encoder 7-frame storage scheme

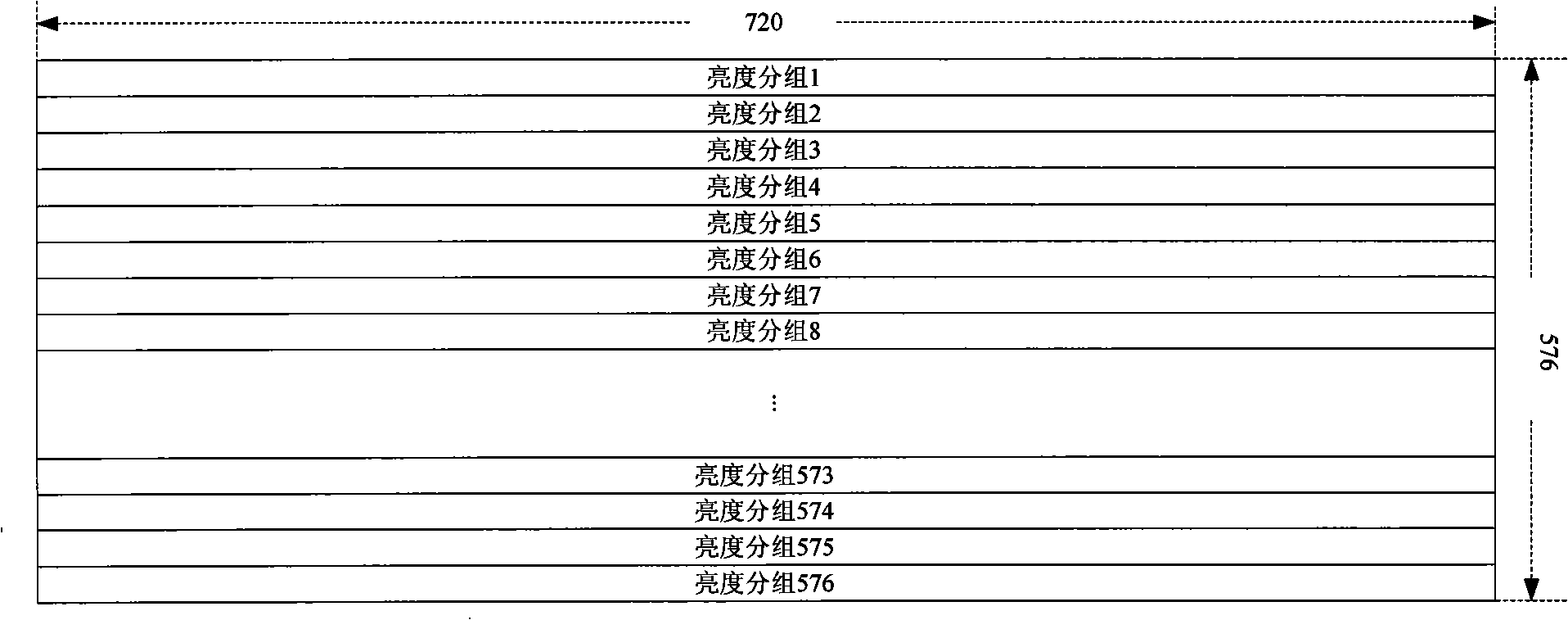

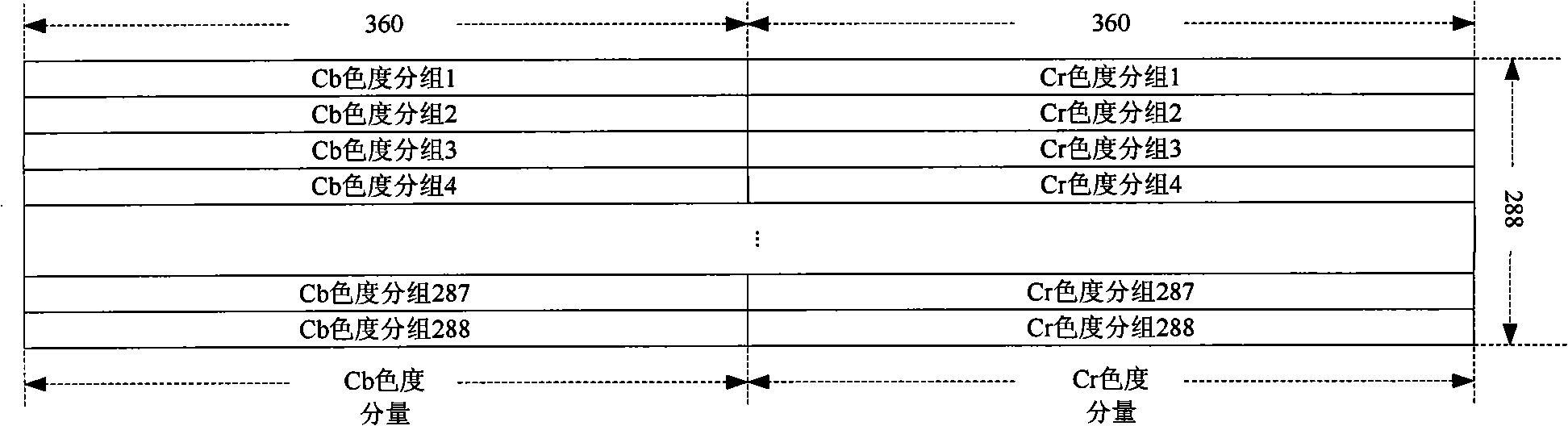

[0050] The memory used is W986432DH 512K×4BANKS×32BITSDRAM of Winbond Company, the data bus bit width of this memory is 32 bits, and the number of pages Banknum is equal to 4; the resolution of the video image is 720×576, and the sampling format is 4:2:0; That is, the proportional relationship between the brightness pixel point Y and the number of two color difference pixel points Cb and Cr is: Y:Cb:Cr is equal to 4:1:1, P frame coding refers to 2 frames of images at most, between two consecutive P frames , or there are at most two B frames between the P frame and the I frame; the video processor requires a separate storage space for the original image and the reconstructed image, and the two do not overlap each other in the memory; the processed video sequence is a frame sequence.

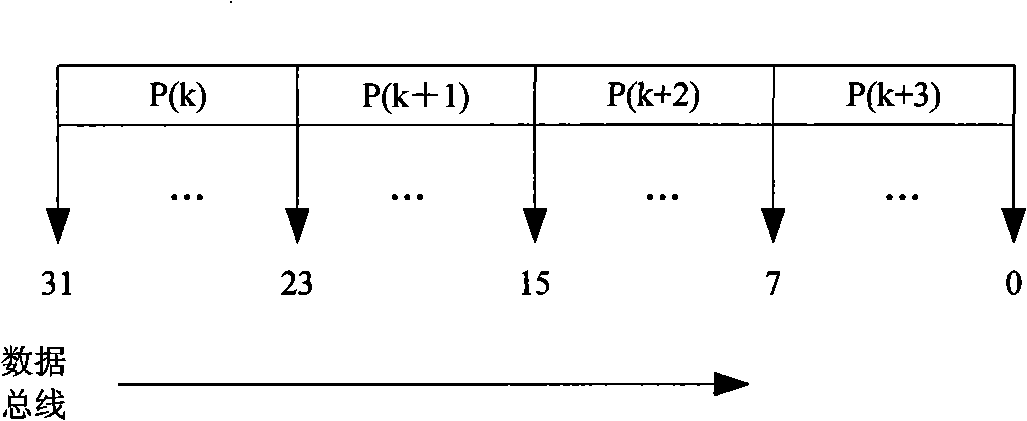

[0051] From the bit width of the data bus of the memory, it can be obtained that: PPU is equal to 4, and the situation of PPU pixels occupying th...

Embodiment 2

[0061] Embodiment 2: Encoder 6-frame storage scheme

[0062] The memory used is W986432DH 512K×4BANKS×32BITSDRAM of Winbond Company, the data bus bit width of this memory is 32 bits, and the number of pages Banknum is equal to 4; the resolution of the video image is 720×576, and the sampling format is 4:2:0; That is, the proportional relationship between the brightness pixel point Y and the number of two color difference pixel points Cb and Cr is: Y:Cb:Cr is equal to 4:1:1, P frame coding refers to 2 frames of images at most, between two consecutive P frames , or there are at most two B frames between the P frame and the I frame; the video processor allows the original image and the reconstructed image to share the storage space, and they can overlap each other in the storage space; the processed video sequence is a field sequence.

[0063] From the bit width of the data bus of the memory, it can be obtained that: PPU is equal to 4, and the situation of PPU pixels occupying th...

Embodiment 3

[0072] Embodiment 3: Decoder 4 frame storage scheme

[0073] The memory used is the MT46V8M16 type DDR SDRAM of Micron Company, the data bus of the memory is 16 bits, and the page number Banknum is equal to 4; the resolution of the video image processed by the decoder is 720×576, and the sampling format is 4:2:0; P frame decoding refers to 2 frames of images at most, and supports B frame decoding function.

[0074] From the bit width of the data bus of the memory, it can be obtained that: PPU is equal to 2, and the situation of PPU pixels occupying the address bus is as follows Figure 12 shown.

[0075] According to the number of reference frames required for decoder P frame decoding, it can be obtained that the total number of video image frames to be stored is 4. For this reason, 4 groups of initial row addresses and initial column addresses are set in the memory: the first group of initial row addresses and initial column addresses are 0 and 0 respectively, represented b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More