Semi-conductor encapsulation connecting construction avoiding welding defect induced by warp of substrate

A semiconductor and structural technology, applied in the field of high-density 3D stacking structure and semiconductor package bonding structure, to reduce the difference of solder gap, solve the warpage of the substrate, and avoid the effect of welding defects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 Embodiment

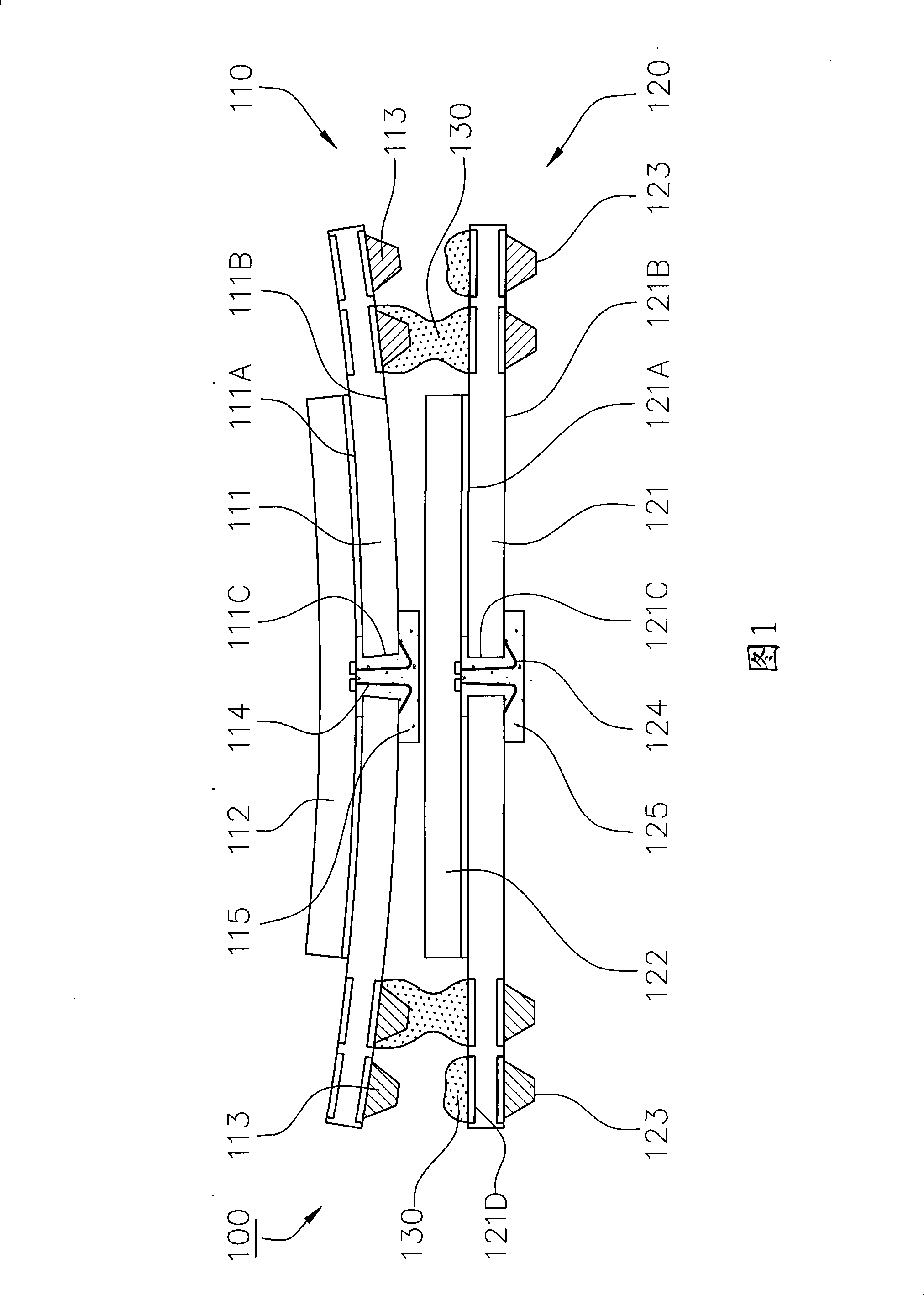

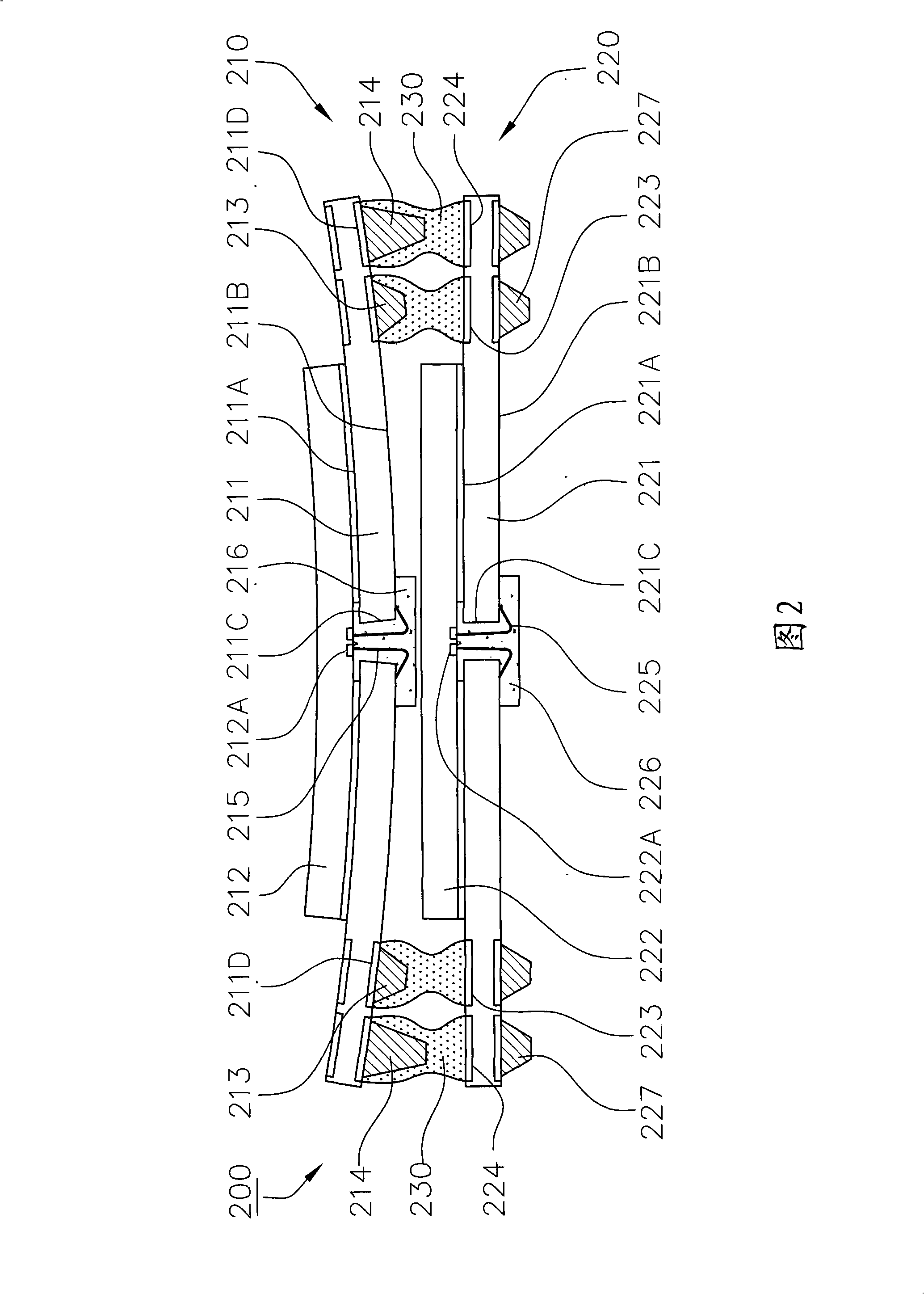

[0099] According to a first embodiment of the present invention, a semiconductor package bonding structure for avoiding soldering defects caused by substrate warpage is disclosed.

[0100] Please refer to FIG. 2 , which is a schematic cross-sectional view of a semiconductor package bonding structure according to a first embodiment of the present invention. A semiconductor package bonding structure 200 according to the first embodiment of the present invention mainly includes at least a first semiconductor package 210 , a package carrier 220 and a plurality of solders 230 . The first semiconductor package 210 is disposed on the package carrier 220 and connected and electrically connected to the package carrier 220 by the solders 230 .

[0101] The aforementioned first semiconductor package 210 includes a first substrate 211 , a first chip 212 , a plurality of first external terminals 213 and a plurality of second external terminals 214 .

[0102] The first substrate 211 is use...

no. 3 Embodiment

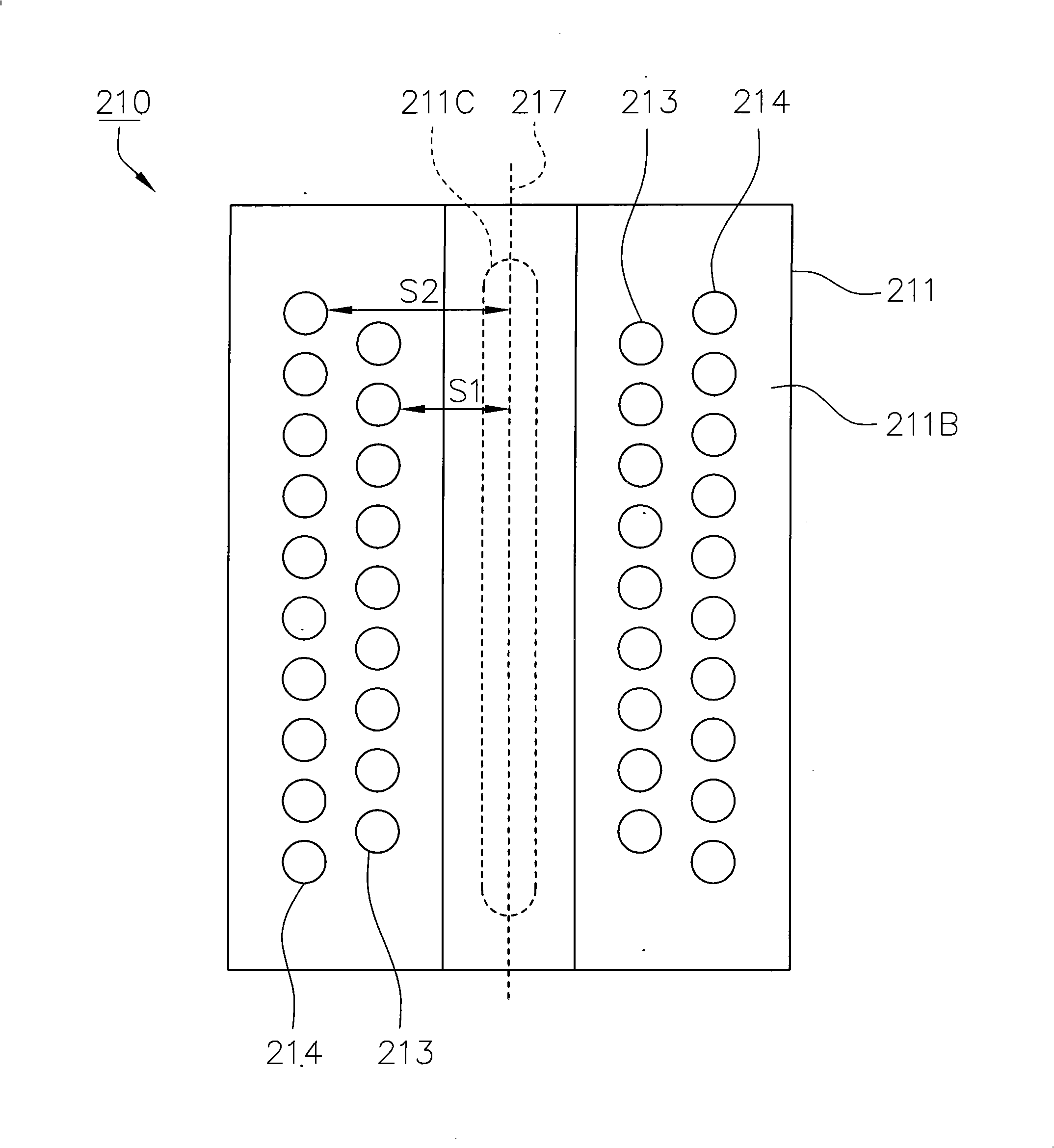

[0116]Please refer to FIG. 5 , which is a schematic cross-sectional view of a semiconductor package bonding structure according to a third embodiment of the present invention. A semiconductor package bonding structure according to the third embodiment of the present invention mainly includes at least one semiconductor package 210, a package carrier 320 and a plurality of solders 330, wherein the semiconductor package 210 is the same as the first embodiment of the first embodiment. The semiconductor packages 210 are substantially the same, so they are labeled with the same reference numerals.

[0117] The aforementioned semiconductor package 210 includes a substrate 211, a chip 212, a plurality of first external terminals 213 and a plurality of second external terminals 214; wherein:

[0118] The first external terminals 213 and the second external terminals 214 are disposed on the lower surface 211B of the substrate 211 . Moreover, the distance from the first external termina...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More