Chip-embedded package structure and manufacturing method thereof

A manufacturing method and packaging structure technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as unsatisfactory use requirements, poor reliability, and low yield rate of finished products, so as to facilitate mass production , the effect of counteracting uneven stress distribution and easy processing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

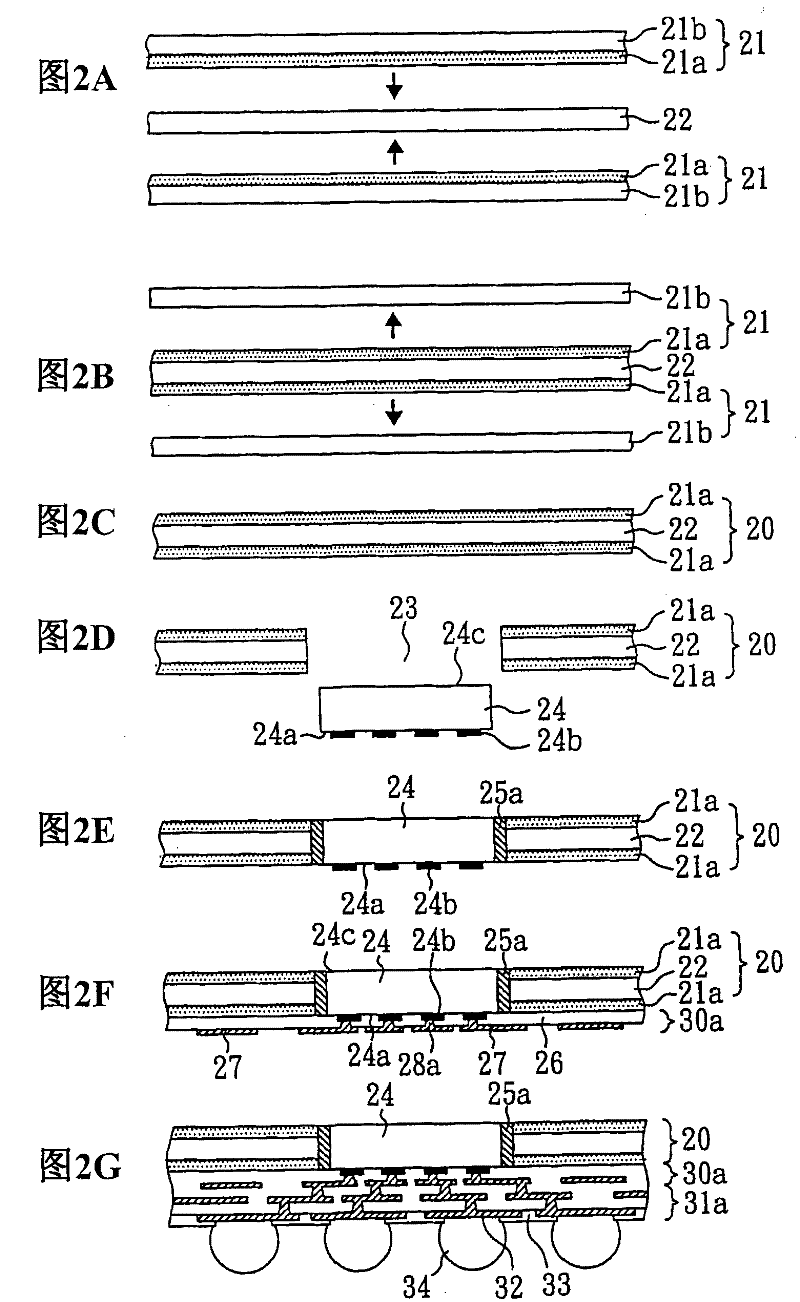

[0046] See Figure 2A to 2E , Which is a schematic cross-sectional view of the manufacturing method of the chip-embedded package structure of this embodiment.

[0047] Such as Figure 2A As shown, first, two aluminum carrier plates 21 are provided. The two aluminum carrier plates 21 can be placed in an electrolytic cell to perform anodization reaction to oxidize a surface of the aluminum carrier plate 21 to form a metal oxide layer, that is, an aluminum oxide layer 21a is formed, and the other aluminum carrier plate One part is an aluminum layer 21b. The anodizing reaction in this embodiment controls the thickness of the aluminum oxide layer by adjusting the anodizing time. Then, like Figure 2B As shown, the aluminum oxide layers 21a of the two aluminum carrier plates 21 are facing each other, and an adhesive layer 22 is sandwiched between them to make them tightly adhered. The material of the adhesive layer 22 can be thermosetting resin, and this embodiment Use epoxy resin. ...

Embodiment 2

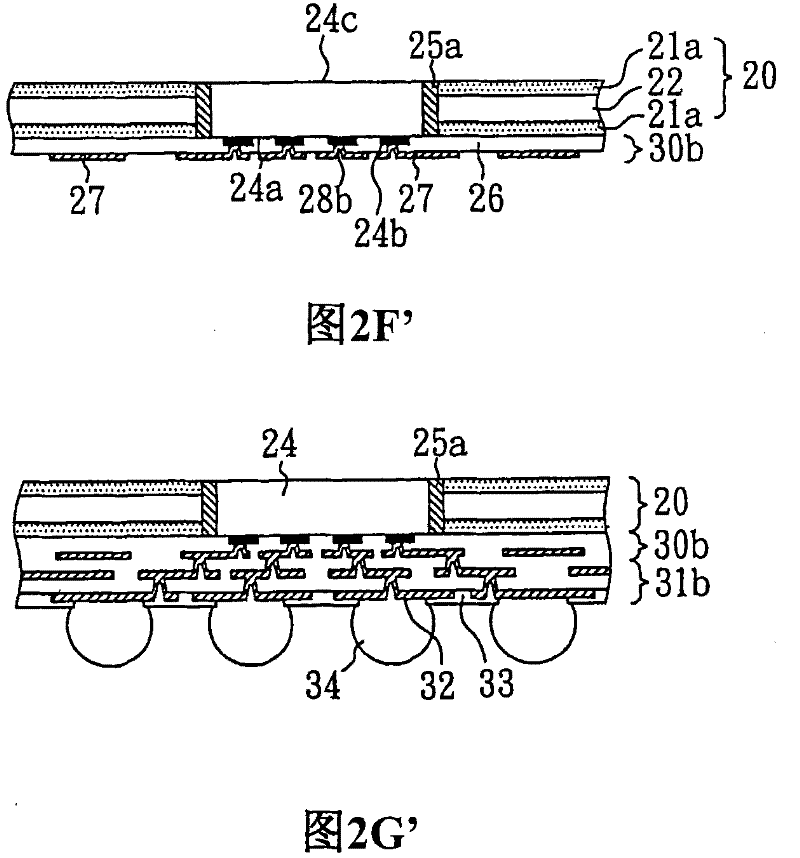

[0055] The manufacturing method of the package structure with embedded chips in this embodiment is substantially the same as that in Embodiment 1, except that the method of fixing the chip 24 to the alumina composite board is different, and the rest are the same as in Embodiment 1.

[0056] Such as image 3 As shown, the method of fixing the chip 24 to the alumina composite board 20 in this embodiment is as follows: image 3 As shown, when the chip 24 is embedded in the alumina composite board 20, epoxy resin is not used first, but when the dielectric layer 26 is laminated, the dielectric layer 26 (ie, ABF) is filled at the same time The gap between the chip 24 and the composite board opening 23 formed by the alumina composite board 20 uses the dielectric layer 26 as an adhesive material. The remaining steps are the same as in Example 1. Finally, a package structure with embedded chips of the present invention is obtained.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More