Wafer

A chip and substrate technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve problems such as difficult to print identification codes, misidentification of reading identification codes, and problems with productivity, so as to increase production quantity and expand devices area, the effect of accurate identification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

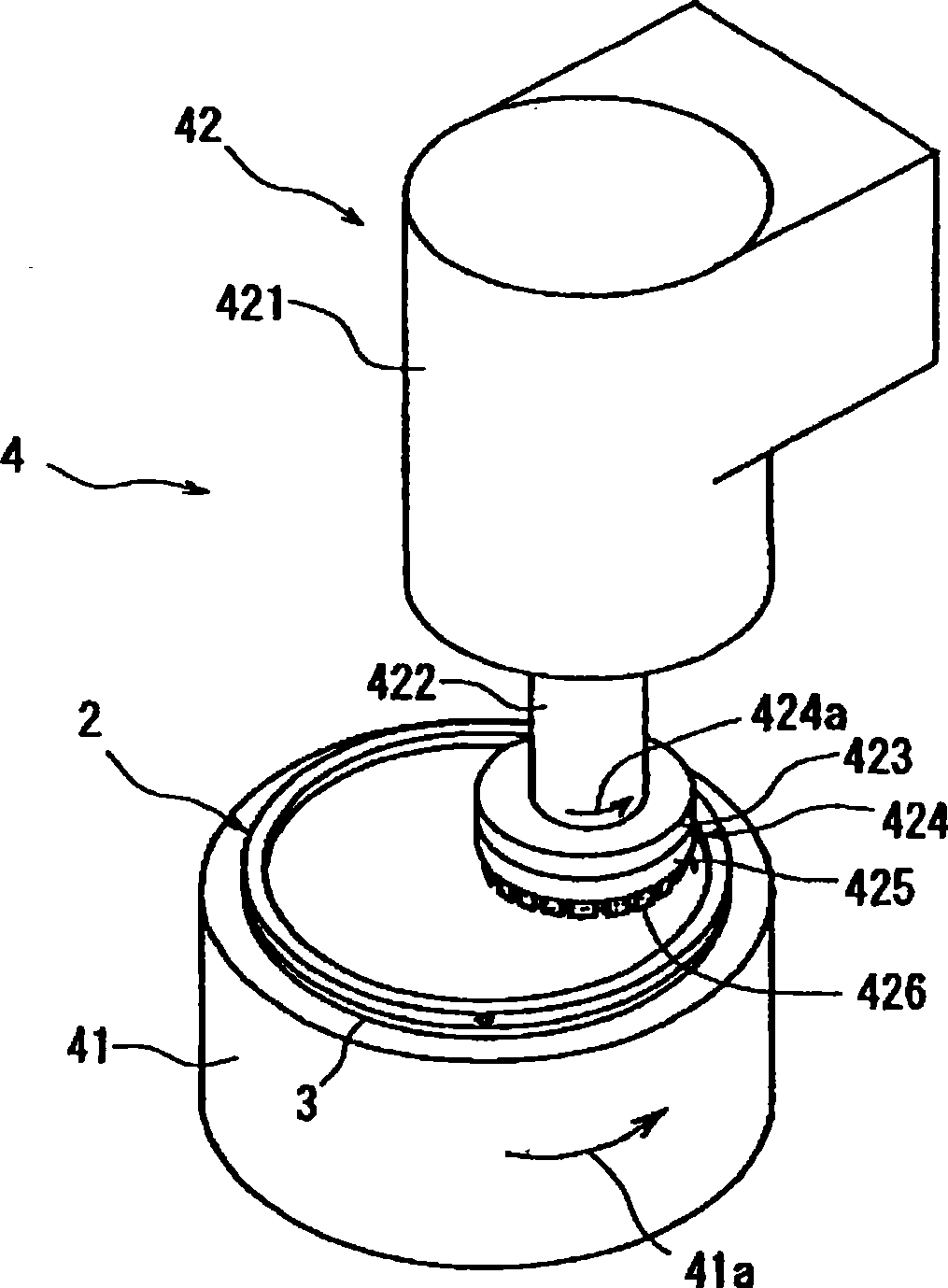

[0026] Hereinafter, preferred embodiments of a wafer constructed according to the present invention will be described in detail with reference to the accompanying drawings.

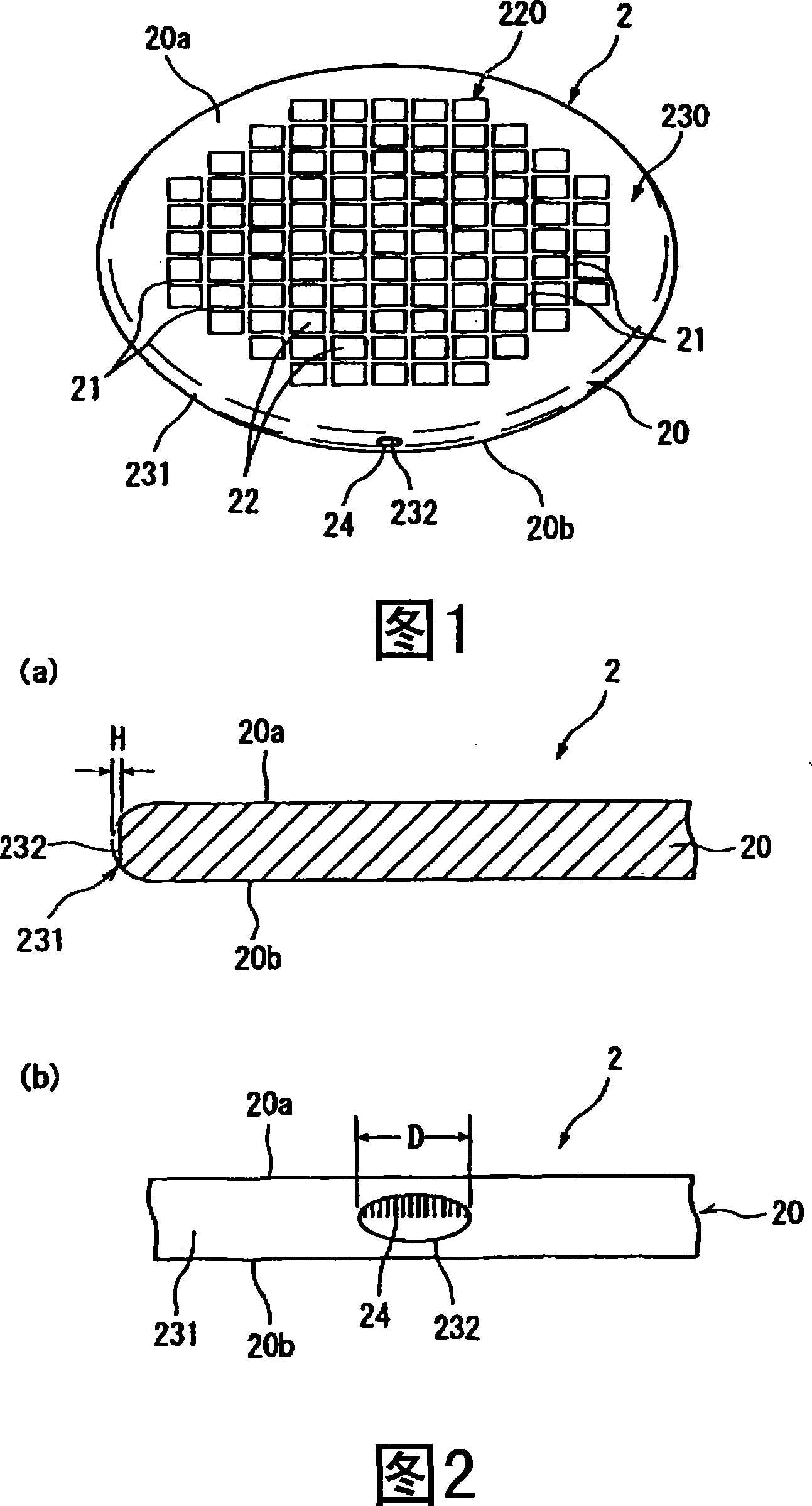

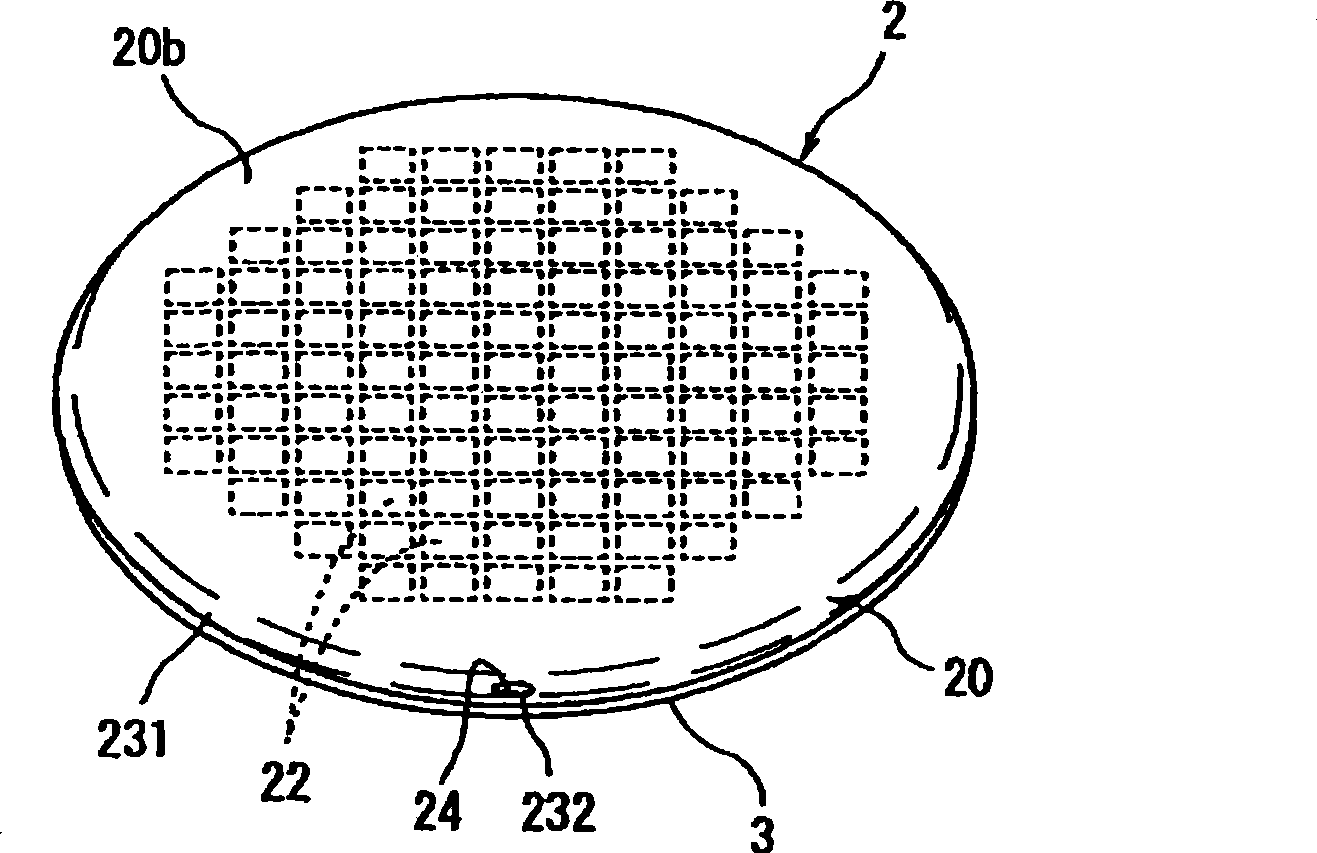

[0027] FIG. 1 shows a perspective view of a semiconductor wafer as a wafer constructed according to the present invention. In the semiconductor wafer 2 shown in FIG. 1 , on the surface 20a of a wafer substrate 20 made of, for example, silicon with a thickness of 700 μm, a plurality of blank channels 21 are arranged in a grid pattern, and at the same time, when divided by the multiple blank channels 21 Devices 22 such as ICs and LSIs are formed in a plurality of regions. The wafer substrate 20 thus formed has a device region 220 where a plurality of devices 22 are formed and a peripheral remaining region 230 surrounding the device region 220 . In addition, in order to prevent cracks and breakage due to inadvertently received impacts, as shown in FIG. 20b forms a chamfer 231 whose cross-sectional shape is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More