Clock generator based on phase-locked loop and clock generating method

A clock generator, phase-locked loop technology, applied in the direction of signal generation/distribution, automatic power control, electrical components, etc., can solve the problem of non-coverage, maximum frequency oscillation frequency limit, phase adjustment digital multiplexer accuracy limit, etc. problem, to achieve the effect of convenient adjustment and convenient phase

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

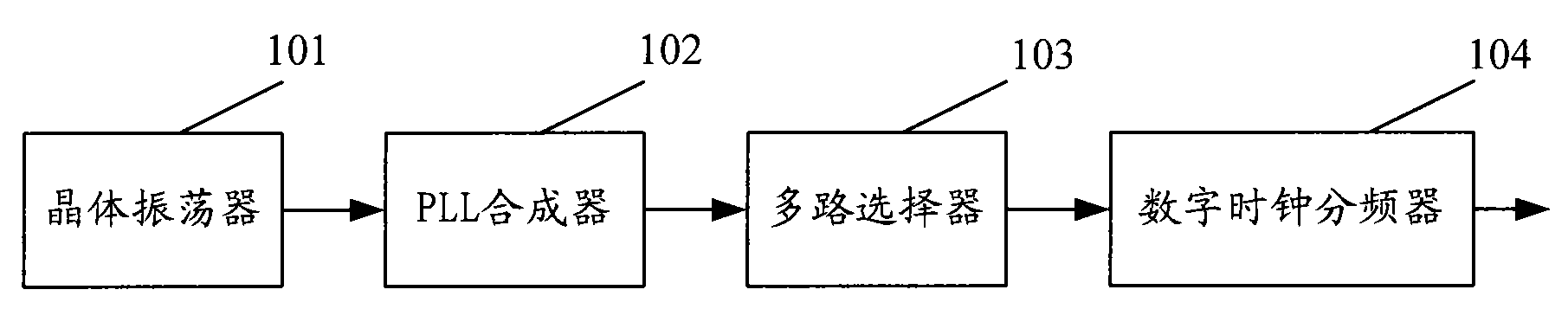

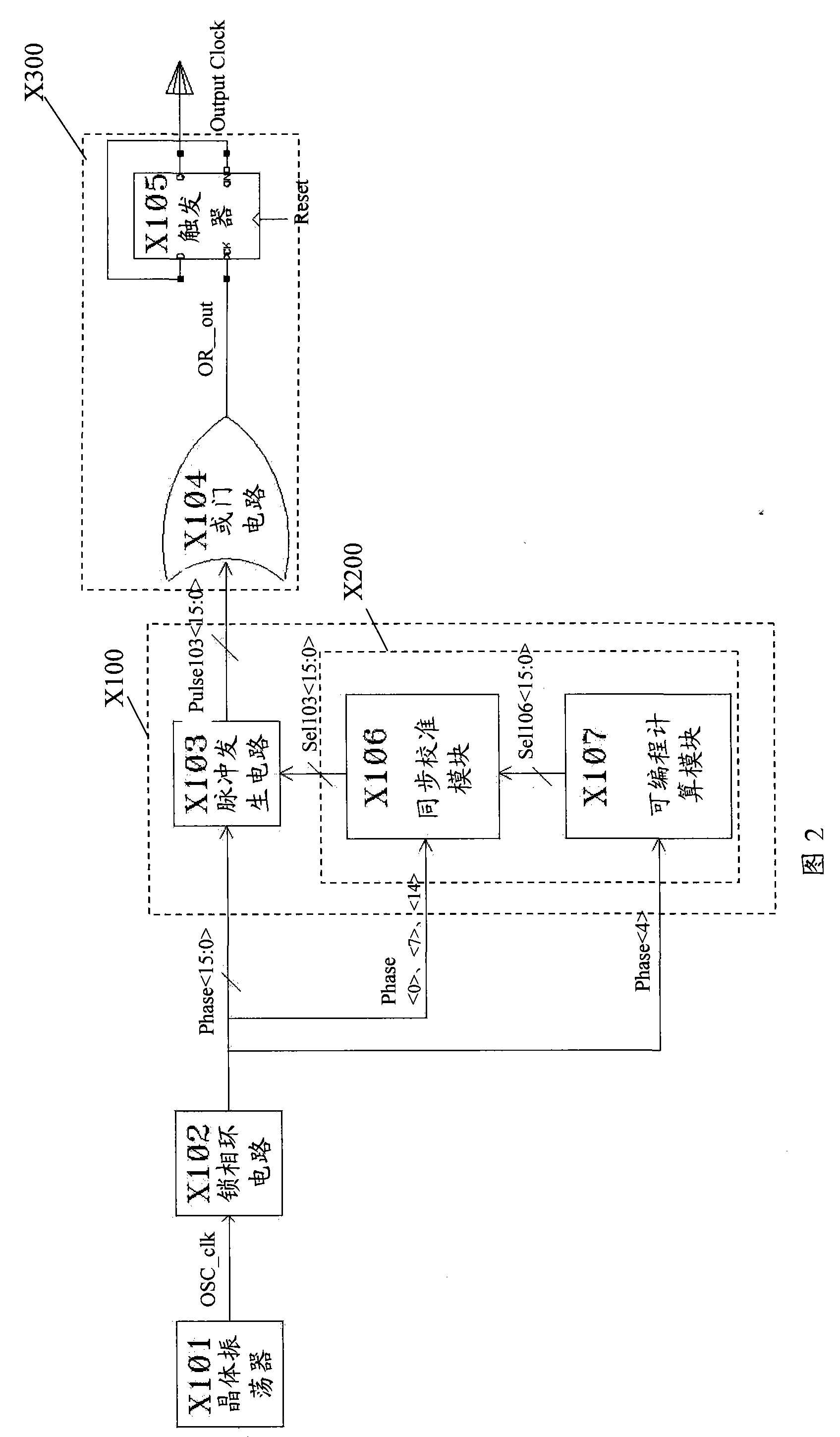

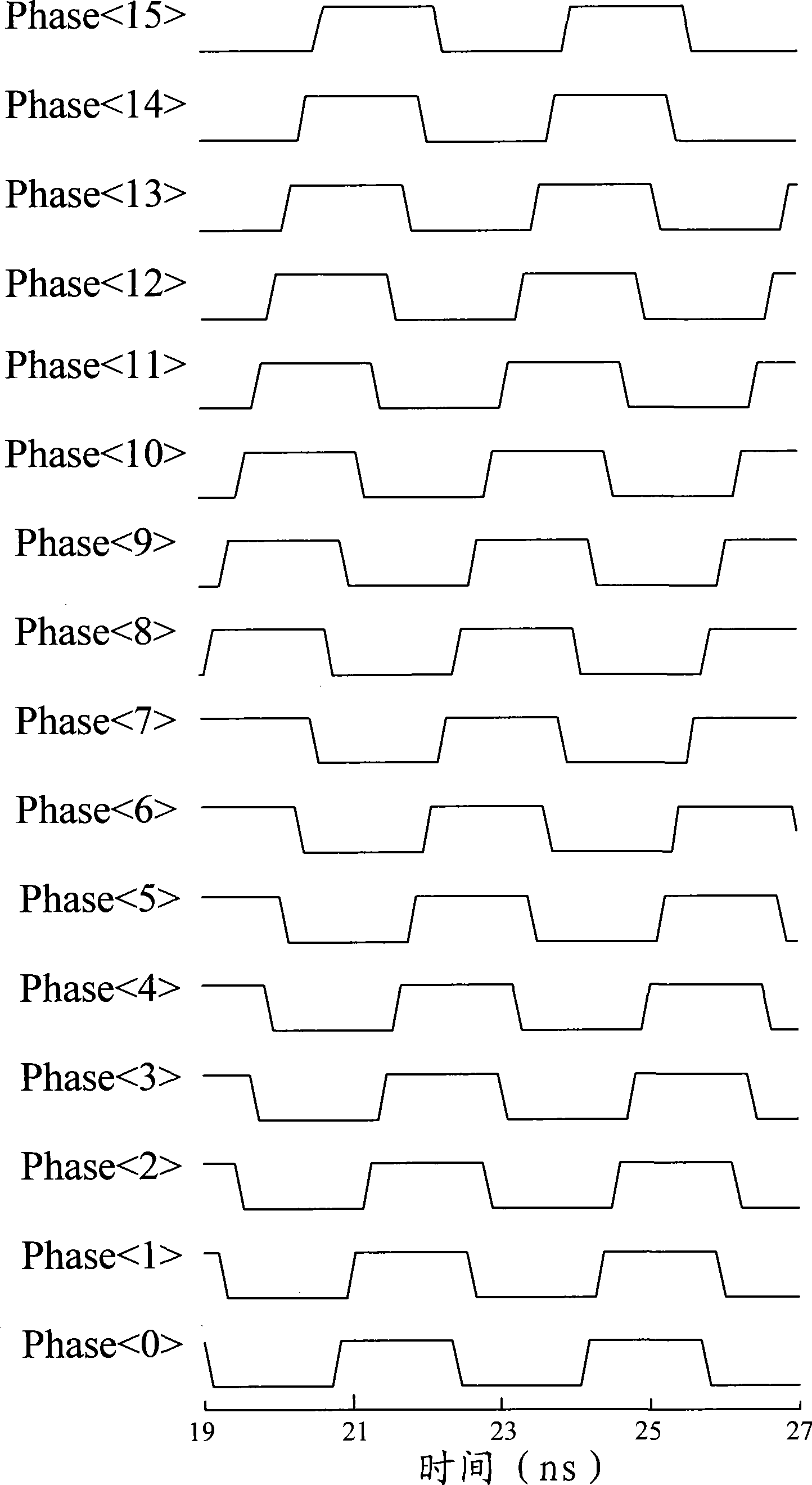

[0059] The first embodiment of the present invention details a clock generator based on a phase-locked loop. 2 is a schematic diagram of a clock generator based on a phase-locked loop in the first embodiment of the present invention, Figure 3 to Figure 10 It is the timing diagram inside the clock generator based on the phase-locked loop in the first embodiment of the present invention, below in conjunction with Fig. 2 to Figure 10 The first embodiment of the present invention will be described in detail.

[0060] As shown in Figure 2, the clock generator based on the phase-locked loop in the present embodiment includes: a crystal oscillator X101, which is used to output an initial clock signal (OSC_clk); a phase-locked loop circuit X102, which is used to receive the crystal oscillator The initial clock signal (OSC_clk) output by X101 outputs a plurality of first multi-channel clock signals with different phases (in this embodiment, 16 first multi-channel clock signals with ...

no. 2 example

[0120] The second embodiment of the present invention proposes a phase-locked loop-based clock generation method that can be realized by using the clock generator in the first embodiment of the present invention, Figure 11 It is a flowchart of a clock generation method based on a phase-locked loop in the second embodiment of the present invention, combined below Figure 11 and Figure 2 to Figure 10 The clock generation method based on the phase-locked loop in the second embodiment of the present invention is introduced in detail.

[0121] Step 1101: Output an initial clock signal by using a crystal oscillator.

[0122] An initial clock signal (OSC_clk) having a certain fixed frequency is generated by the crystal oscillator X101.

[0123] Step 1102: Using a phase-locked loop circuit to complexize the initial clock signal output by the crystal oscillator, and output a plurality of first multi-channel clock signals with different phases.

[0124] The initial clo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More