High precision time difference calibrating method based on FPGA

A calibration method and high-precision technology, applied in the direction of clock driven by synchronous motor, electronic timer, automatic power control, etc., can solve the problem of not giving detailed time difference processing algorithm, no algorithm implementation scheme and design introduction, implementation scheme There are no problems with the introduction and the algorithm, which achieves the effects of fast synchronization between satellites, reduced injection frequency, and strong real-time performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] Below in conjunction with accompanying drawing and specific embodiment the present invention is described in further detail:

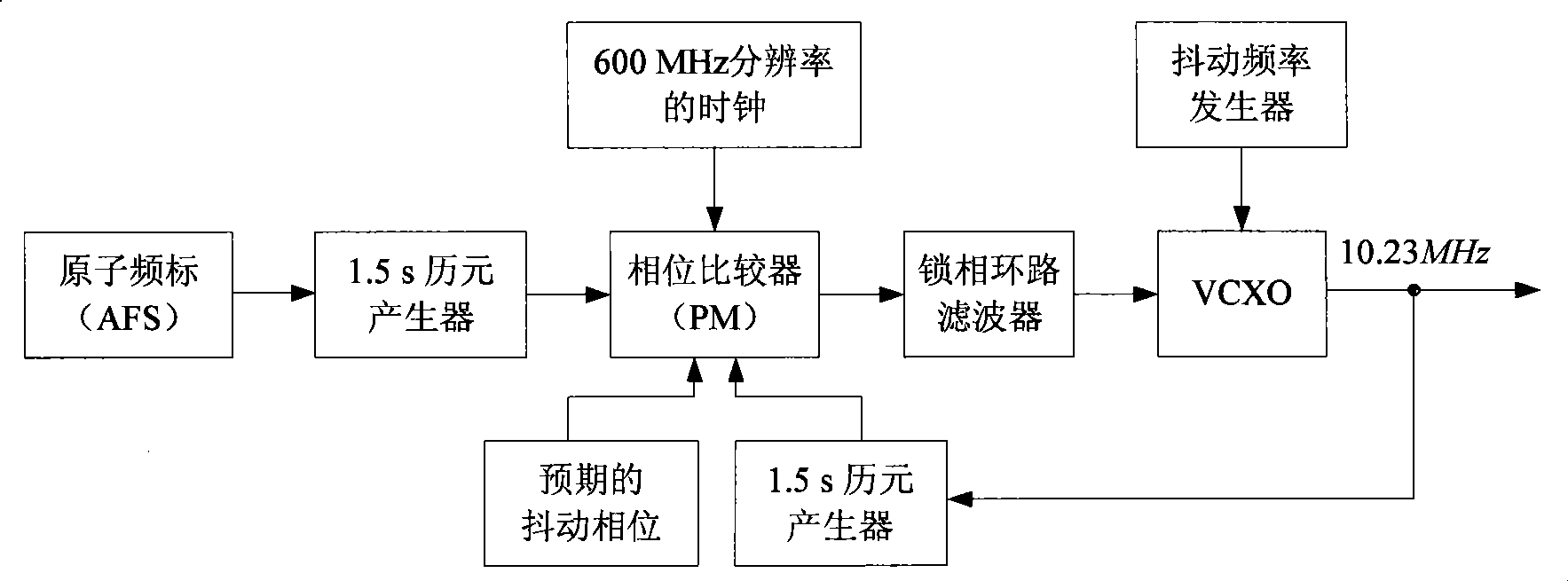

[0032] The FPGA externally inputs a working clock, and another device has a clock with a different source and the FPGA working clock, there is a time difference Δt between them, and this time difference needs to be adjusted under certain application conditions. The present invention adopts the main processing chip based on FPGA The hardware platform can calibrate this time difference by using a high-precision time difference calibration method based on FPGA.

[0033] Here we first explain several concepts and the method of judging the validity of time difference.

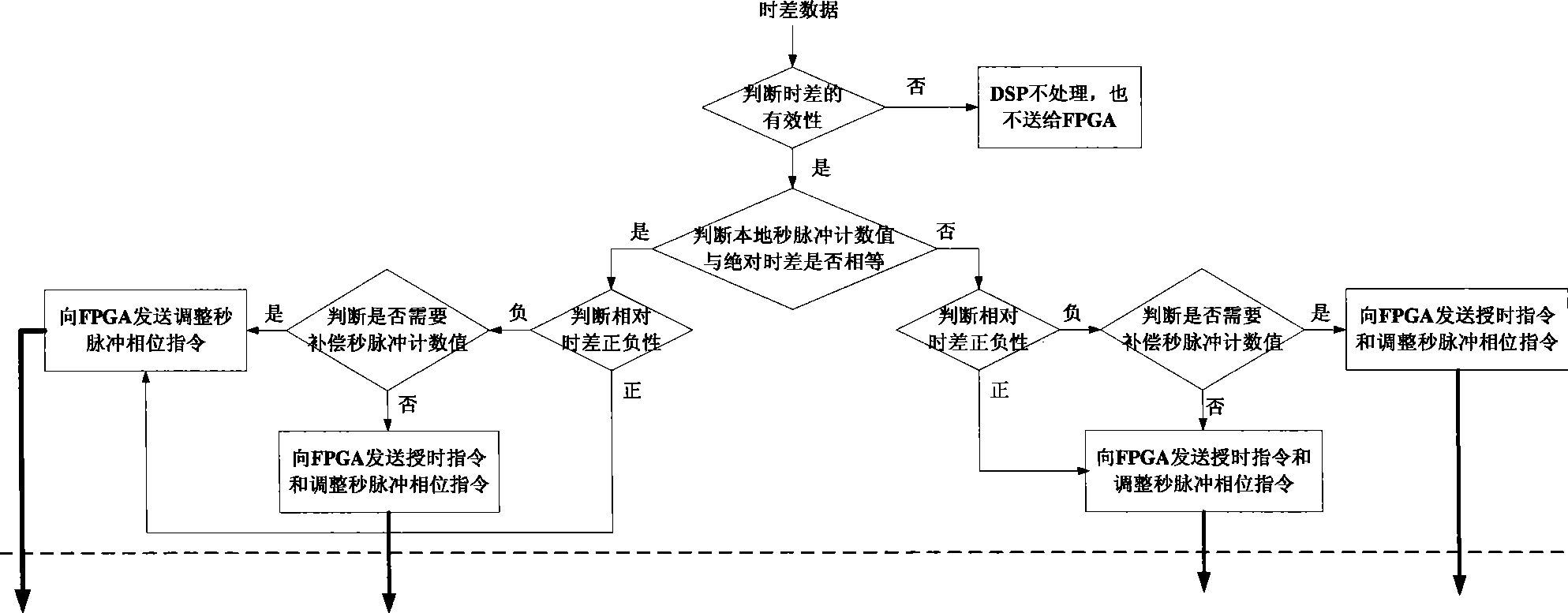

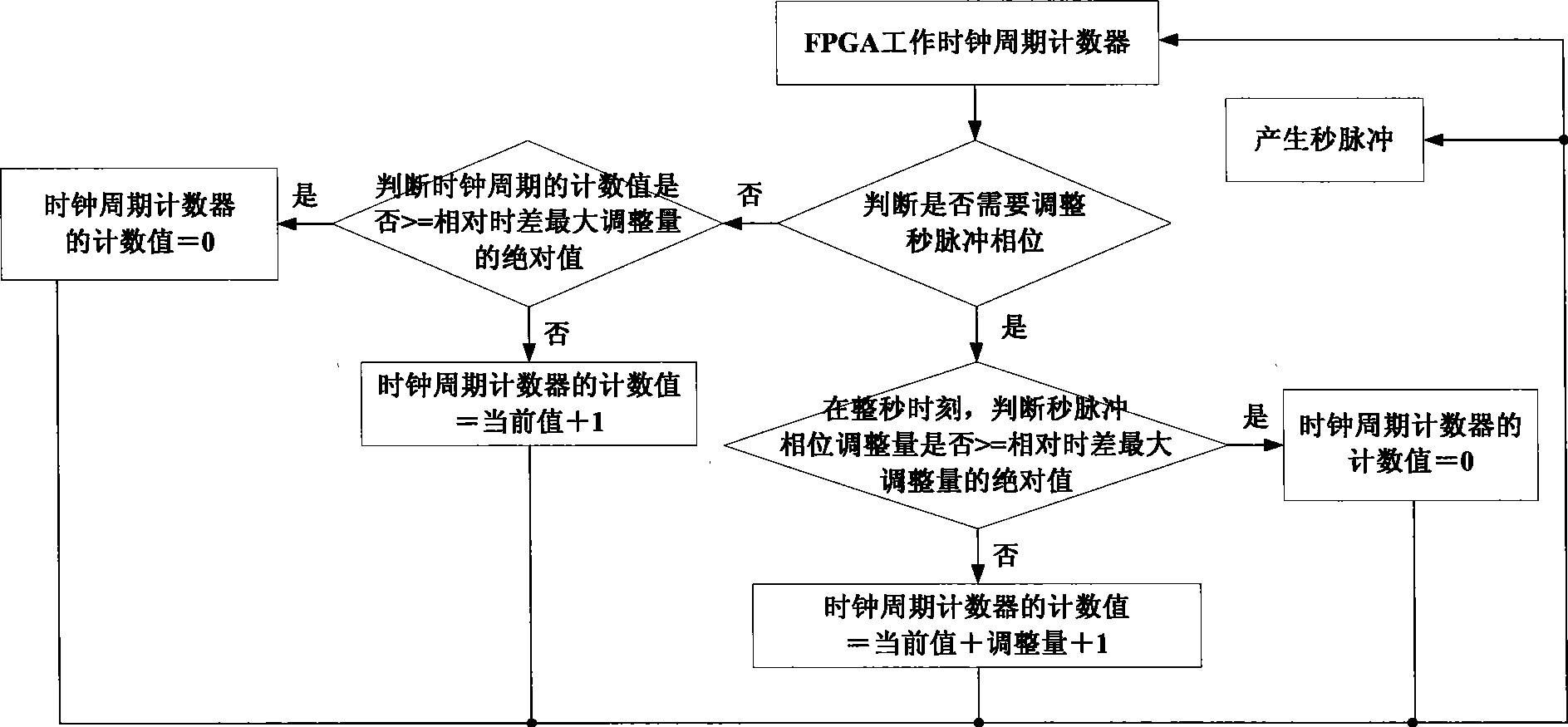

[0034] Time difference Δt: refers to the difference between the local time and the reference time Δt=ΔTs+ΔTp, including the absolute time difference ΔTs and the relative time difference ΔTp, the absolute time difference ΔTs refers to the count value of the second pulse, and the relati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More