Circuit for buffering having a coupler

A buffer circuit and coupler technology, applied in logic circuits, logic circuit coupling/interfaces using field effect transistors, DC coupled DC amplifiers, etc., can solve the problem of slowing down the working speed of the buffering circuit and achieve the goal of improving the working speed Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] Hereinafter, specific embodiments of the present invention will be described in detail with reference to the accompanying drawings.

[0026] The invention discloses a buffer circuit with a coupler for controlling a bias for differential amplification by coupling an input signal with a reference node corresponding to a reference voltage.

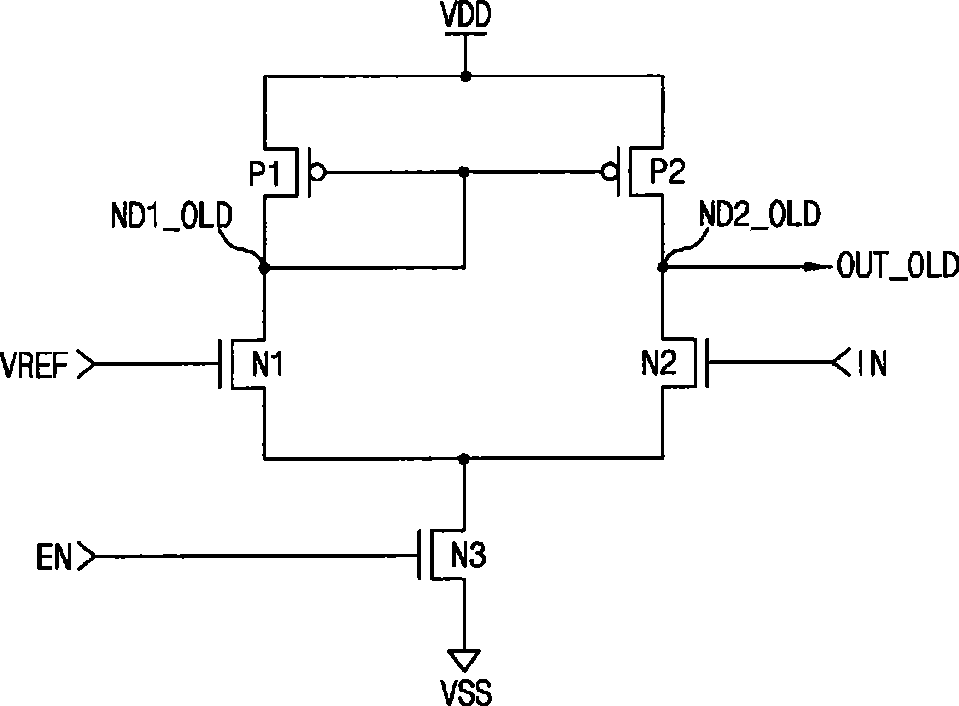

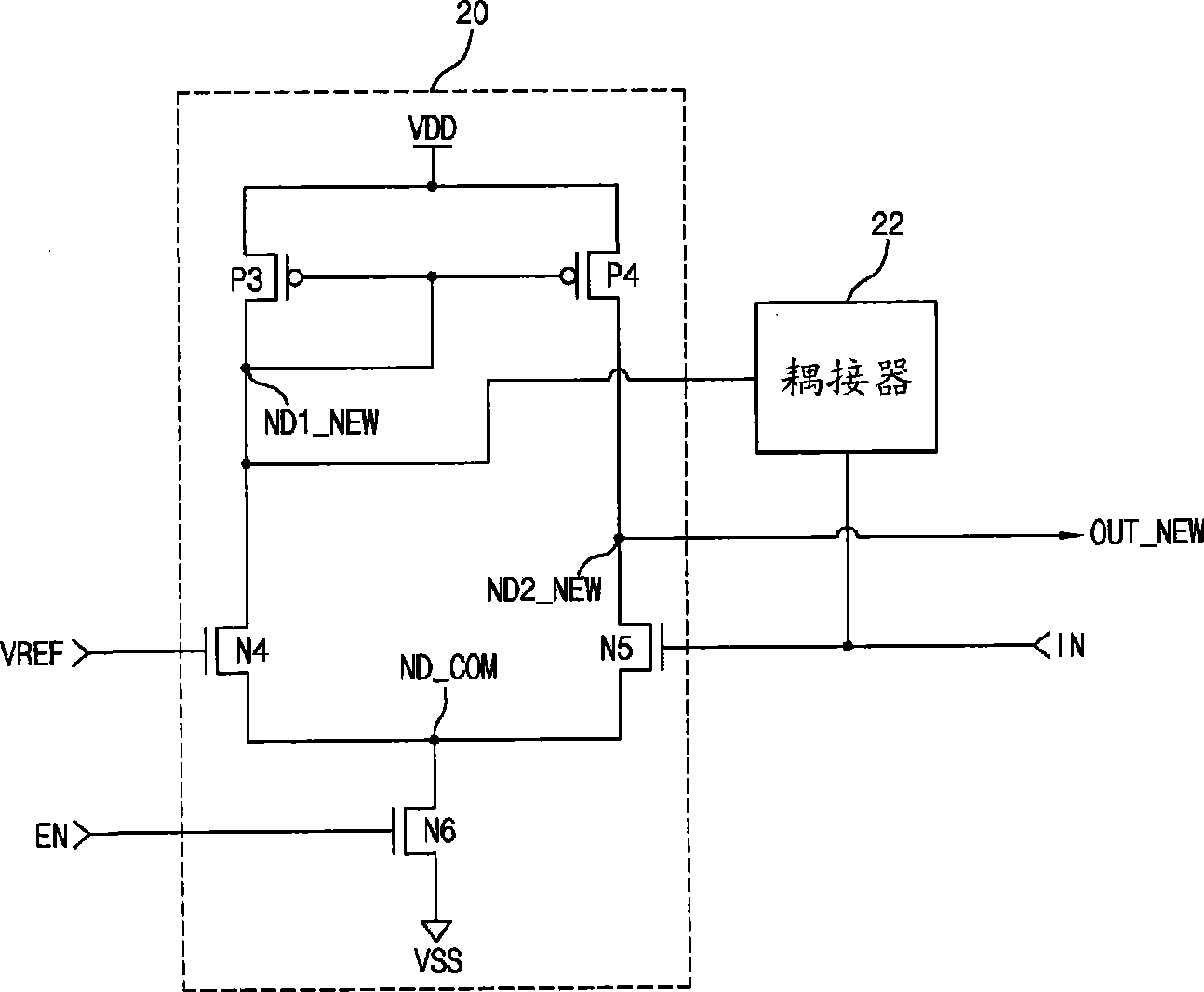

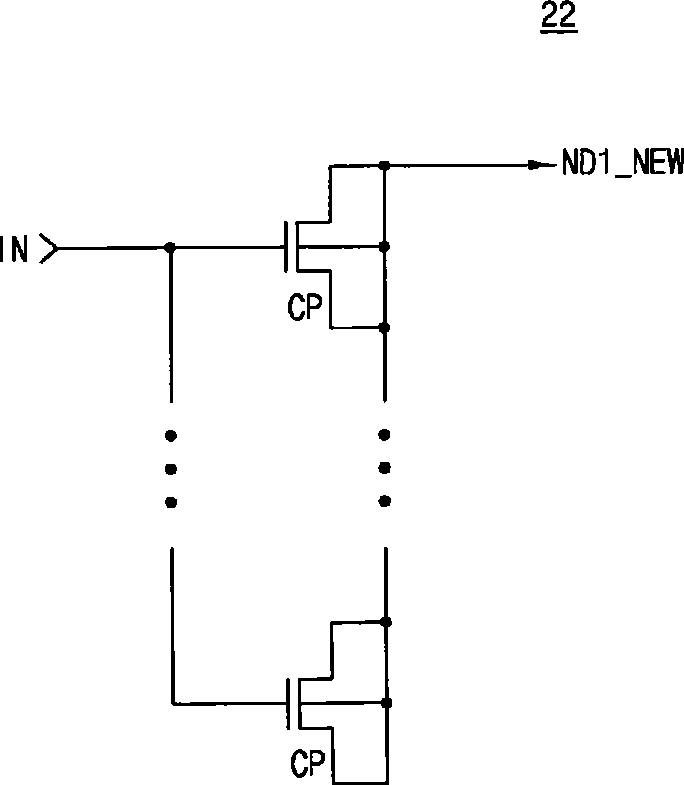

[0027] Specifically, the buffer circuit according to the present invention includes: a differential amplifier 20 for sensing and amplifying the potential difference between a reference voltage VREF and an input signal IN; and a coupler 22 for making the input signal IN and an input signal IN The reference node ND1_NEW corresponding to the reference voltage VREW is coupled, such as figure 2 shown.

[0028] The differential amplifier 20 differentially amplifies the reference node ND1_NEW and an input node ND2_NEW, and outputs an output signal OUT_NEW corresponding to the potential of the amplified input node ND2_NEW. The reference nod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More