FPGA implementing method for Turbo product code optimized encoding and decoding algorithm

An implementation method and product code technology, applied in the field of forward error correction coding and decoding, can solve the problems of cumbersome configuration, simplified algorithm, poor flexibility, etc., and achieve the effects of flexible configuration, high coding performance, and high data rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

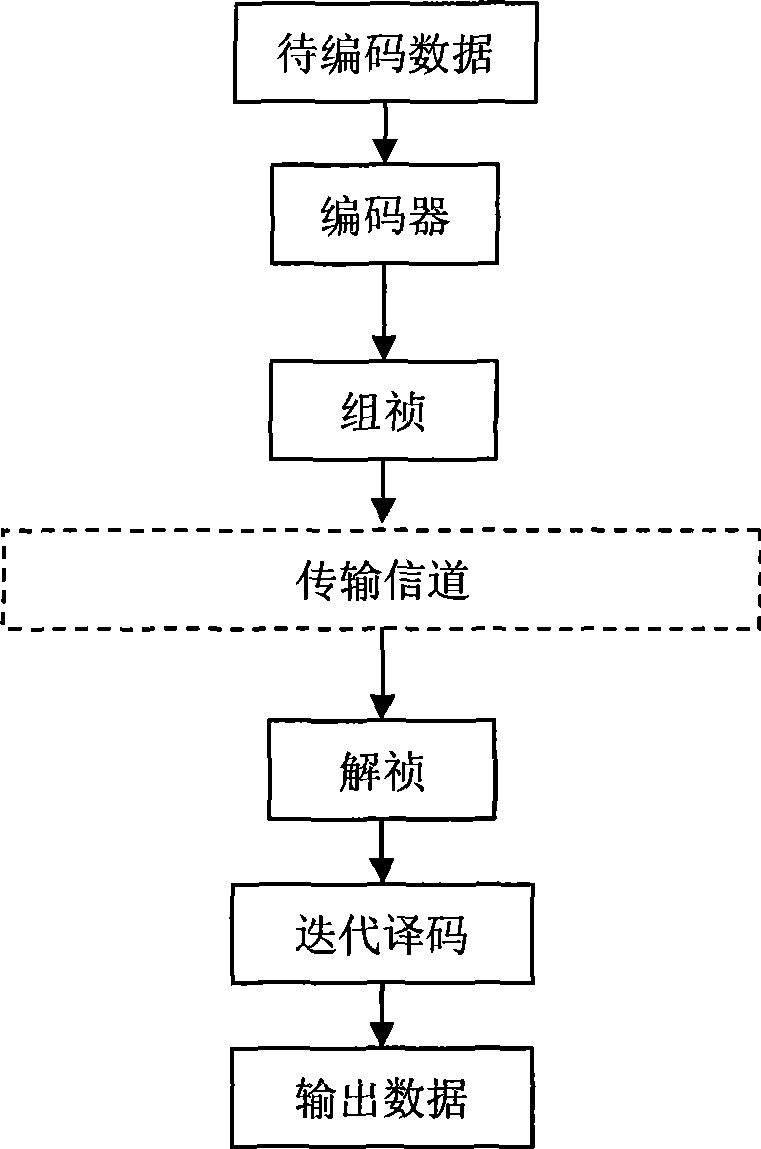

[0040] Such as figure 2 Shown, a kind of FPGA implementation method of Turbo product code optimization coding algorithm, comprises the following steps:

[0041] 1) Encoding:

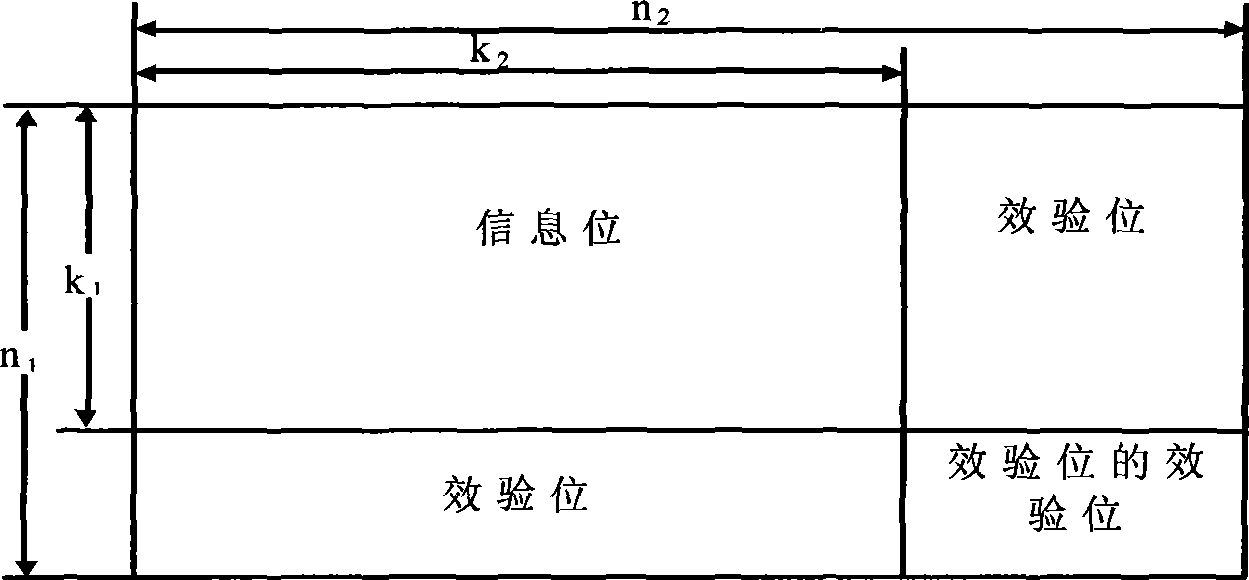

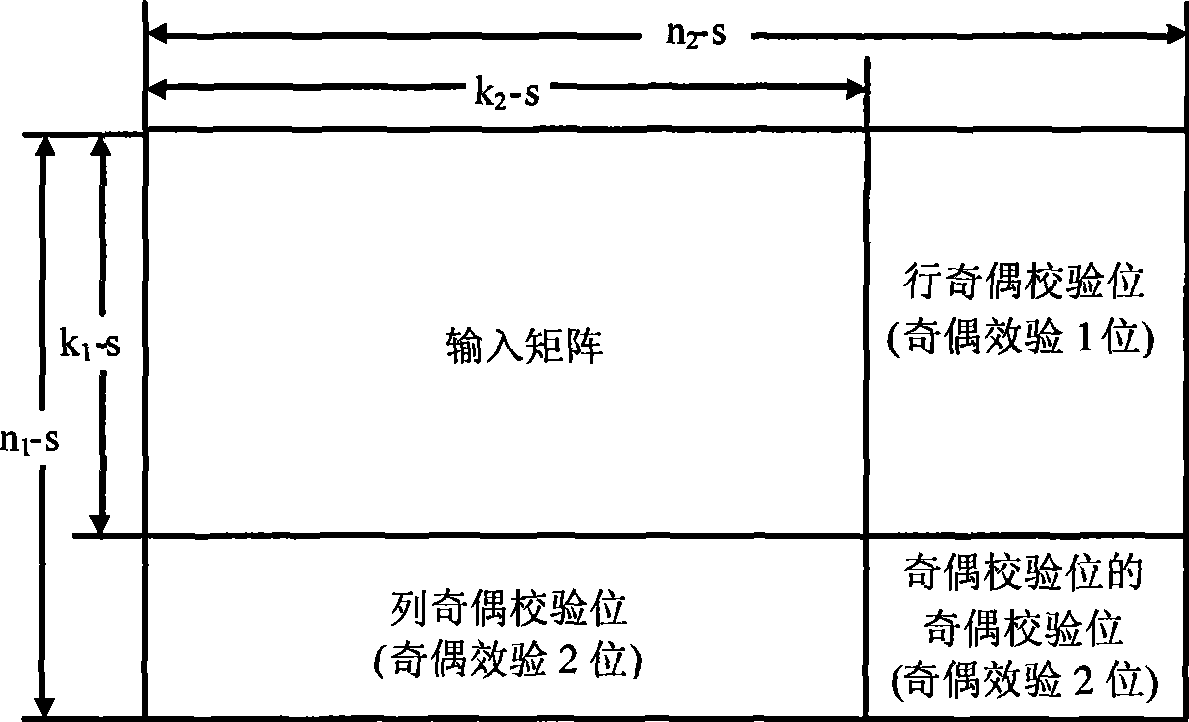

[0042] Use Ram1, Ram1 two random access memory (Random Access Memory, RAM) and output Ram, after the coded data transmission starts, the data is written into Ram1. When Ram1 is full (the length of 1 information block), start to write to Ram2 and at the same time the encoder starts to work, the encoder reads line by line from Ram1 for line encoding, writes to the output Ram, that is, writes image 3 The input matrix (inputarray) and the row parity bit (parity check 1 bit); after all the rows are encoded, they are encoded column by column and written to the output Ram, that is, written image 3The column parity bit (2 bits of parity) and the parity bit of the parity bit (2 bits of parity). After reading Ram1, that is, after reading the information of 1 information block length, wait for Ram2 to be full...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More