Patents

Literature

53 results about "Turbo product codes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

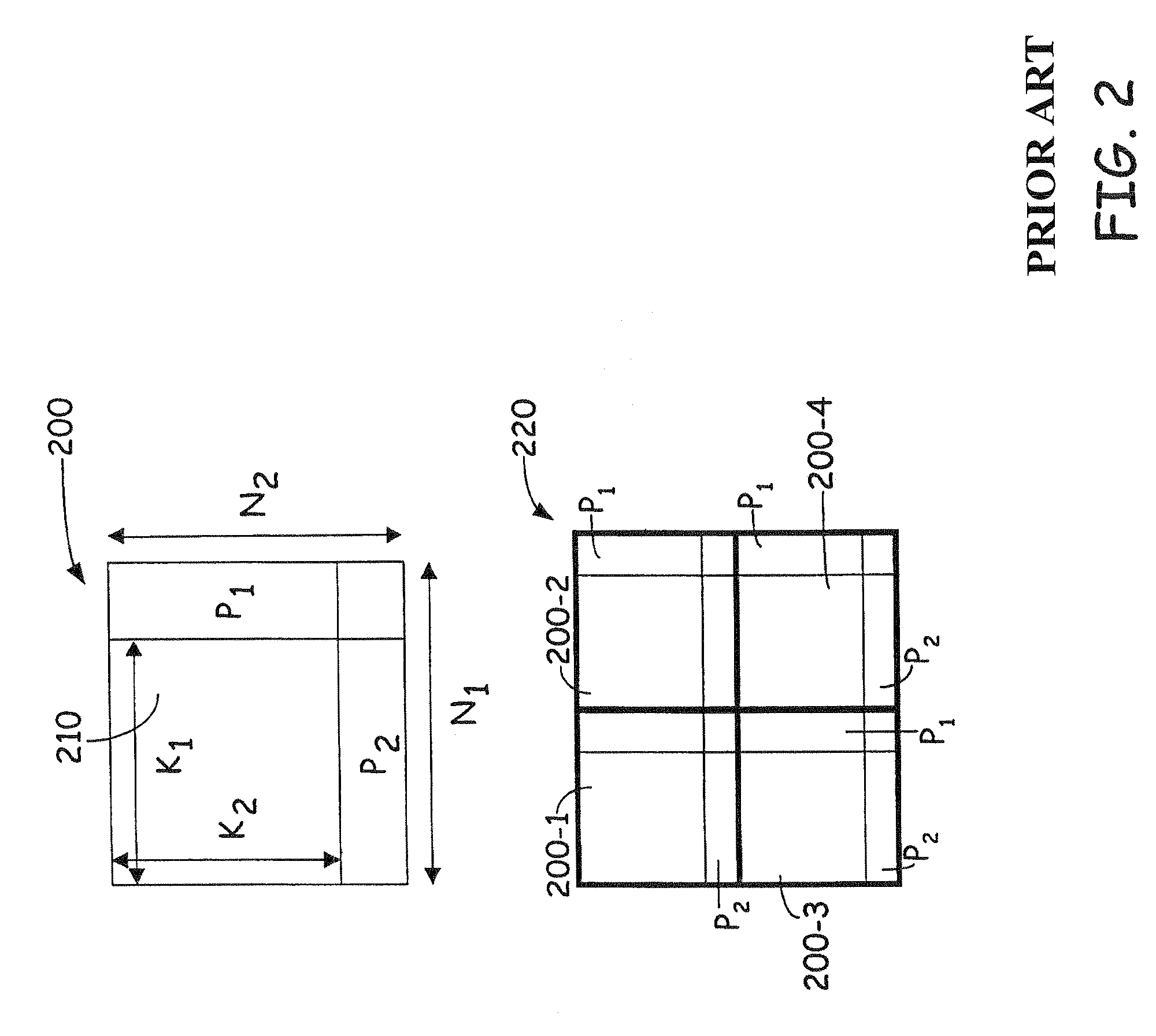

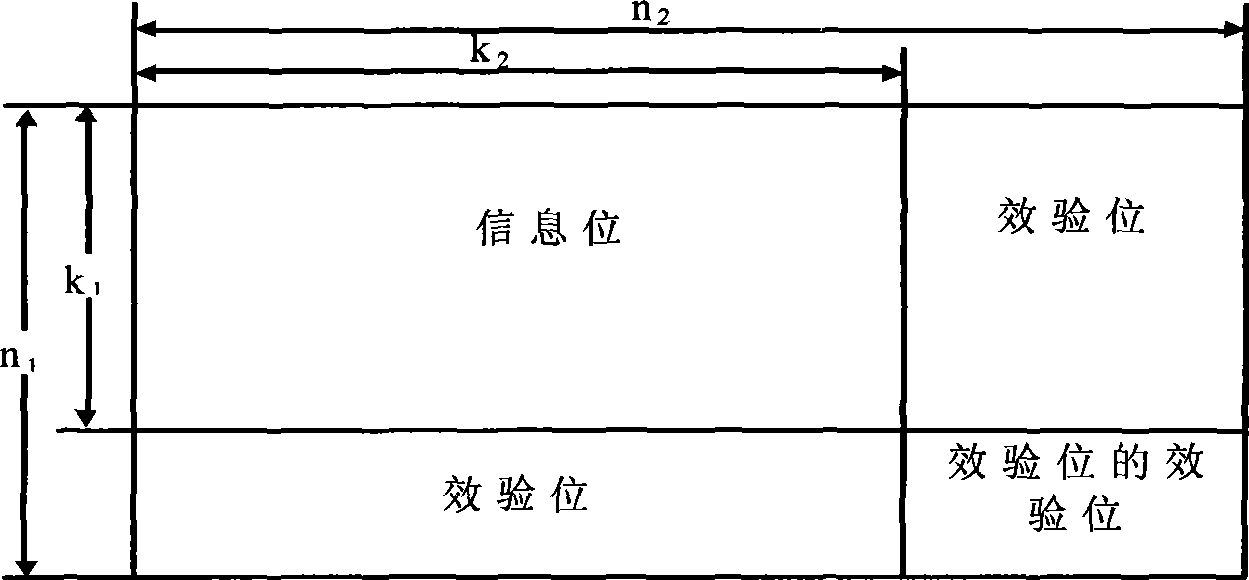

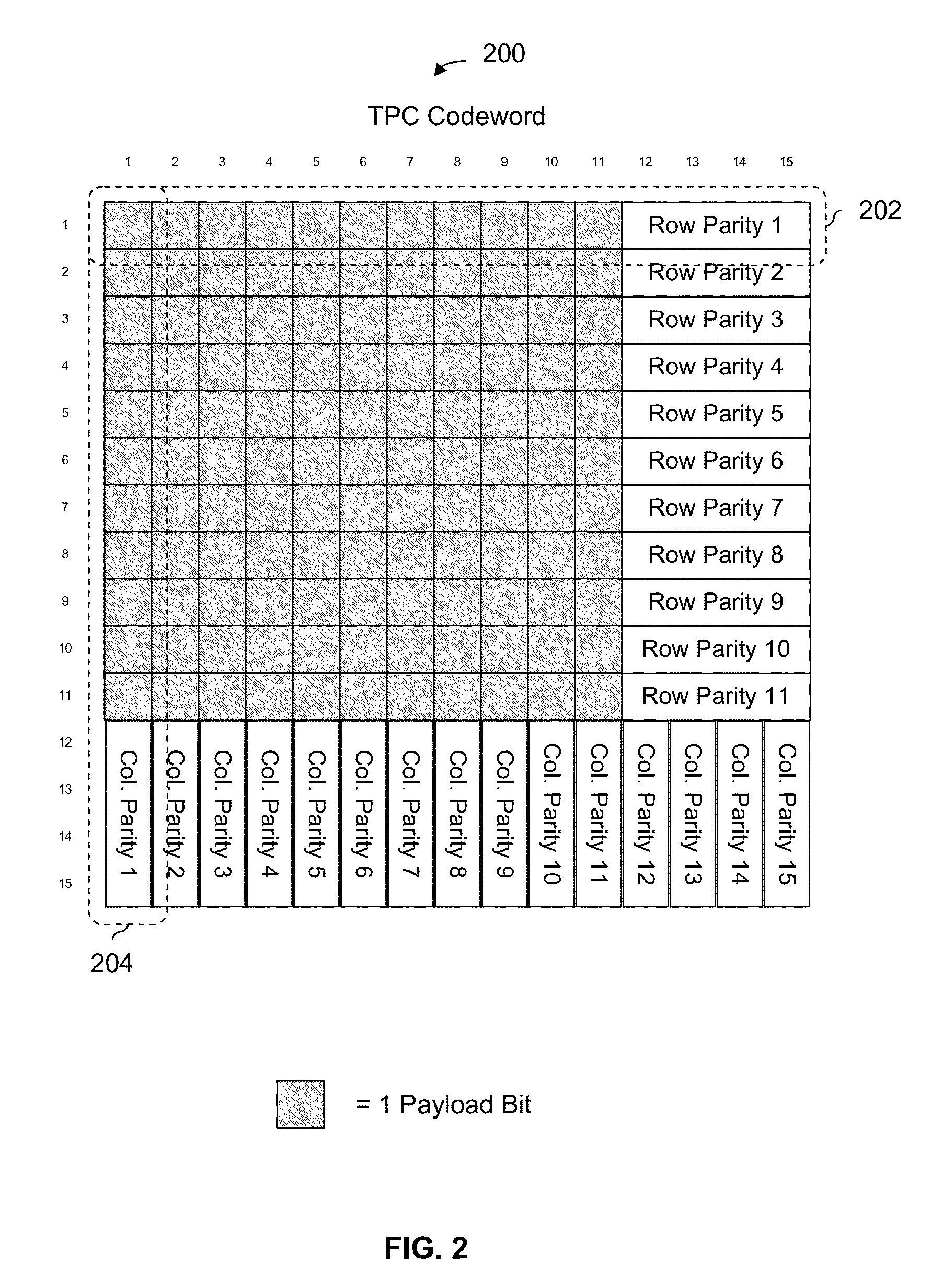

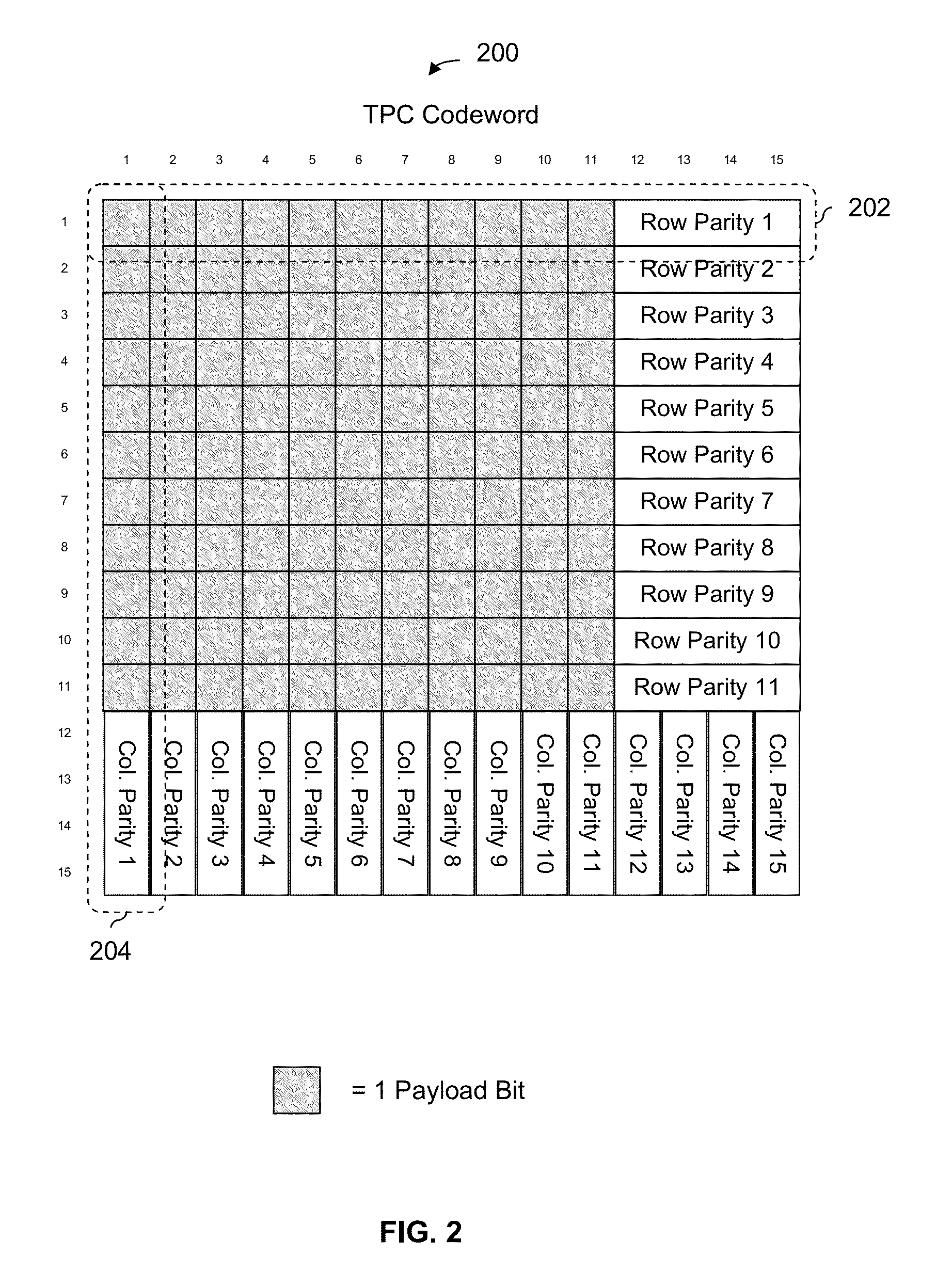

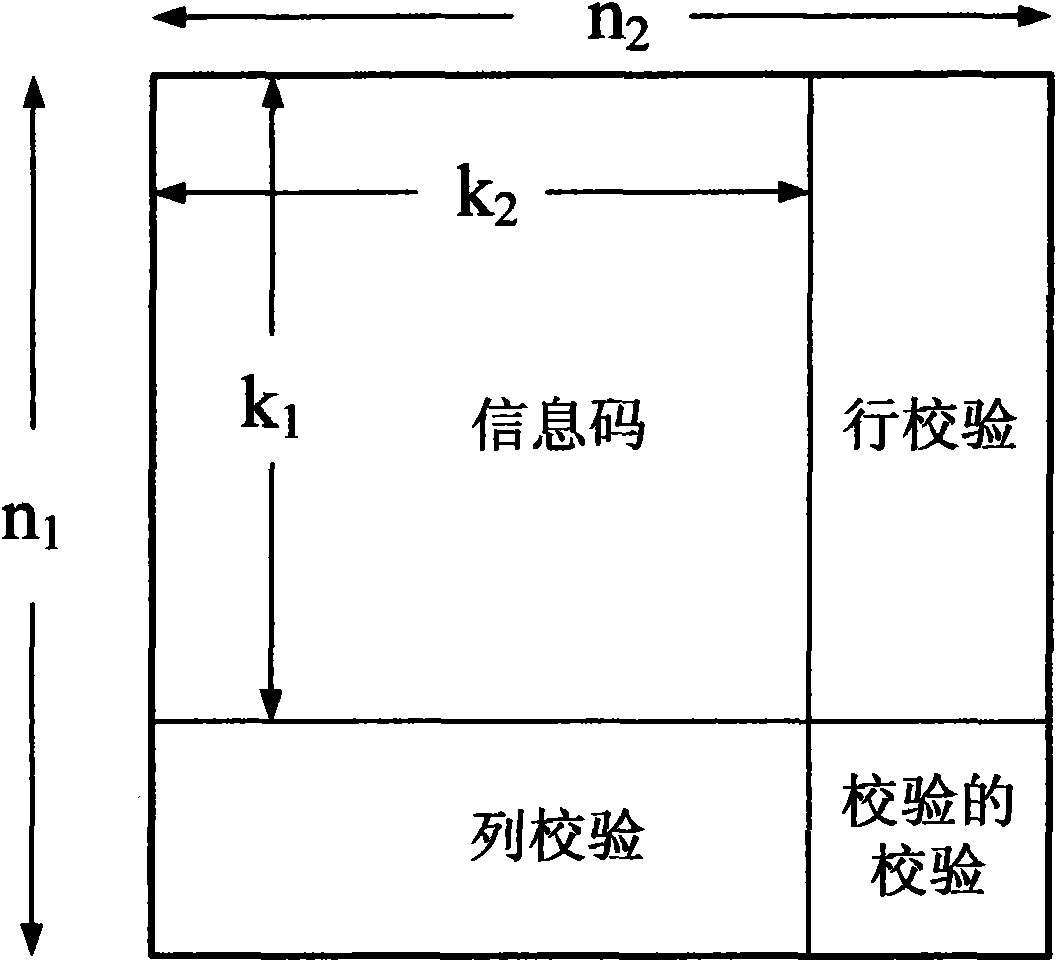

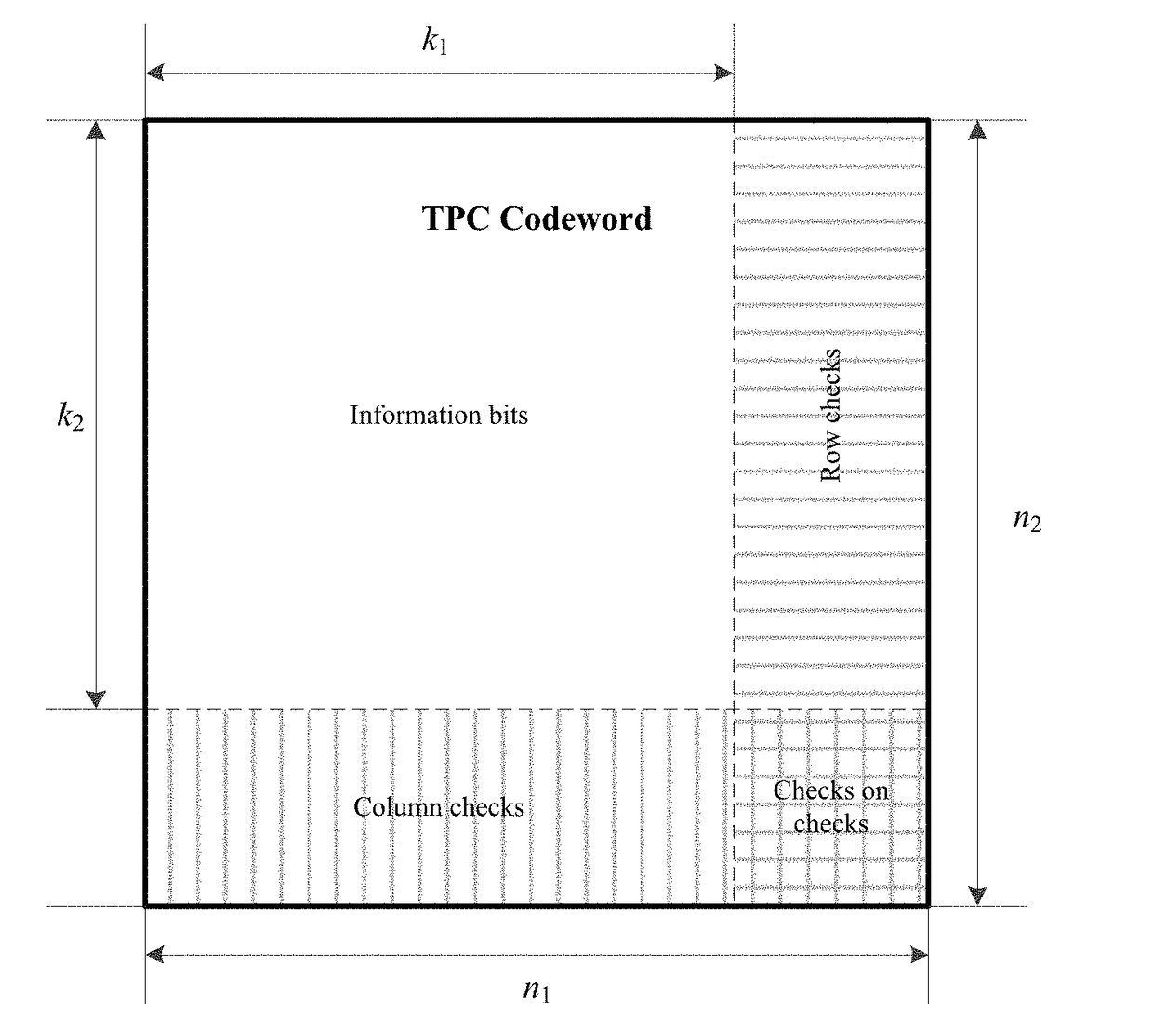

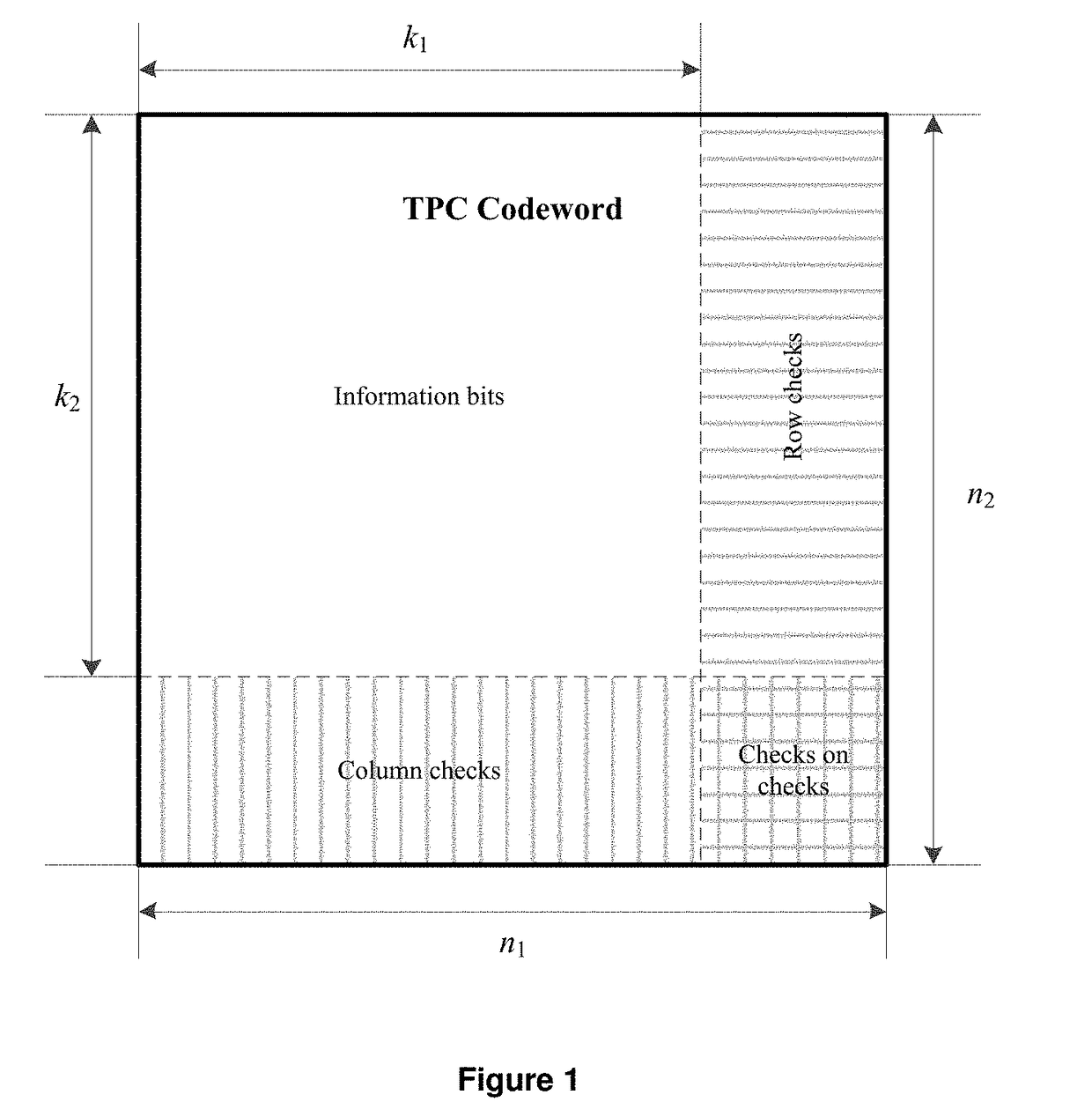

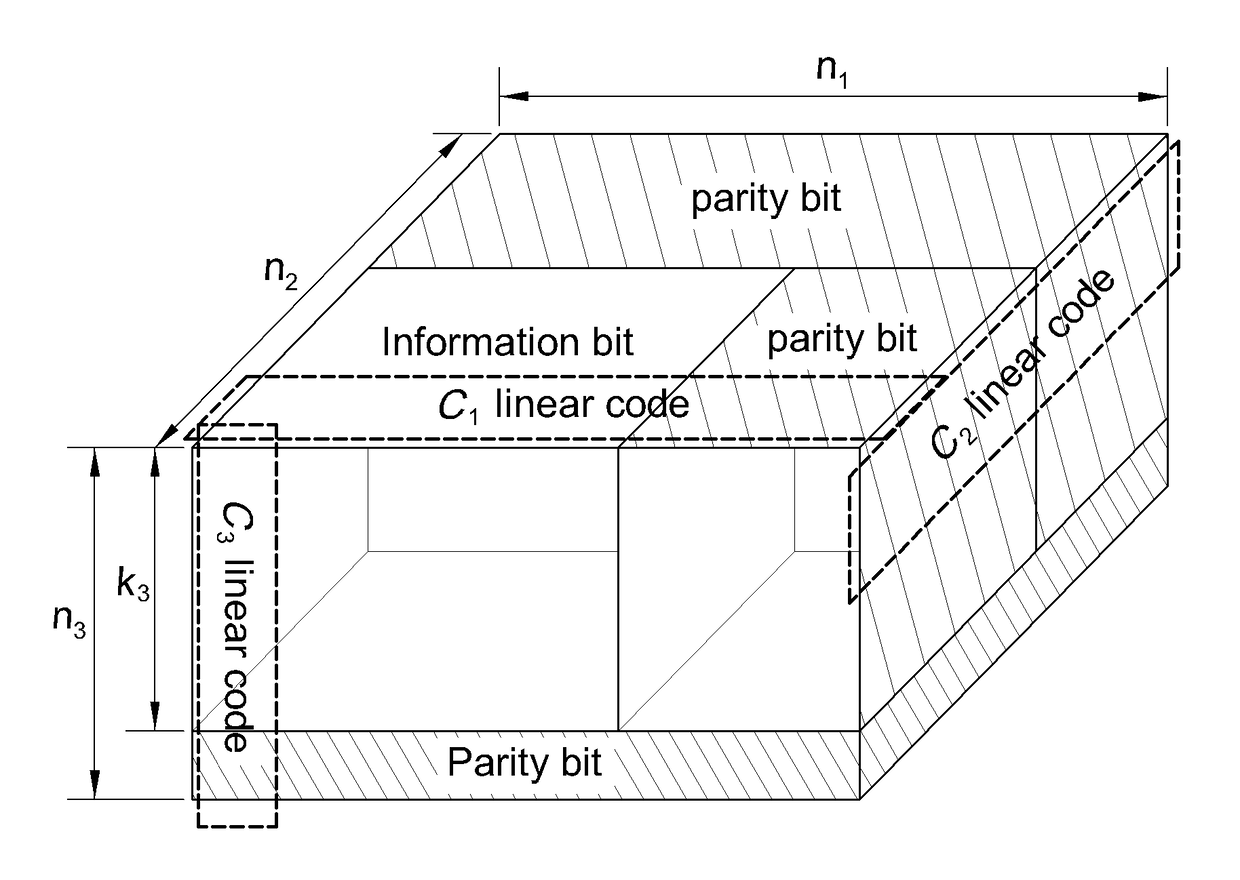

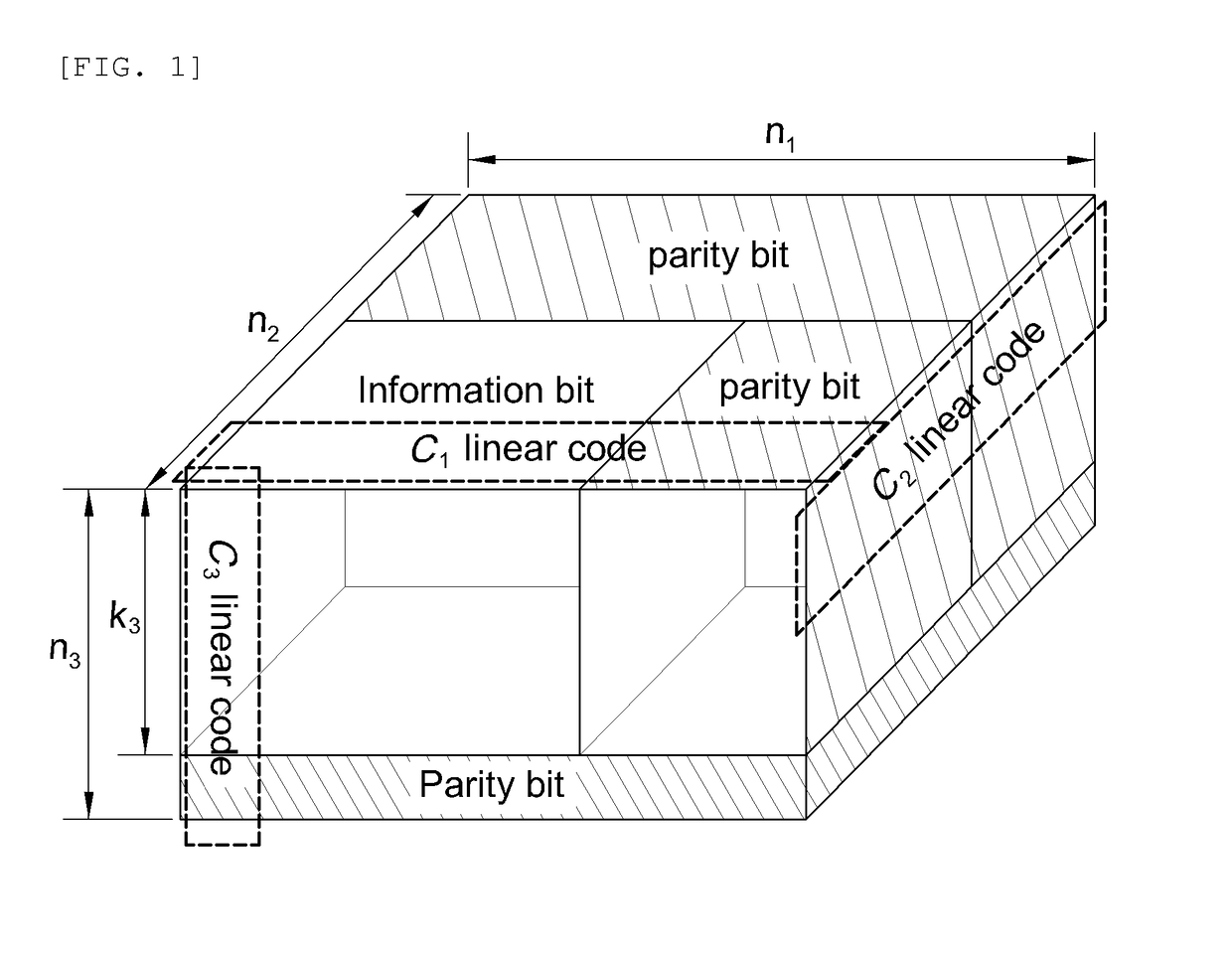

Turbo Product Codes (TPCs) are based on block codes, not convolutional codes. TPCs are built on a 2 or 3 dimensional arrays of extended Hamming codes. Encoding is done in a single iteration. Minimum distance of a 2-D product code is square of constituent code; for a 3-D code, cubed.

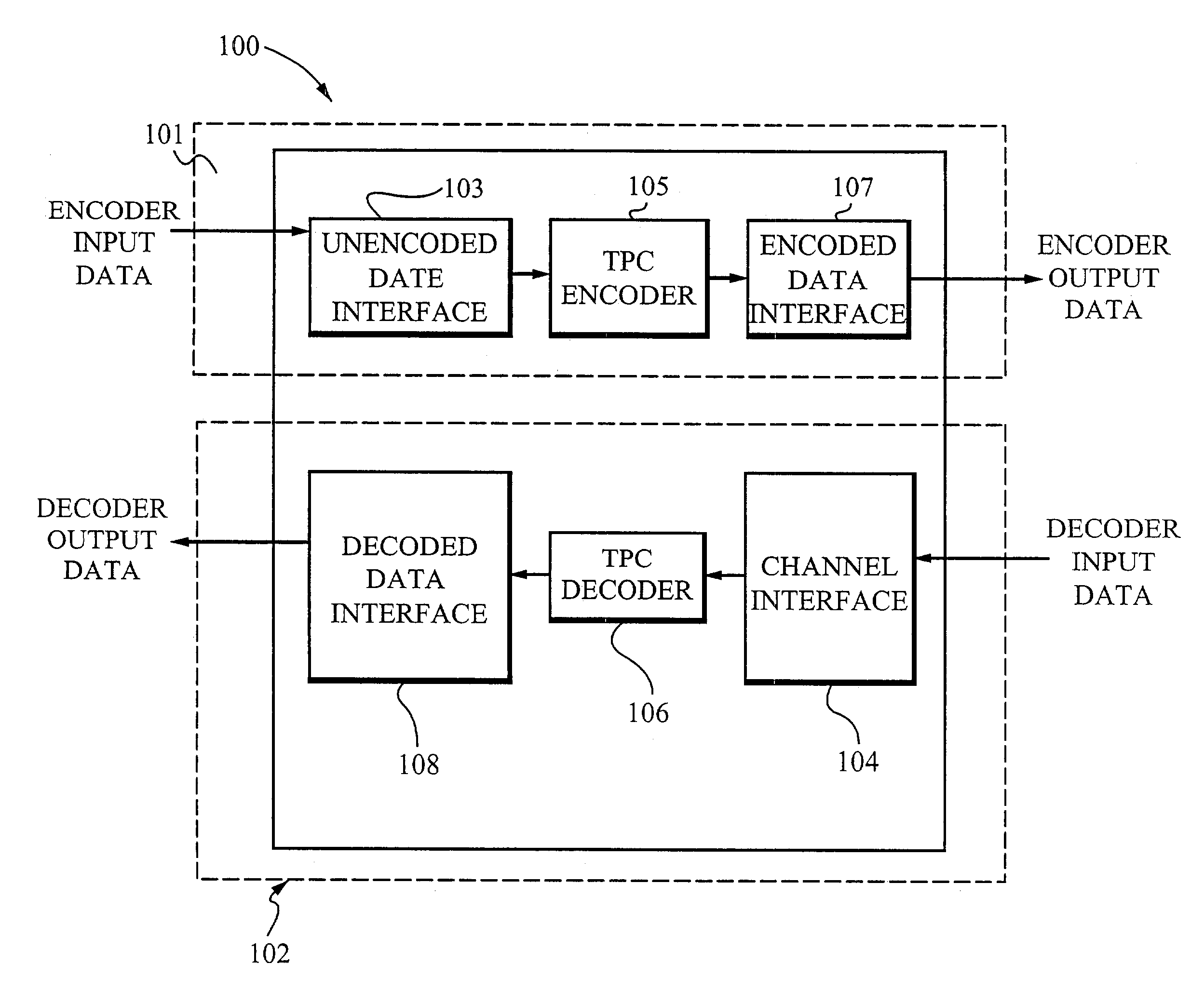

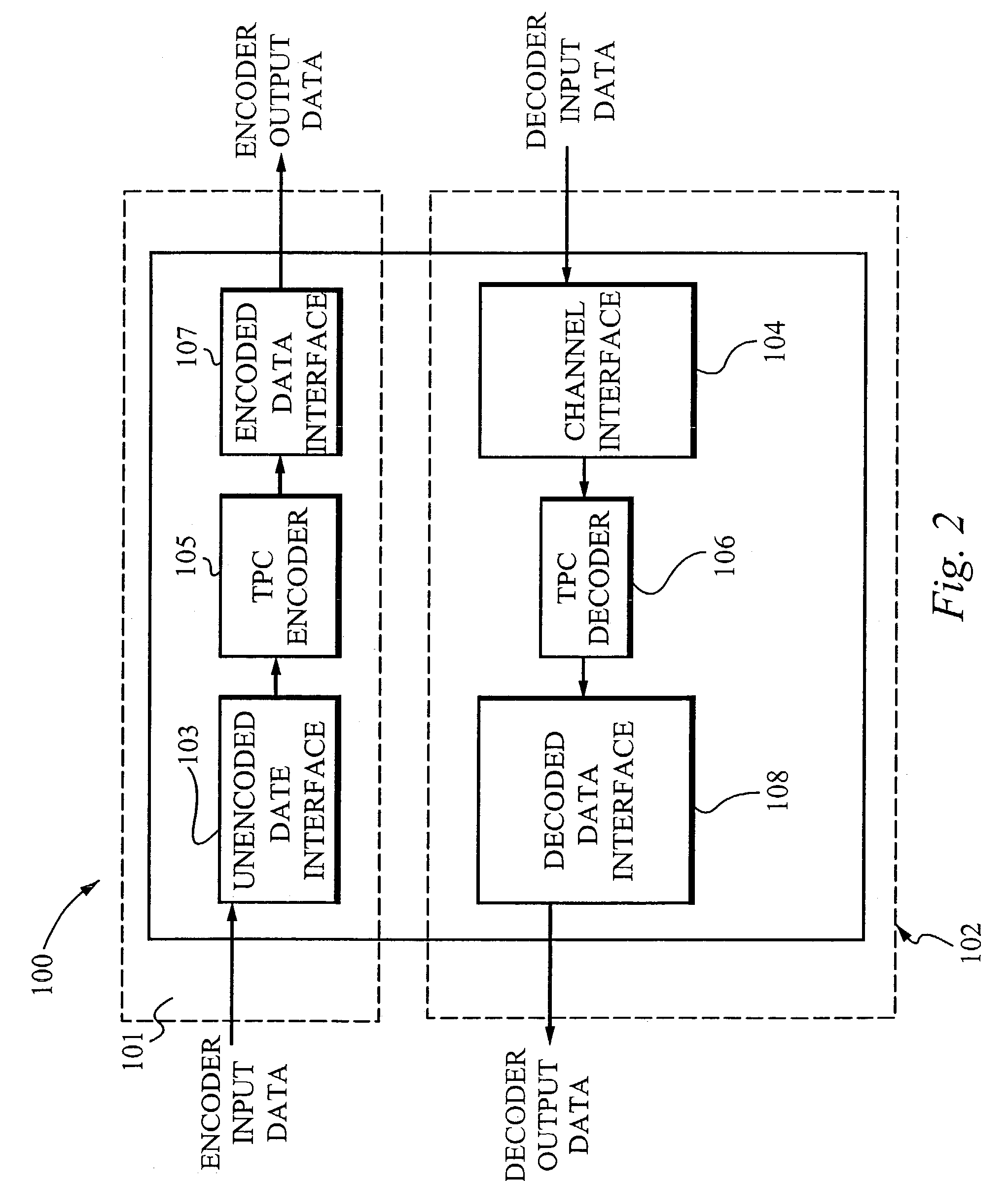

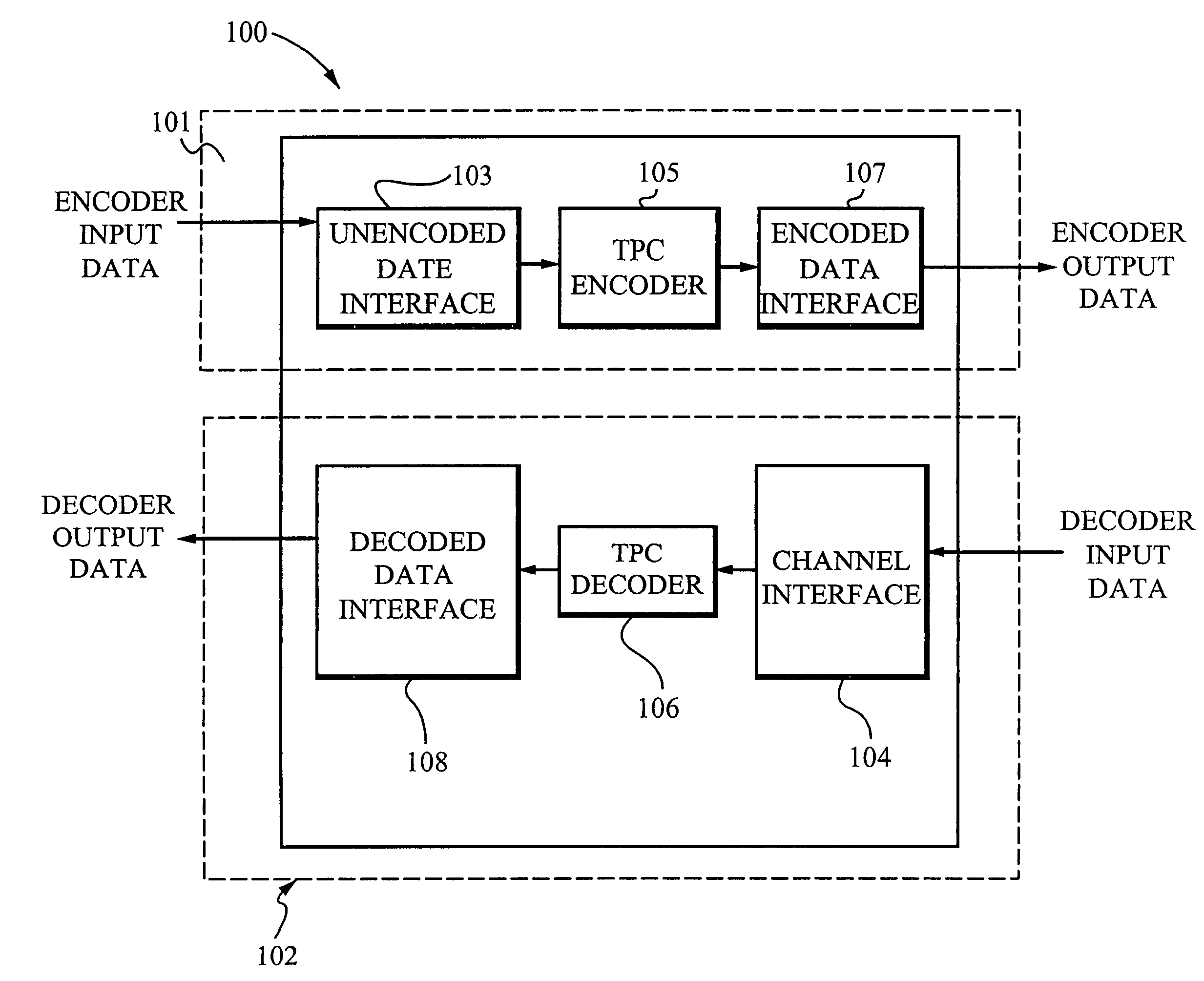

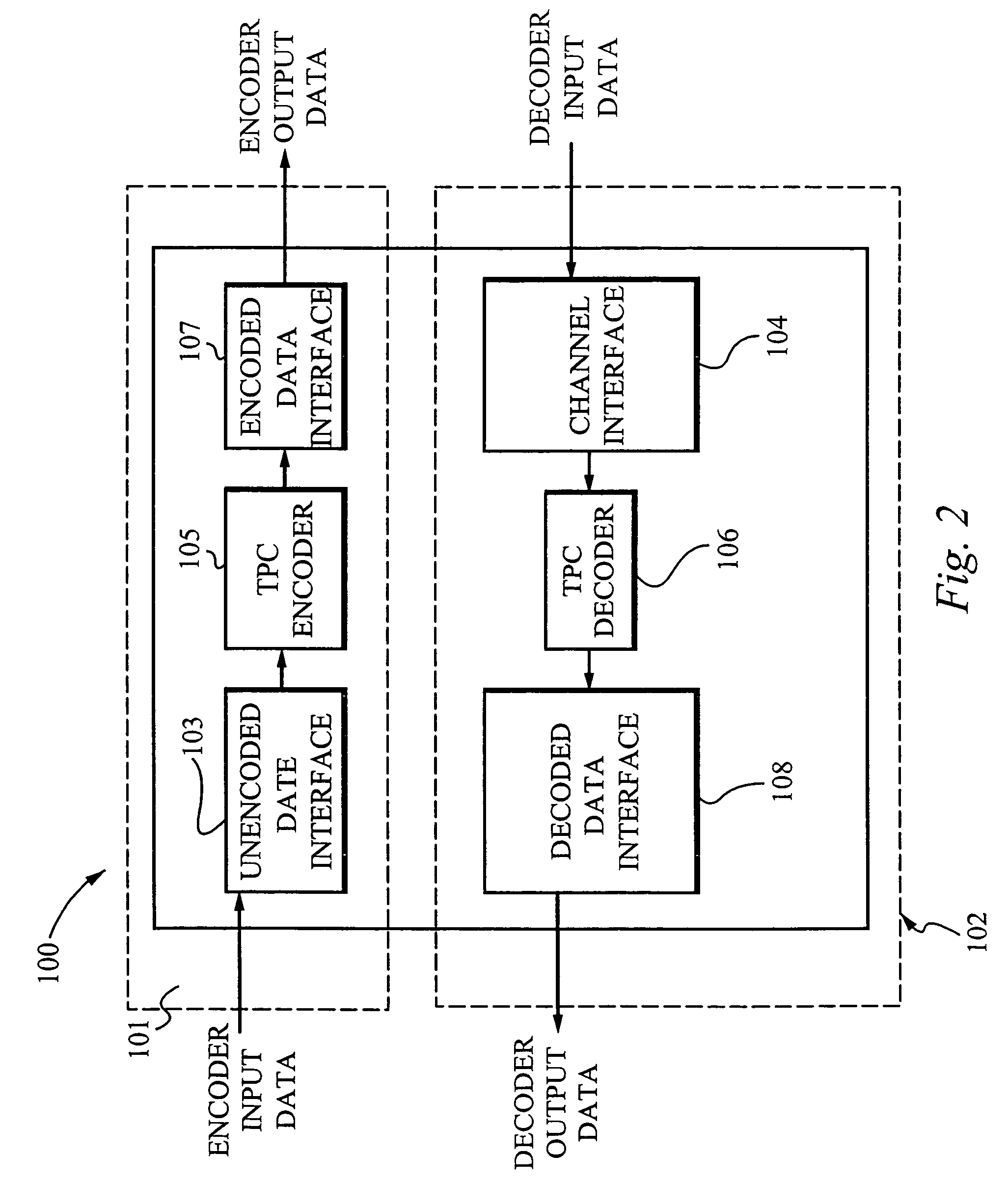

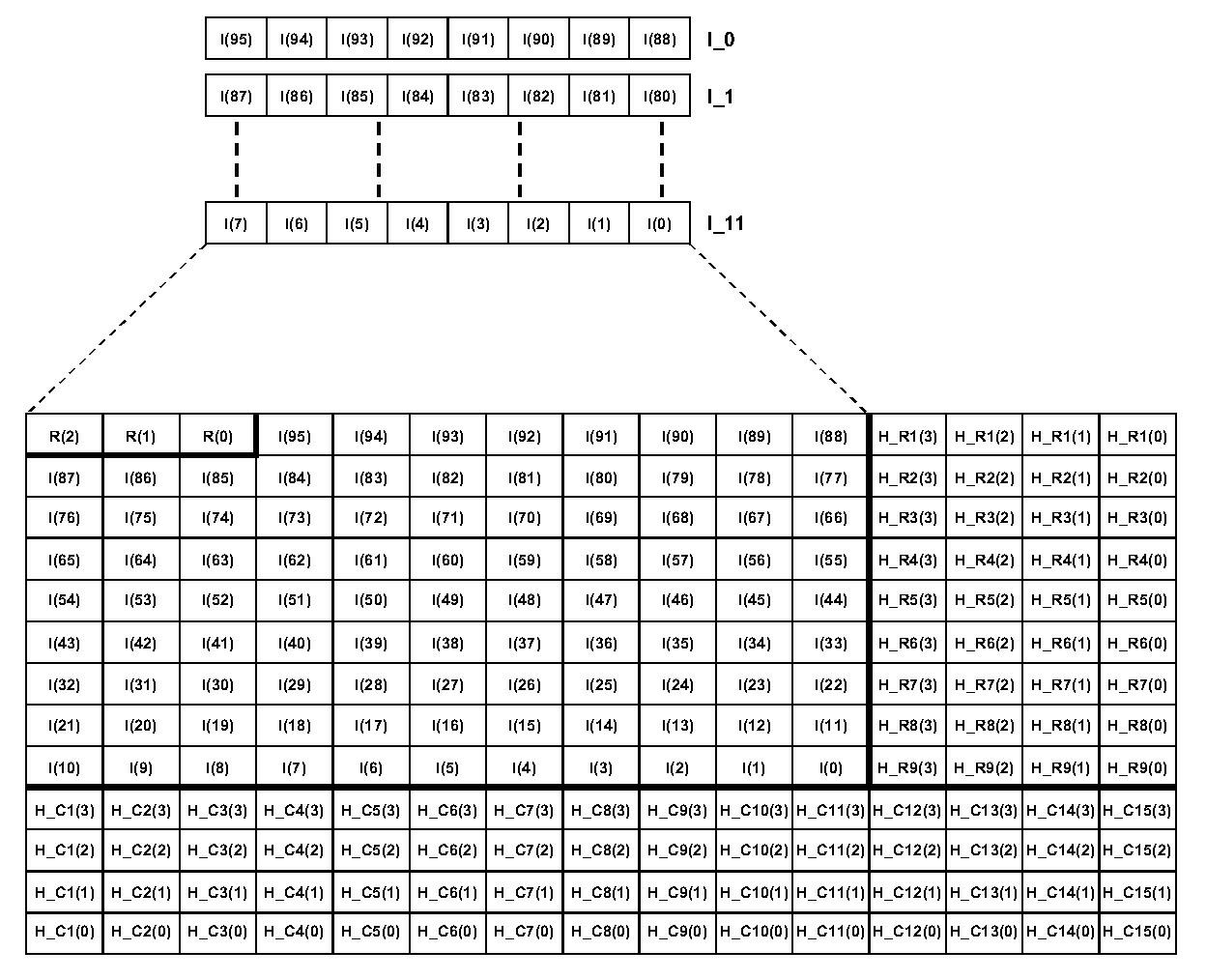

Enhanced turbo product code decoder system utilizing a codeword organization method

InactiveUS7039846B2Error preventionOther decoding techniquesMemory addressTheoretical computer science

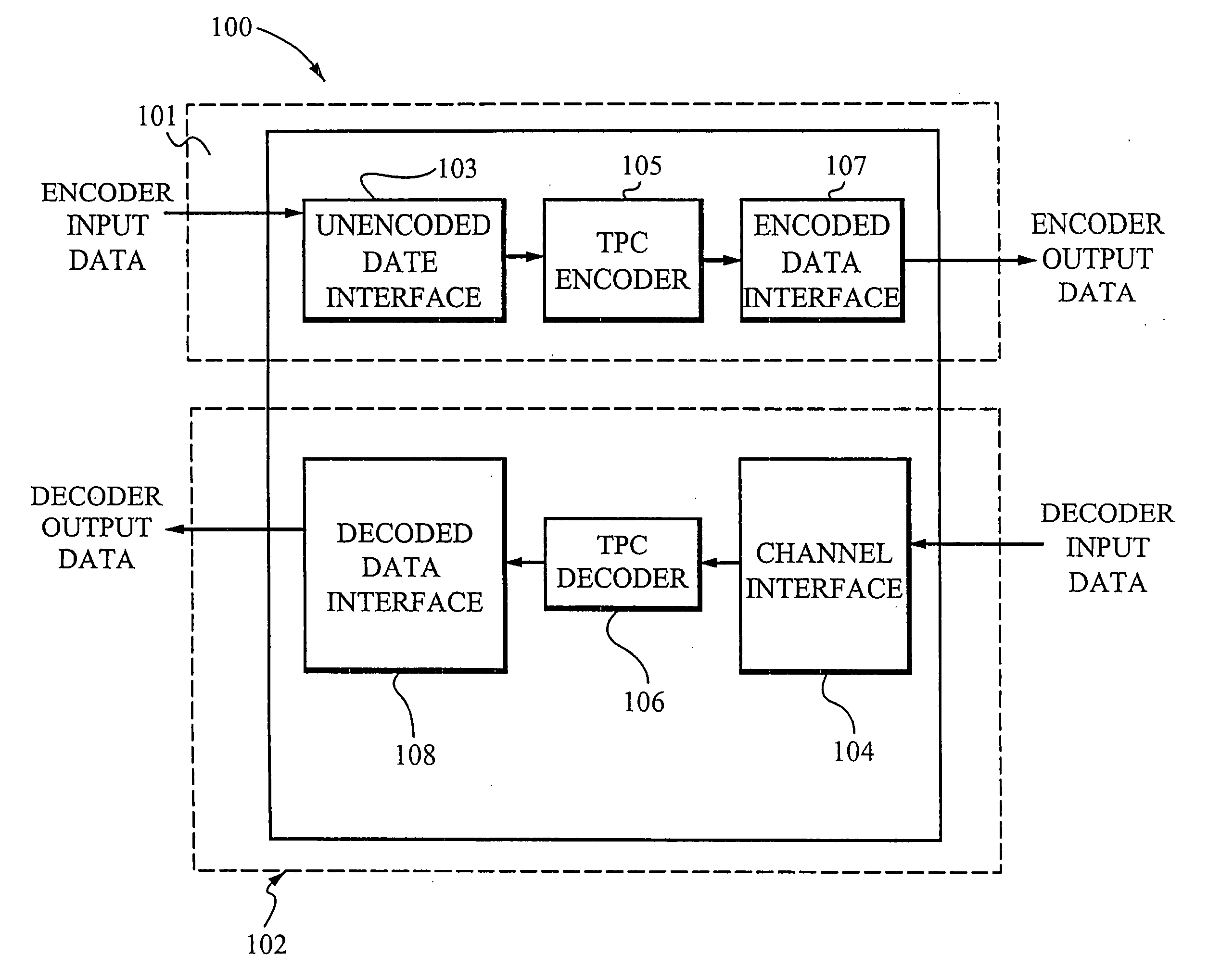

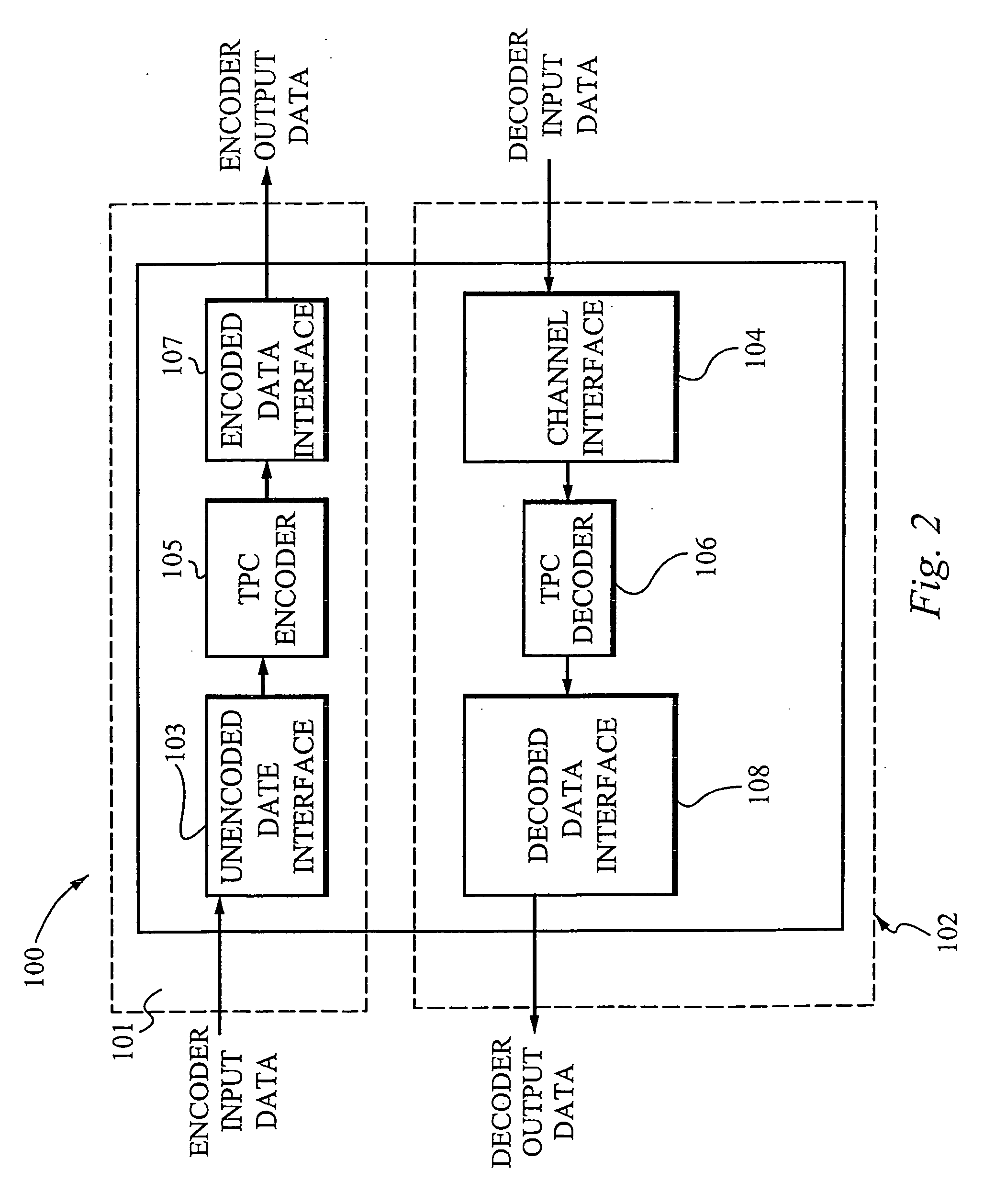

A method and apparatus for decoding a linear block encoded string of information bits comprising: converting the string into a plurality of codewords. Performing hard and soft decisions on each codeword to generate a hard and soft decision vector. Computing the syndrome and finding the location of the two minimum values by Galois Field Arithmetic. Designating these values LOW1 and LOW2 and xoring with a Nc1, thus generating Nc2. Swapping Nc1 with Nc2 and determining the lowest soft decision value, Min1 and a next lowest value, Min2. The two bit locations creating Min1 are designated as MinA and MinB. MinA being replaced with Min2 minus the value MinA. MinB being replaced with Min2 minus the value at MinB. Generating an output codeword by subtracting Min1 from all other bit locations values and 2's complementing all soft values with 0 in their location. Creating the new soft value vector. Some embodiments include a system and method that organizes an encoded codeword. The encoded codeword has several codeword bits. The method receives the encoded codeword, assigns multiple codeword bits to at least one memory address in a plurality of memory addresses, and iteratively decodes the received codeword by utilizing the plurality of memory addresses in a predetermined order. The predetermined order is based on a dimension of the received codeword.

Owner:COMTECH TELECOMM CORP

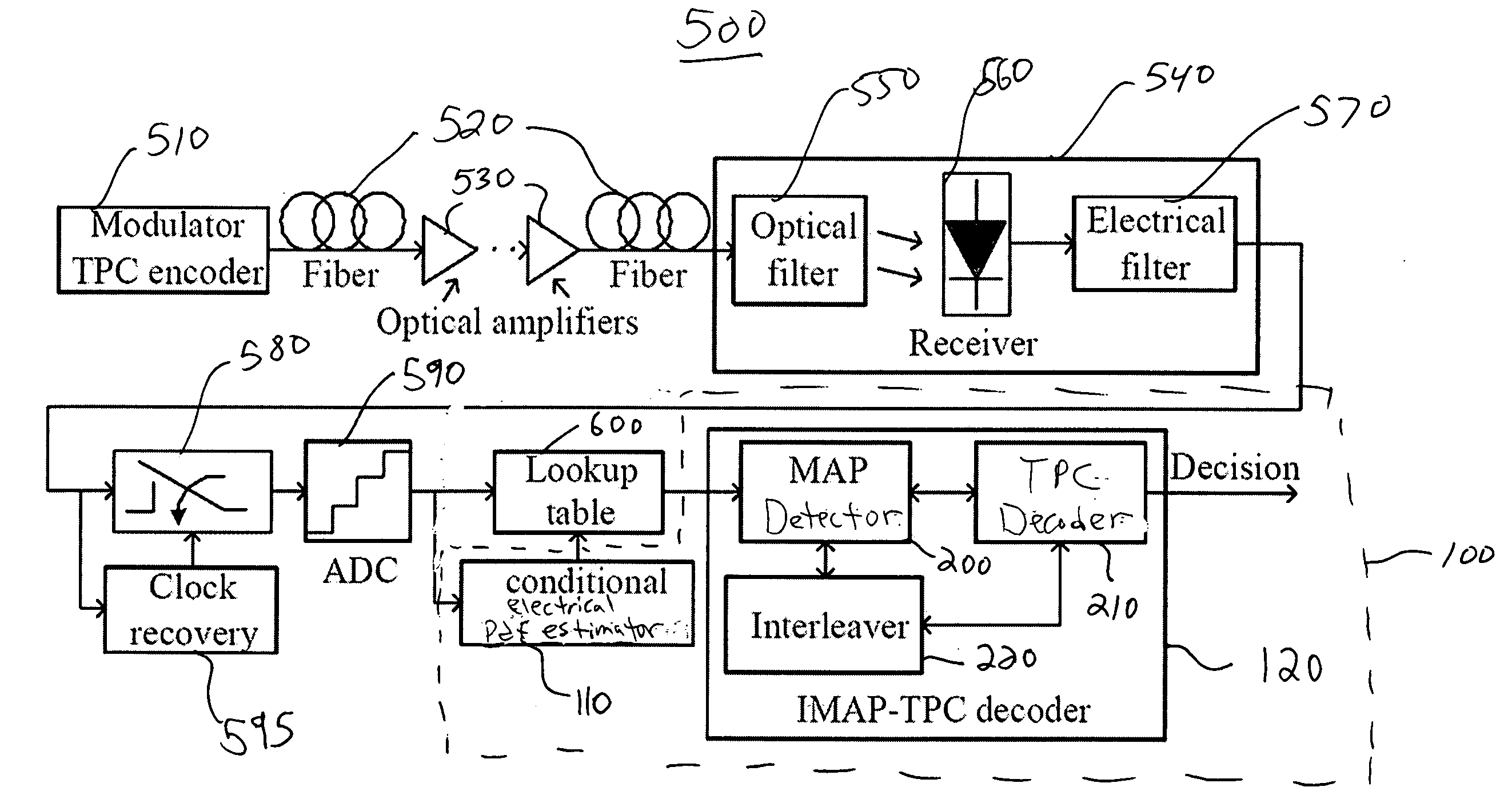

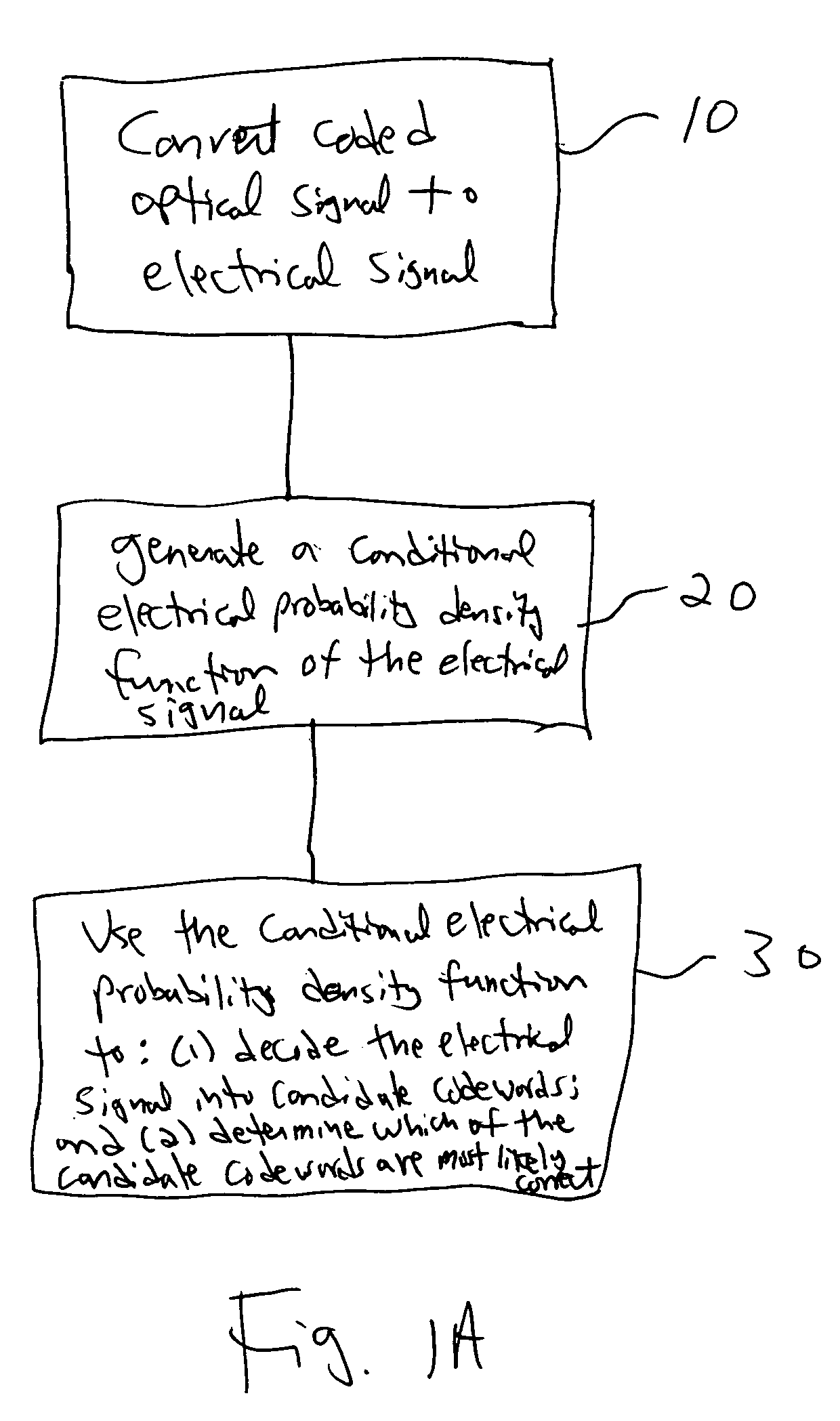

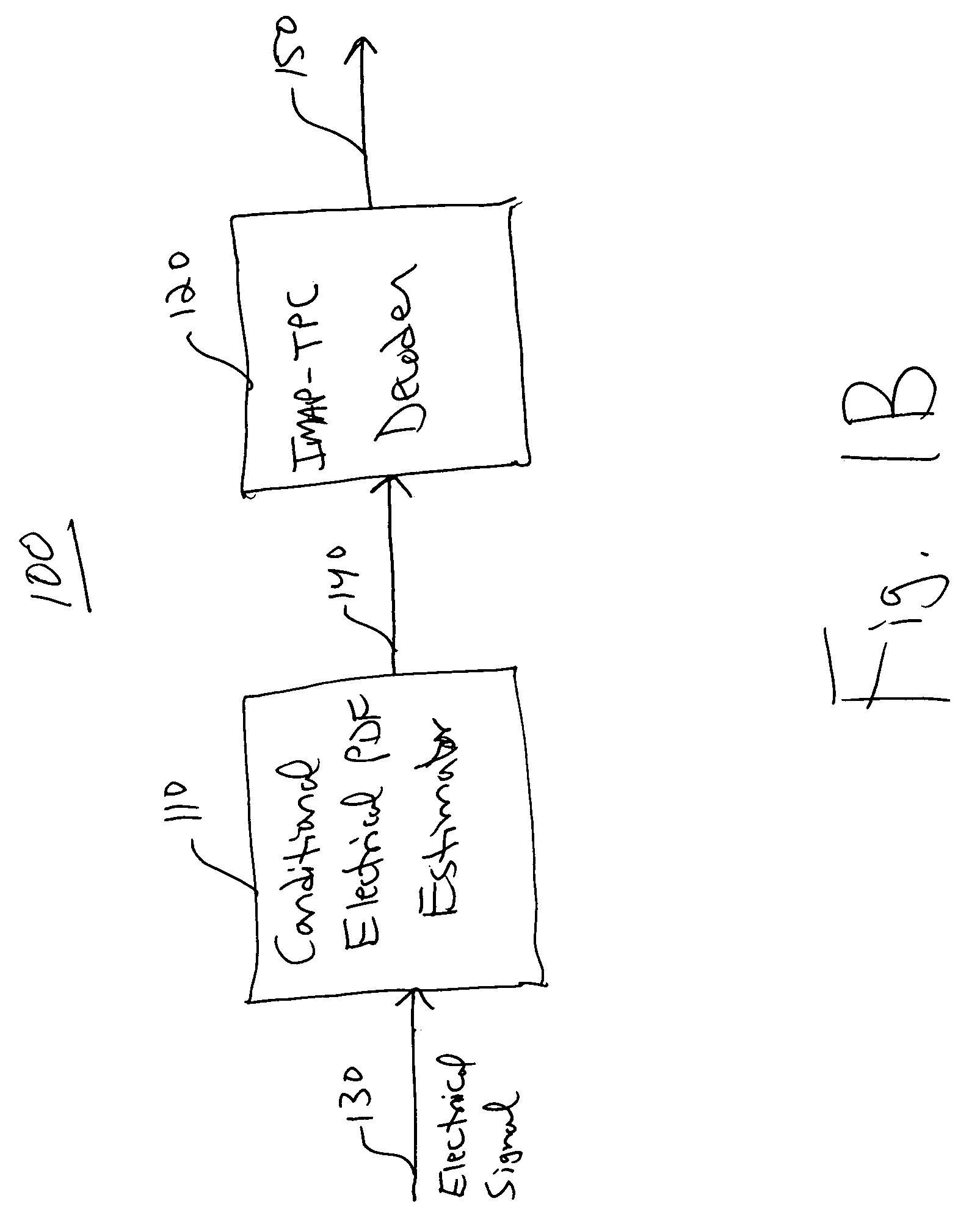

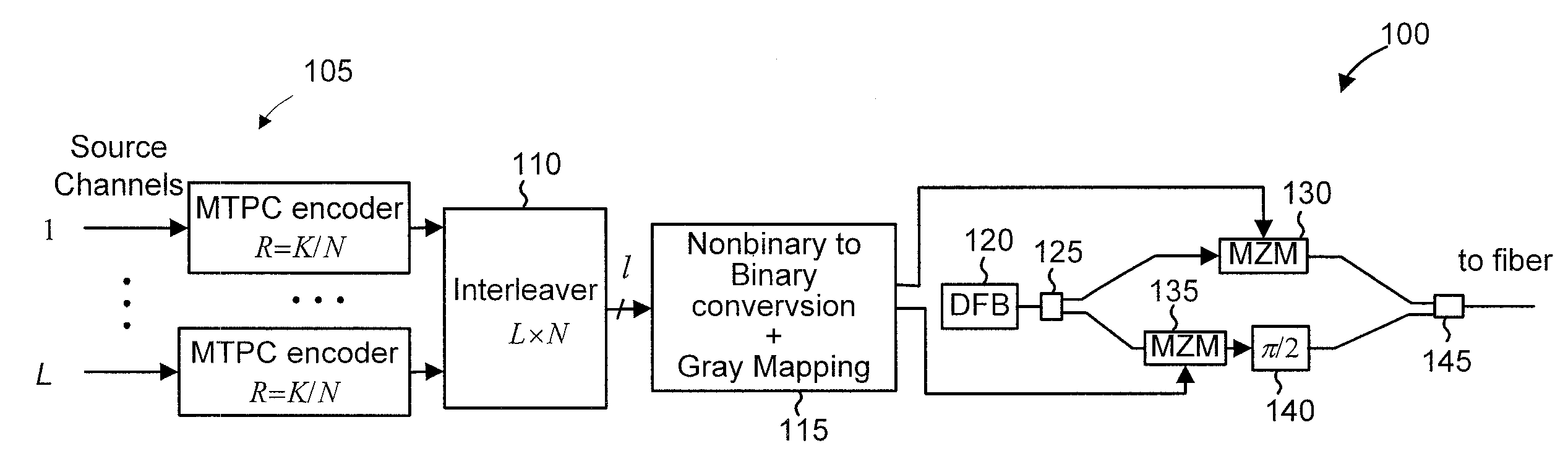

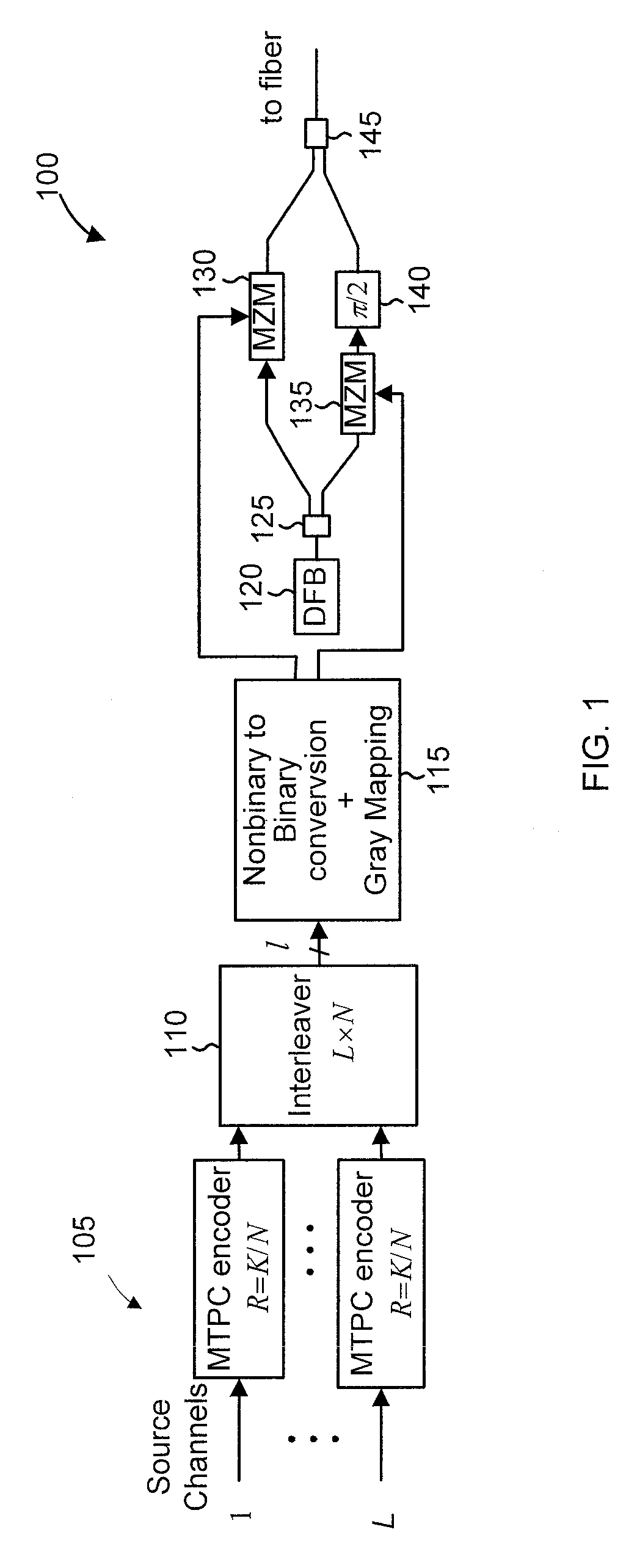

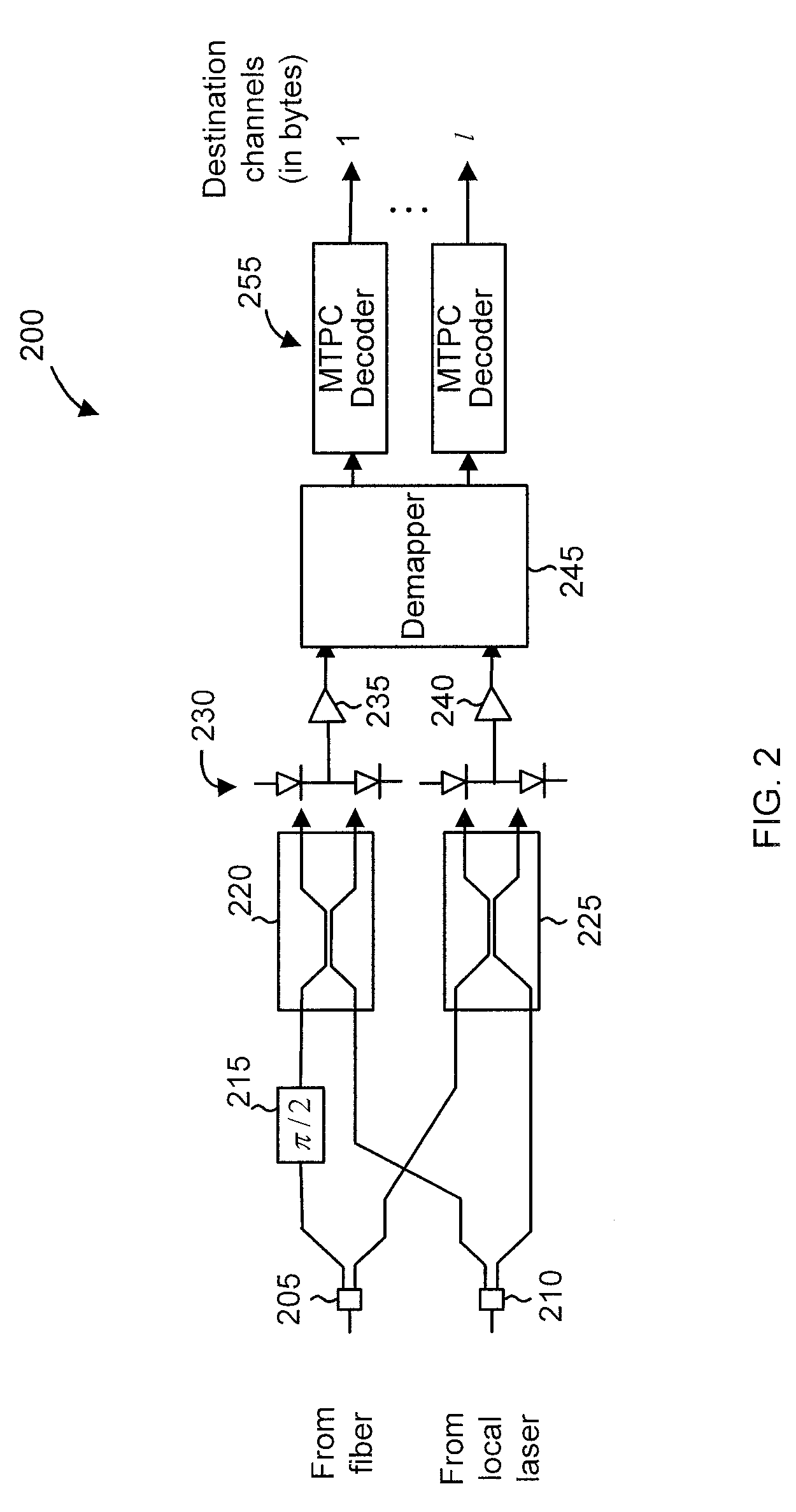

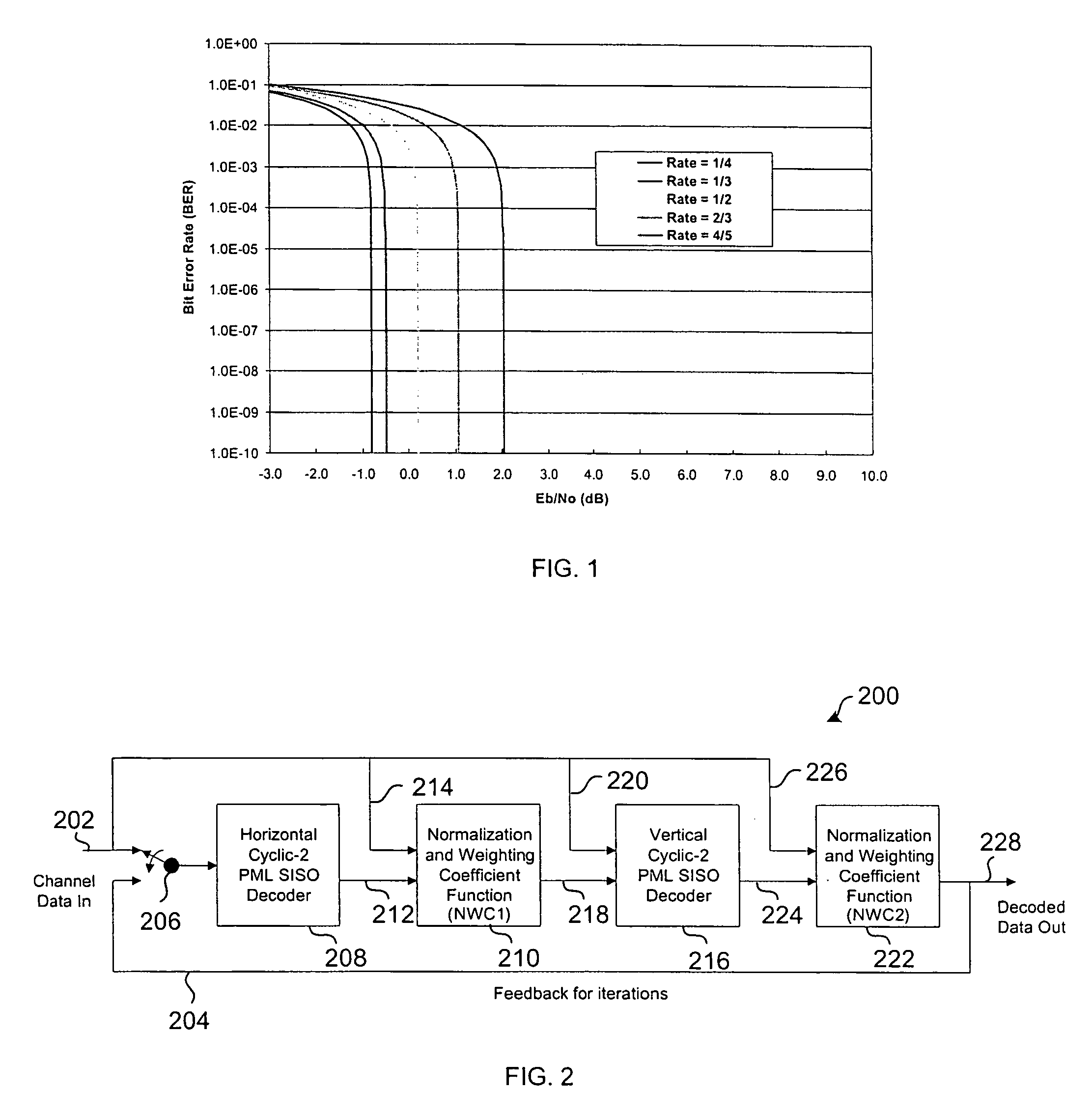

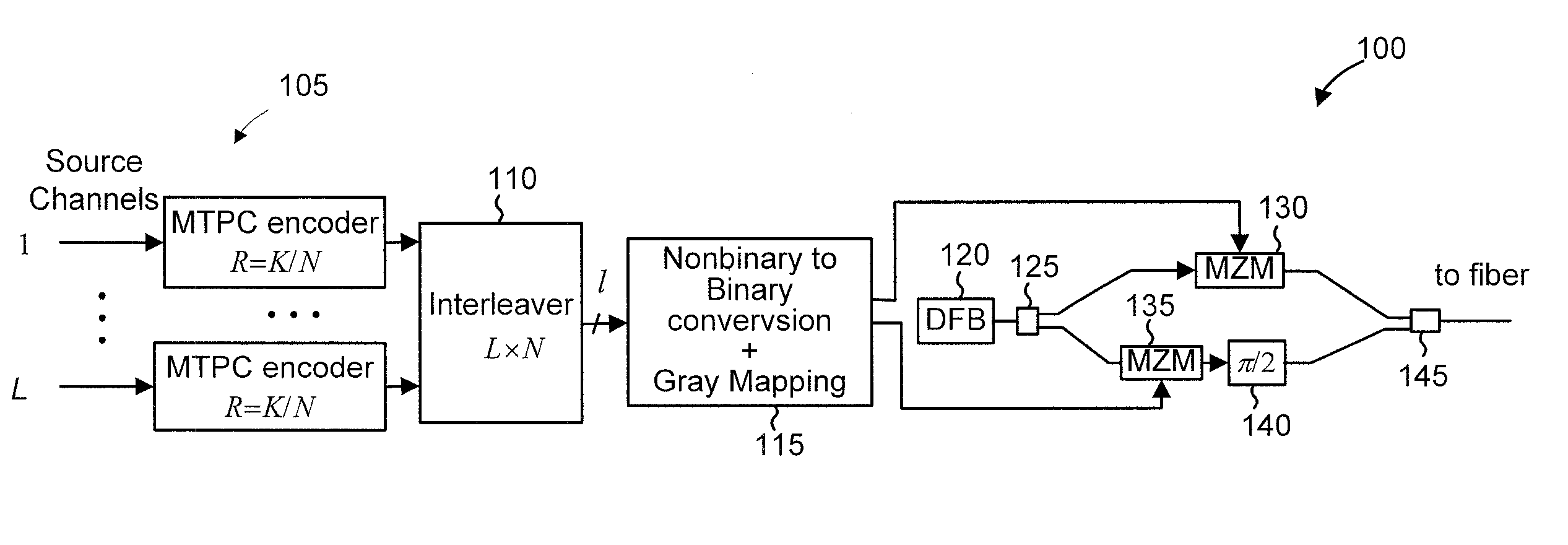

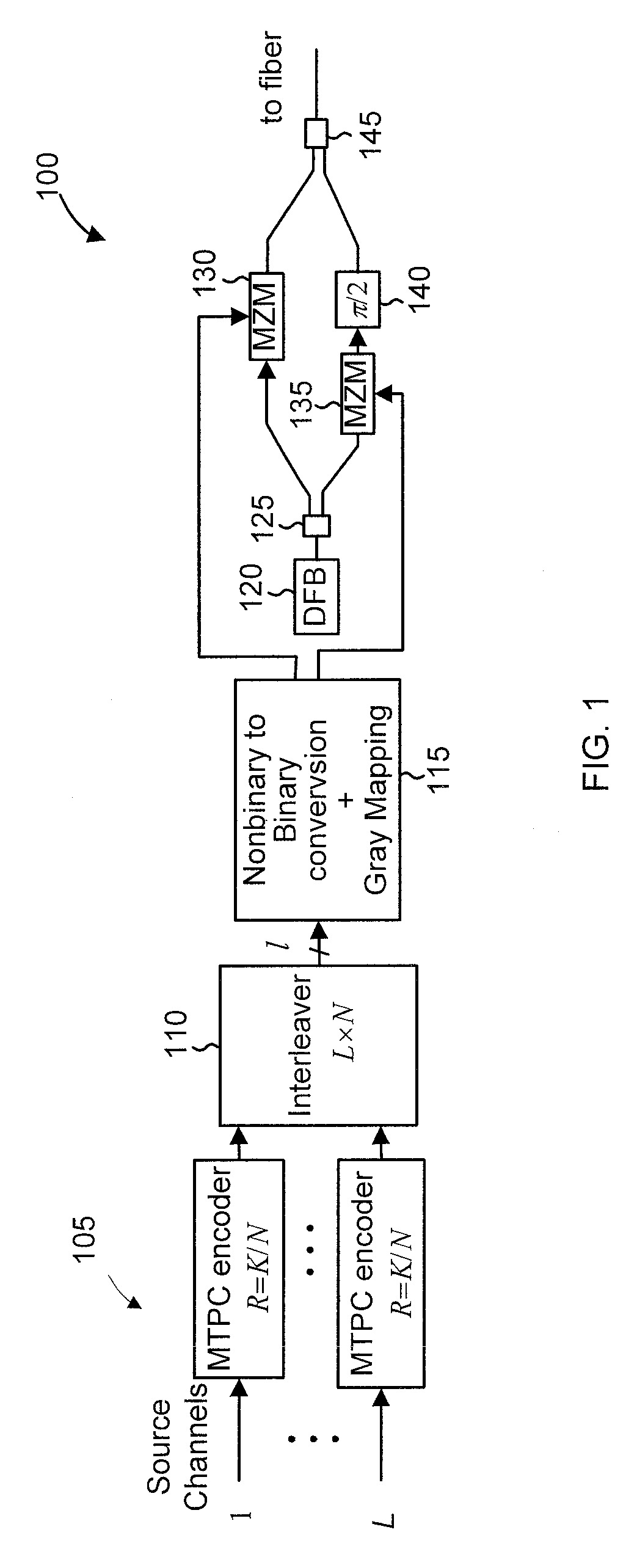

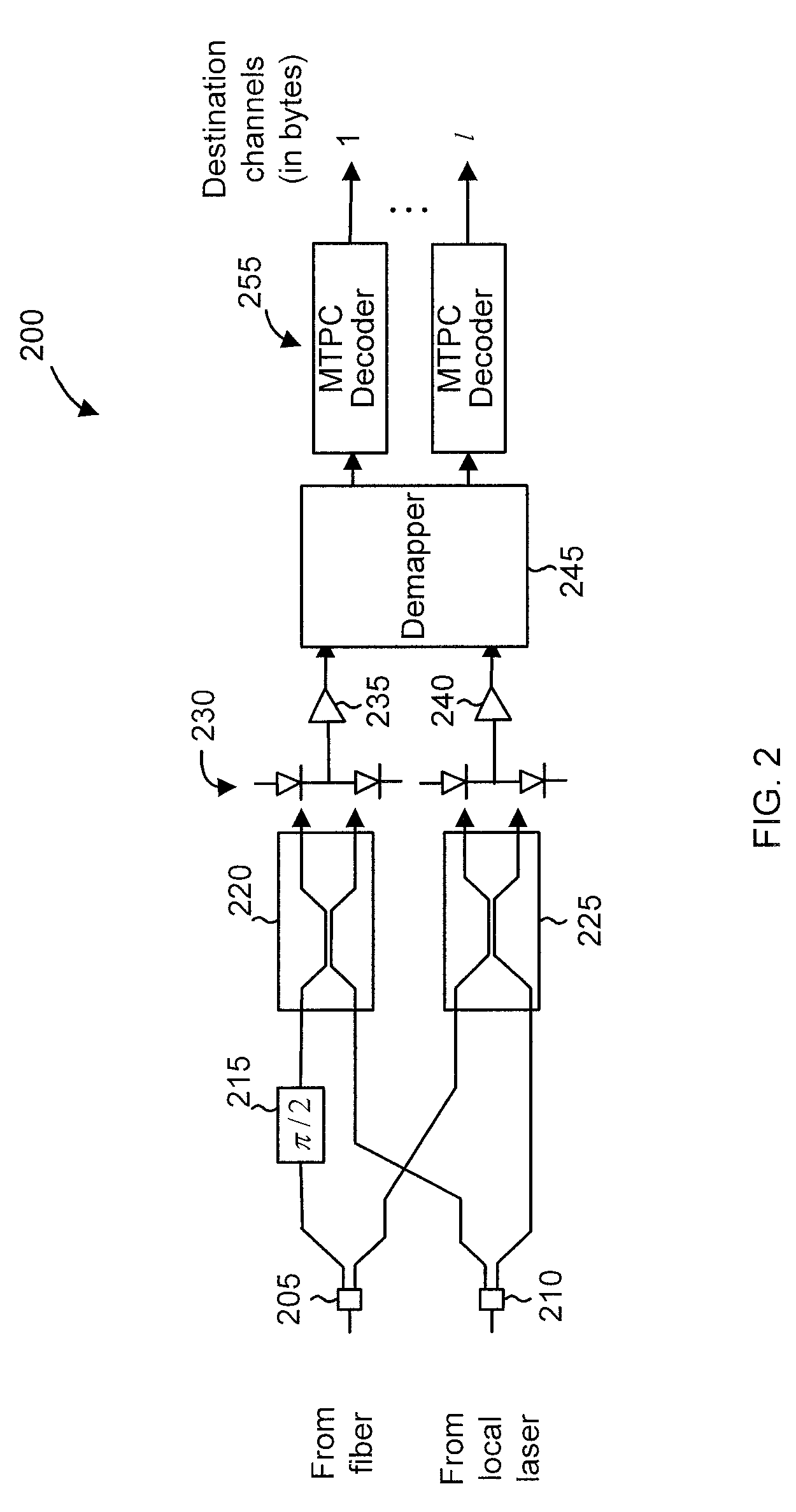

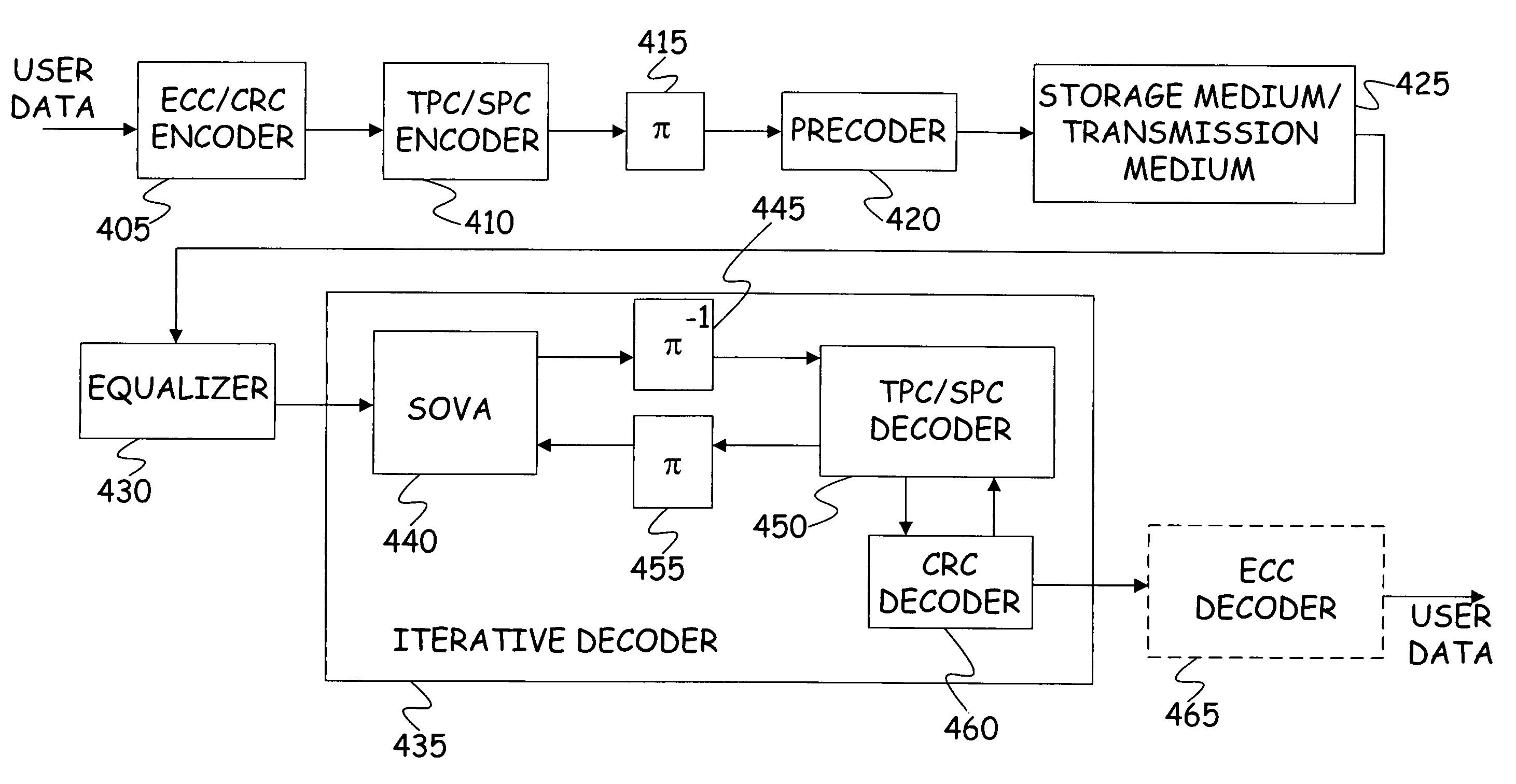

Integrated maximum a posteriori (MAP) and turbo product coding for optical communications systems

InactiveUS20060285852A1Improve fiber performanceImprove bit error rateElectromagnetic transmissionBaseband systemsLogitEqualization

An integrated maximum a posteriori equalization and turbo product coding (IMAP-TPC) system for optical fiber communications systems (OFCS) is provided that uses probabilistic characterization of the electrical current in the presence of inter-symbol interference (ISI) and noise to compensate their effects and improve the bit error rate. In the IMAP-TPC system, turbo product code (TPC) decoding is integrated with a symbol-by-symbol maximum a posteriori (MAP) detector. The MAP detector calculates the log-likelihood ratio of a received symbol using the conditional electrical probability density information, and hence obtains a much more accurate reliability measure than the traditional measure used in the TPC decoder.

Owner:UNIV OF MARYLAND BALTIMORE COUNTY

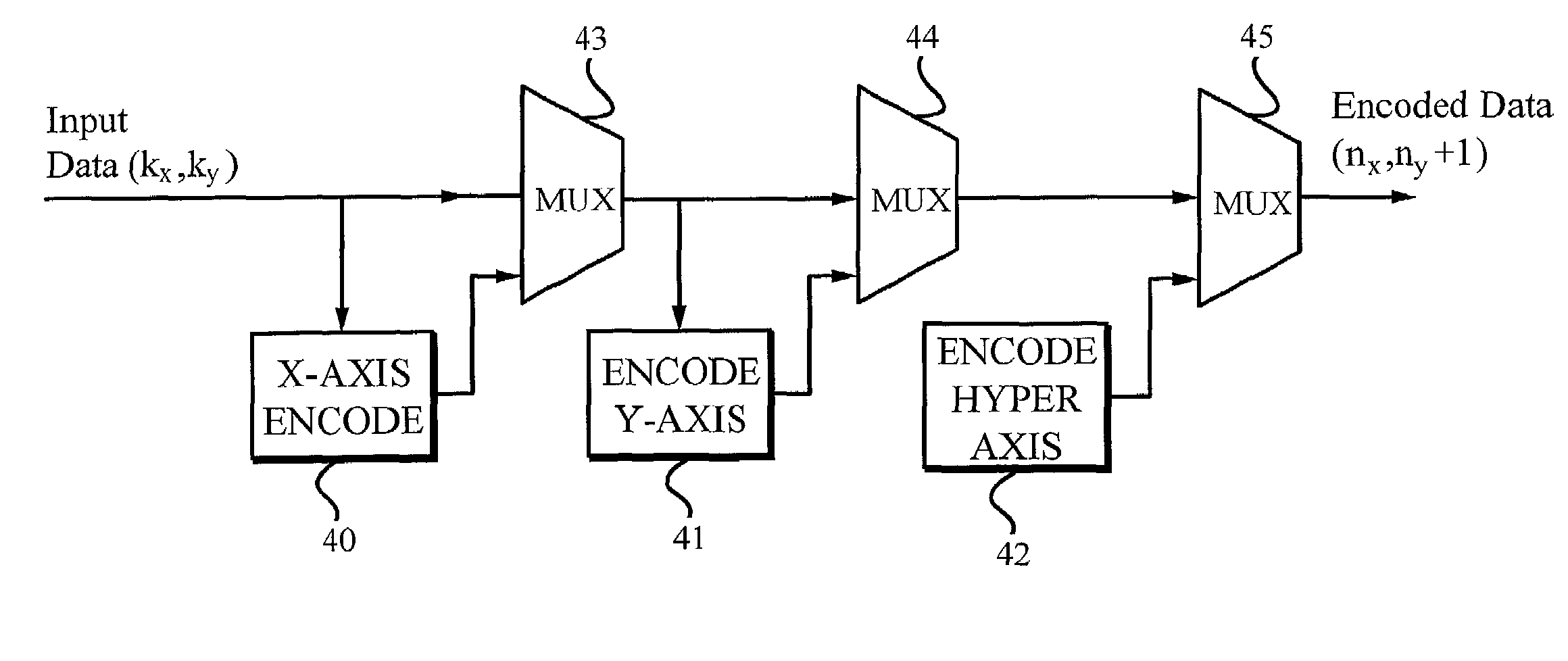

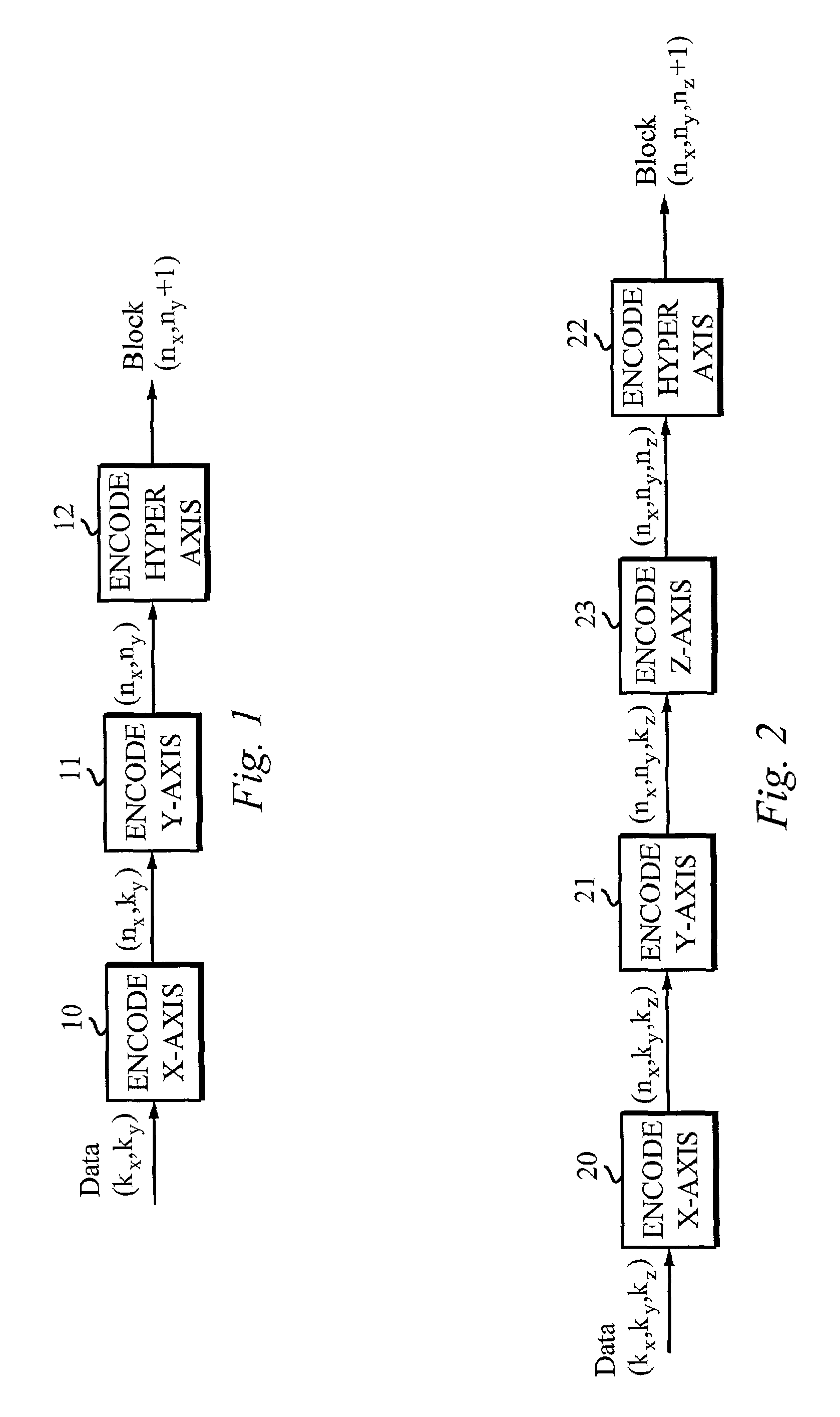

Enhanced turbo product codes

InactiveUS7356752B2Code conversionError correction/detection by combining multiple code structuresComputer hardwareBlock code

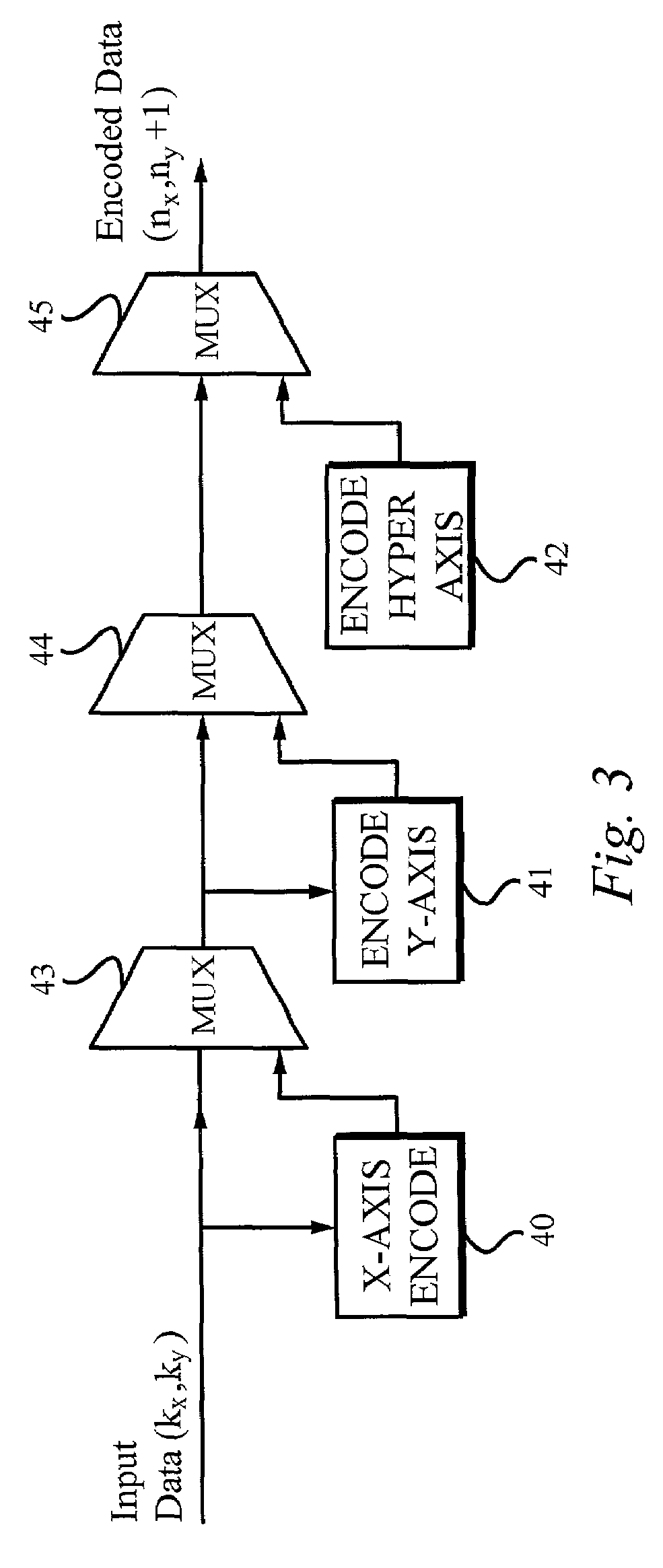

A hyper encoder module encodes a block of data having a plurality of sub-blocks. Each sub-block includes a plurality of systematic block code codewords. A parity sub-block is added to the block. The parity sub-block is a first sub-block rotated by a predetermined number of bits. Each subsequent sub-block in the n-dimensional block is rotated by an appropriate number of bits and bit-wise XORed. An encoder method and apparatus which includes the hyper encoder module receives the block of data. A row of the block is immediately output and encoded by a first module according to a first encoding scheme. A column is encoded by a second module according to a second encoding scheme. A second set of encoded data is generated, iteratively updated and output by the second module. The hyper encoder module hyper-diagonally encodes the information bits as described above and then output.

Owner:COMTECH TELECOMM CORP

Enhanced turbo product code decoder system

InactiveUS20060212781A1Error preventionOther decoding techniquesTheoretical computer scienceGalois field arithmetic

Owner:COMTECH TELECOMM CORP

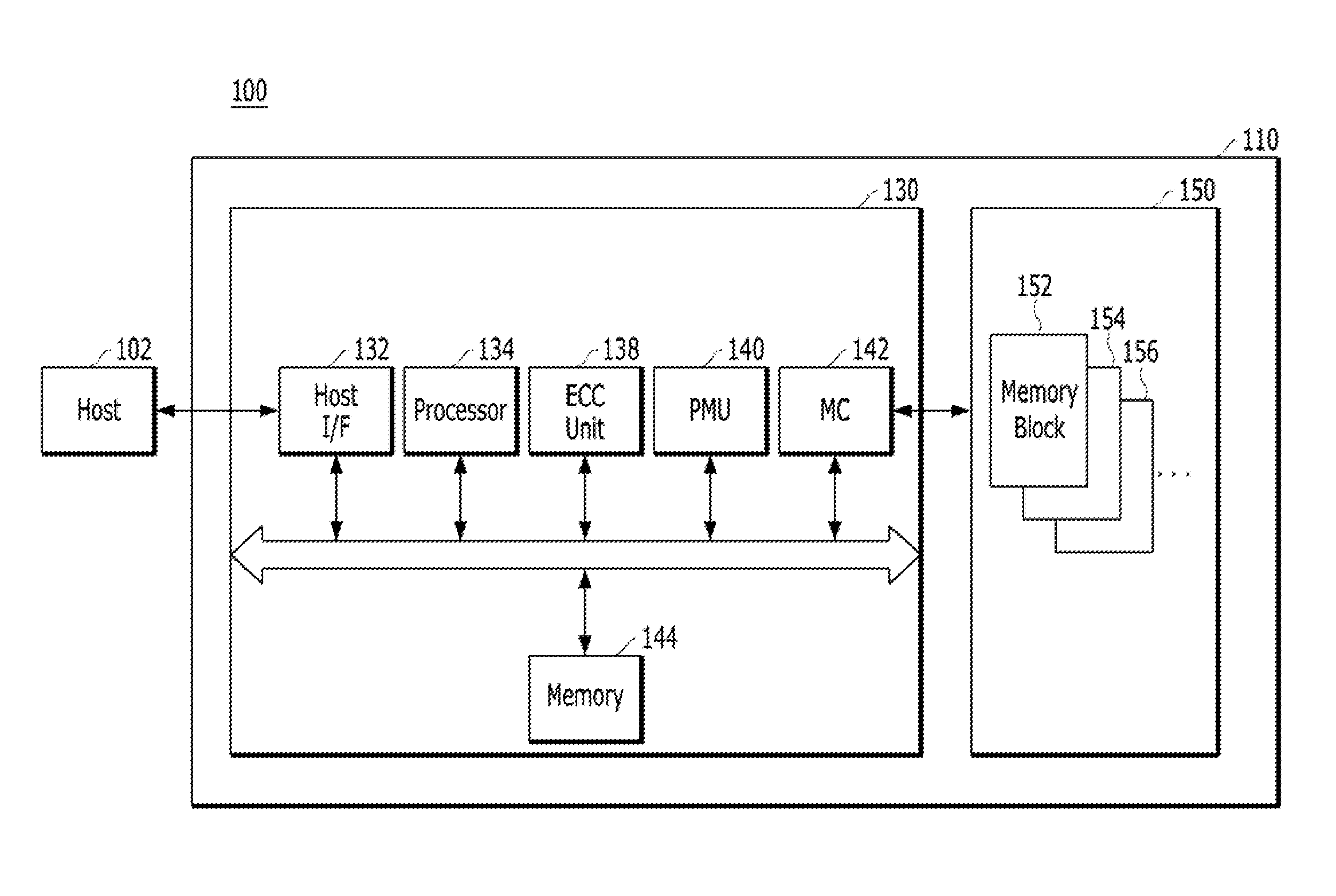

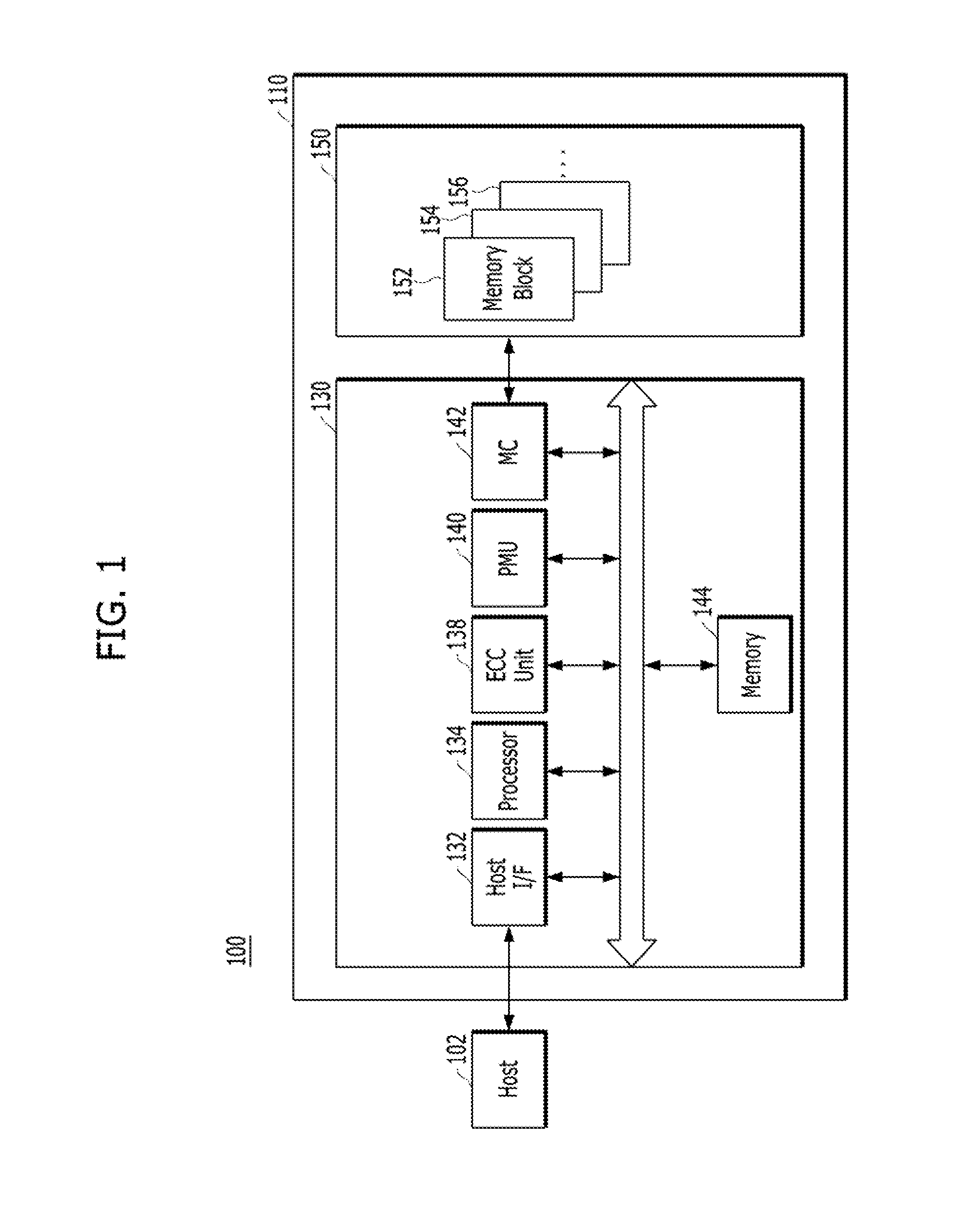

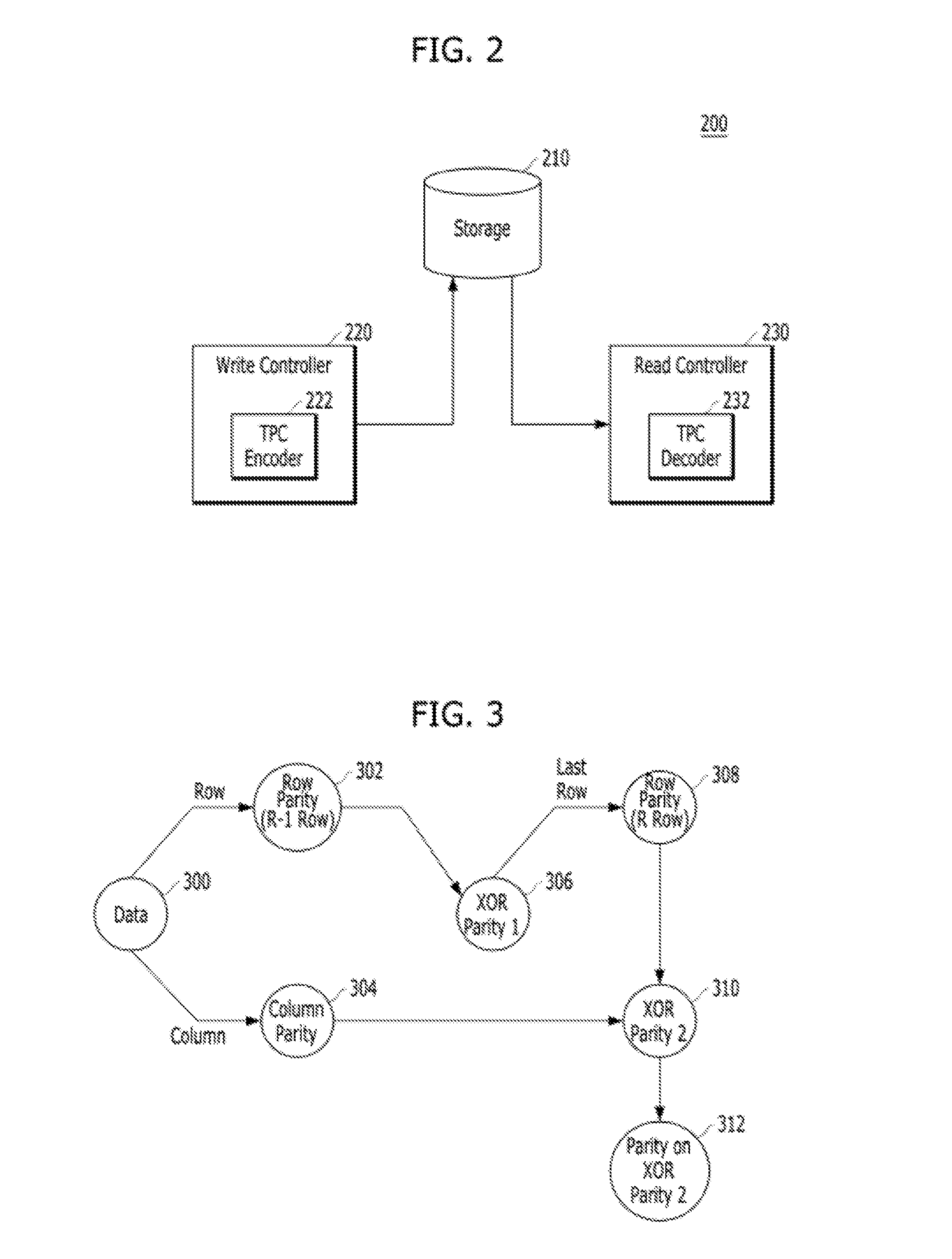

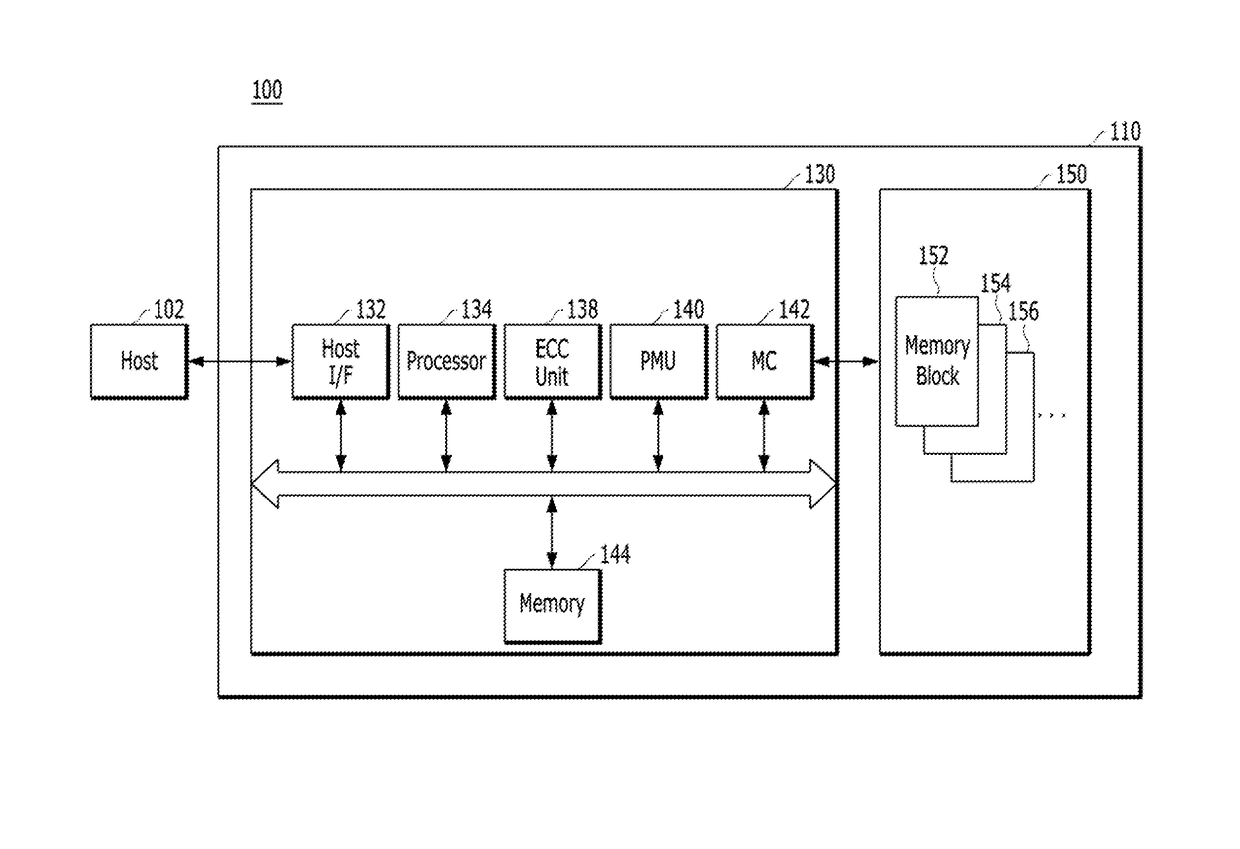

Turbo product codes for NAND flash

ActiveUS20160164543A1Code conversionError correction/detection by combining multiple code structuresComputer scienceNand flash memory

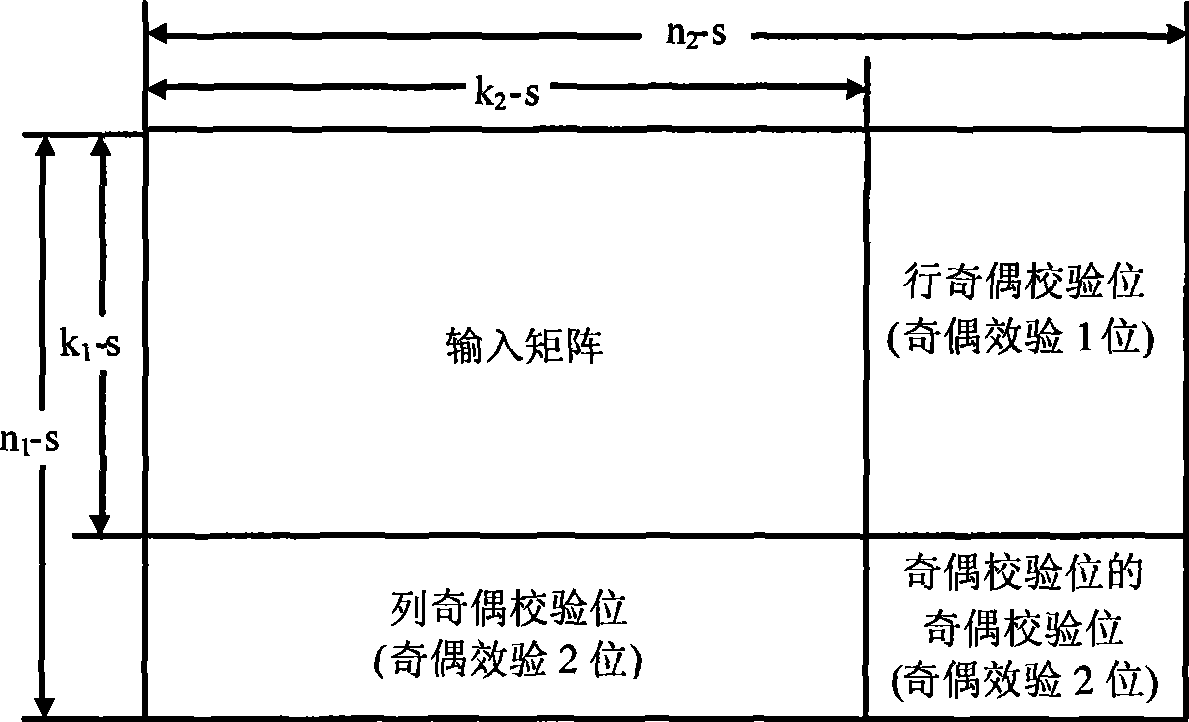

A method of encoding data in a data block includes generating a first XOR parity from an XOR of all data bits in the data block and an XOR of all row parities of all rows in the data block besides a last row, storing the first XOR parity in the last row, and generating a second XOR parity from an XOR of all column parities of all columns in the data block and an XOR of a parity of the last row.

Owner:SK HYNIX INC

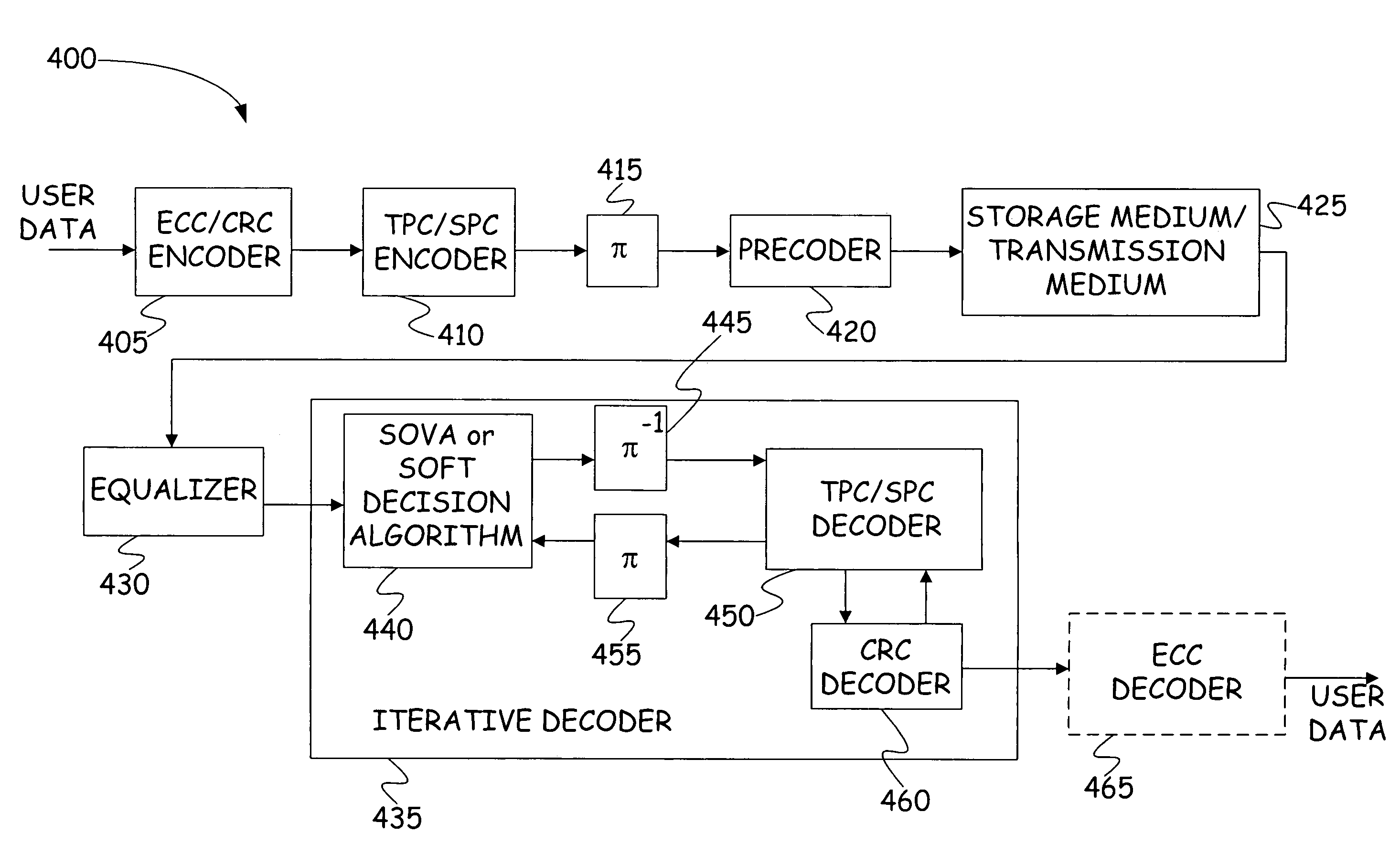

Cyclic redundancy check based message passing in turbo product code decoding

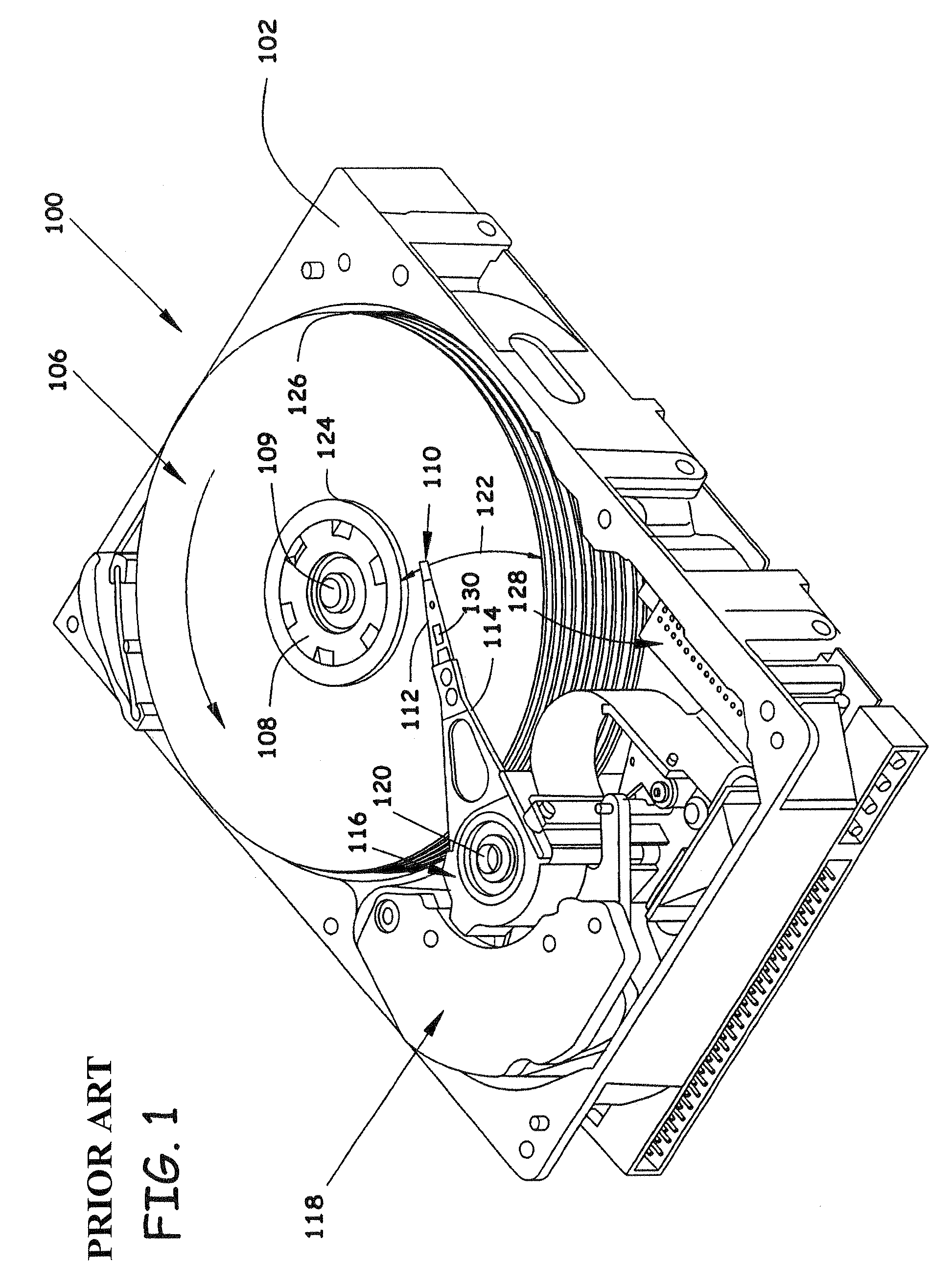

InactiveUS7383484B2Raise the ratioLess complexCode conversionRecord information storageCoding blockHigh probability

A method of decoding a turbo product code (TPC) code word comprises performing a cyclic redundancy check (CRC) on each of a plurality of code blocks of the TPC code word. The bits of code blocks of the TPC code word which pass the CRC are assigned an artificially high probability confidence measure, such as an artificially high log-likelihood ratio. Assigning these bits an artificially high probability confidence measure allows an iterative process, between a soft decision algorithm and a TPC decoder, to be less complex and to converge on a correct decoding solution more quickly. Apparatus for implementing the method are also provided.

Owner:SEAGATE TECH LLC

Multidimensional turbo product codes and generalized low-density parity-check codes with component reed-solomon codes for optical transmission

ActiveUS20090282314A1Code conversionError correction/detection by combining multiple code structuresLow-density parity-check codeLow density

A transmitter, a receiver, and corresponding methods are provided. The transmitter includes encoders configured to encode source bit streams from L information sources into bytes of codewords. Each encoder includes different (n, k) multidimensional turbo-product codes of code rate R=k / n, where k is a number of information bytes, and n is code word length. The encoders operate in at least two phases. A first phase involves operating ky column-encoders in parallel on kx bytes per column to generate the code words for a current dimension. A second phase involves operating nx row-encoders in parallel on ky memory locations per rows to generate the code words for the current dimension. The first and second phases are repeated for remaining layers of the current dimension and layers of other dimensions.

Owner:NEC CORP

Enhanced turbo product code decoder system

InactiveUS7085987B2Error preventionOther decoding techniquesTheoretical computer scienceGalois field arithmetic

Owner:COMTECH TELECOMM CORP

Turbo Product Code implementation and decoding termination method and apparatus

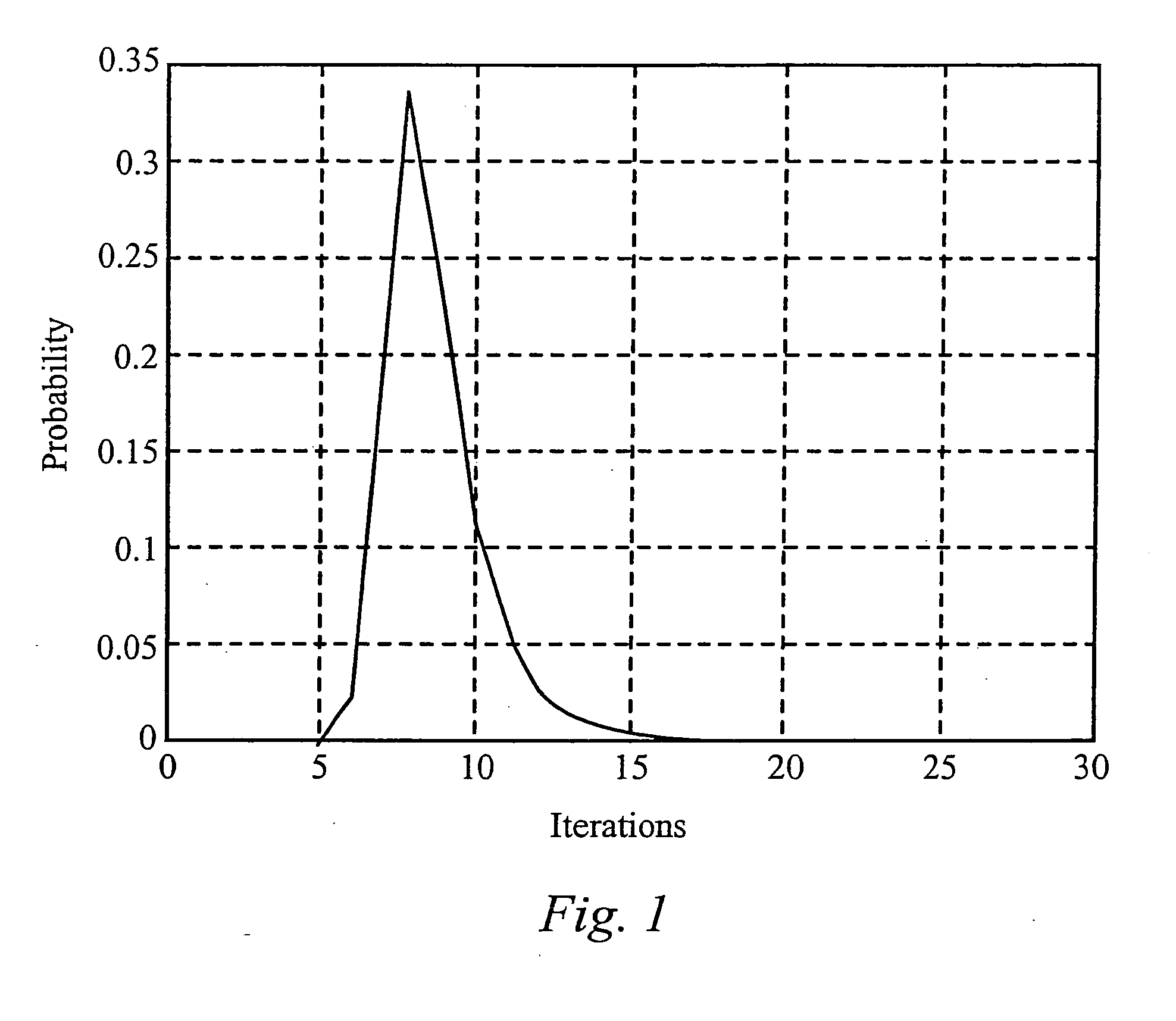

A method of decoding a turbo product code (TPC) code word comprises iteratively decoding the TPC code word using an iterative decoder. The method further comprises terminating the iterative decoding when the TPC code word satisfies a cyclic redundancy check (CRC). The TPC code word can include a plurality of square code blocks of user data, with CRC data bits appended to one of the plurality of code blocks instead of replacing user data within the code blocks. Apparatus for implementing the method are also provided.

Owner:SEAGATE TECH LLC

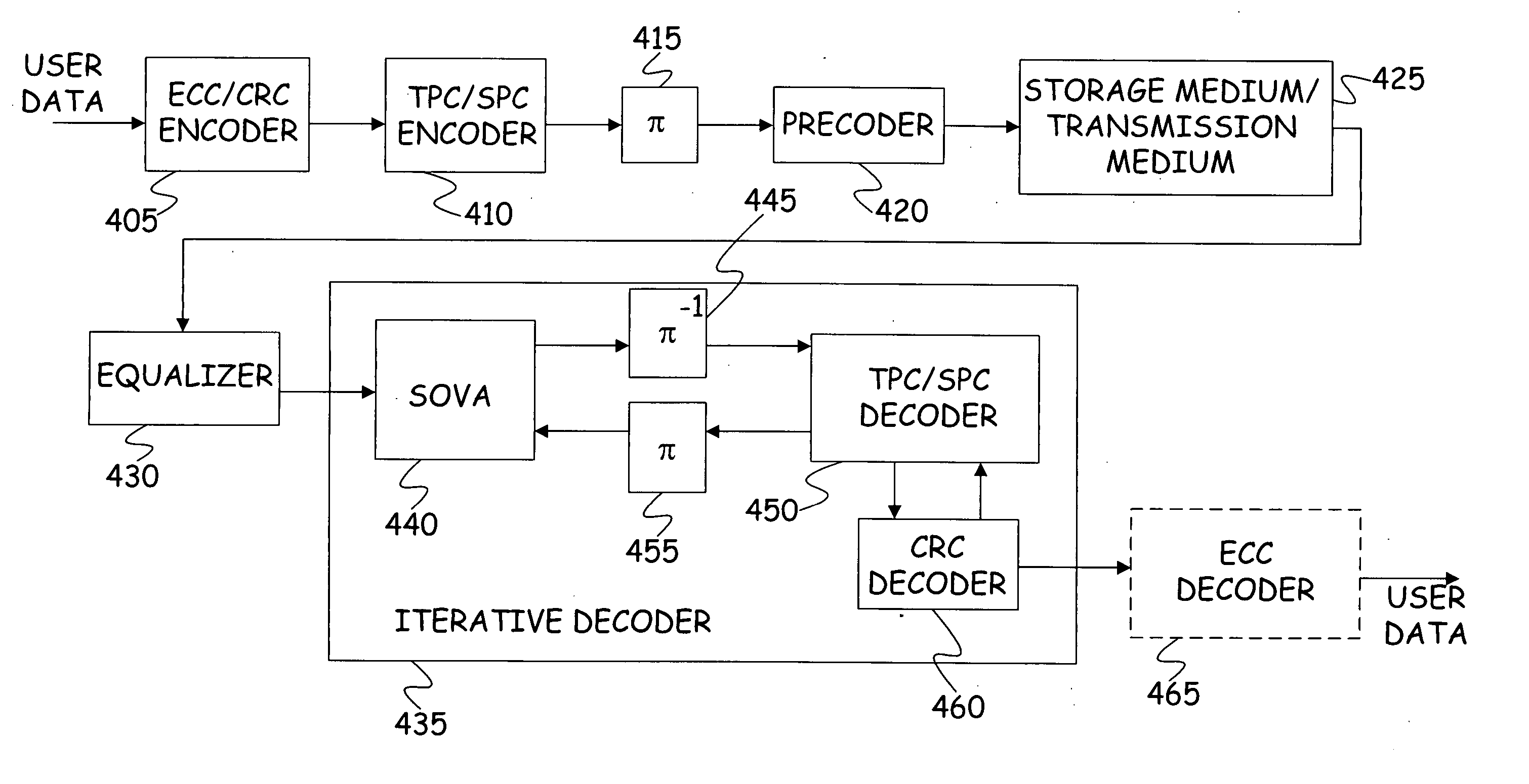

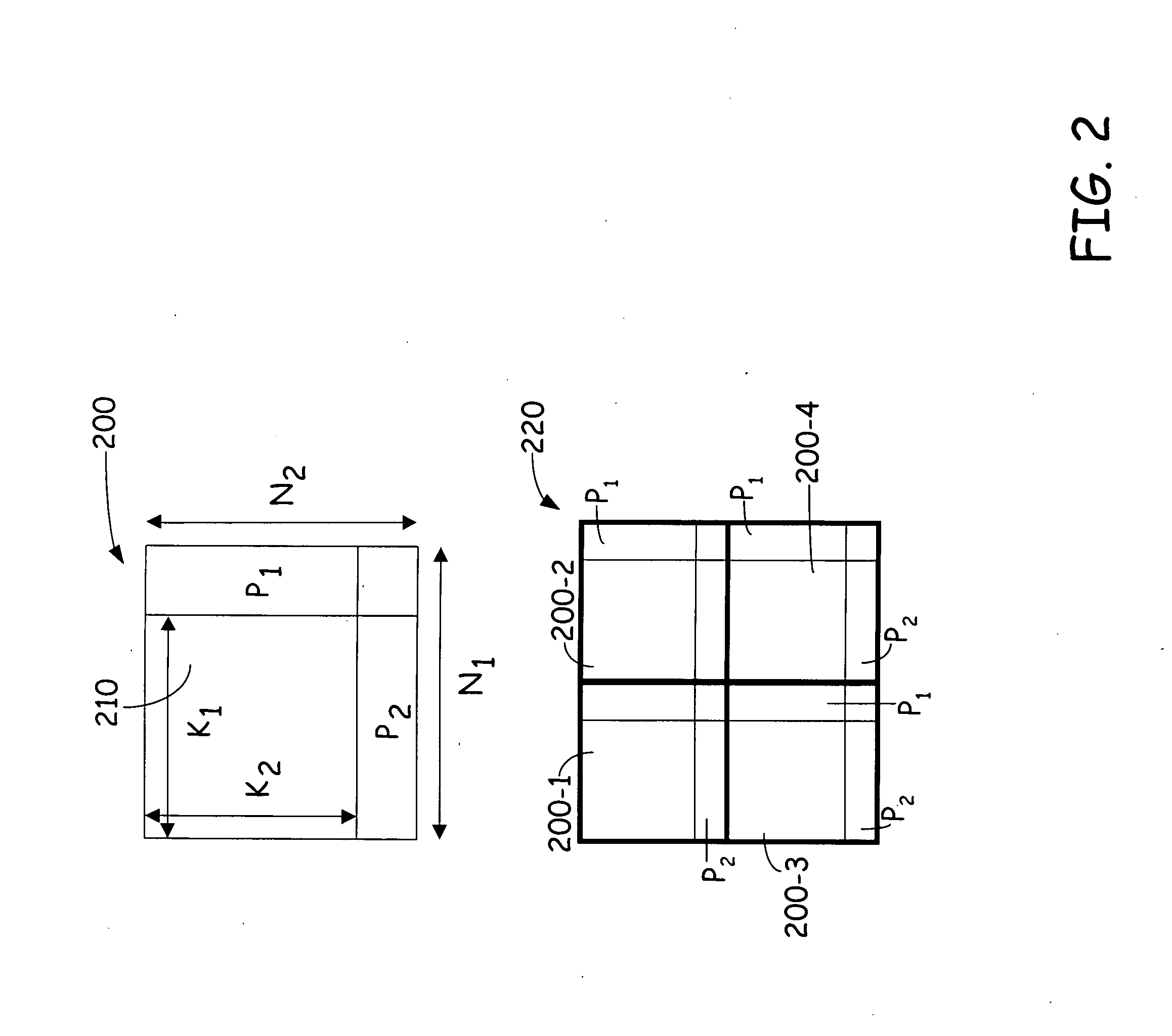

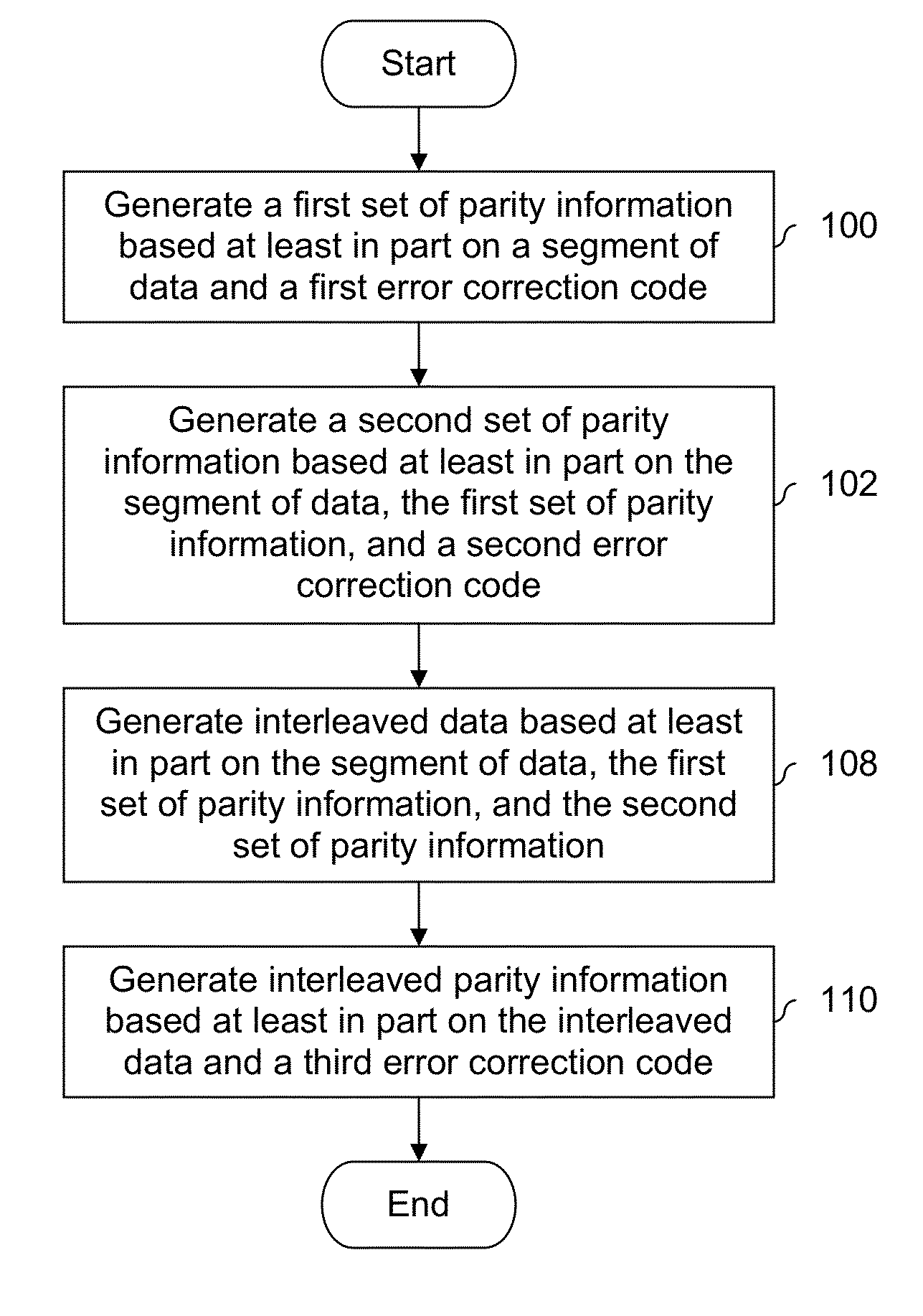

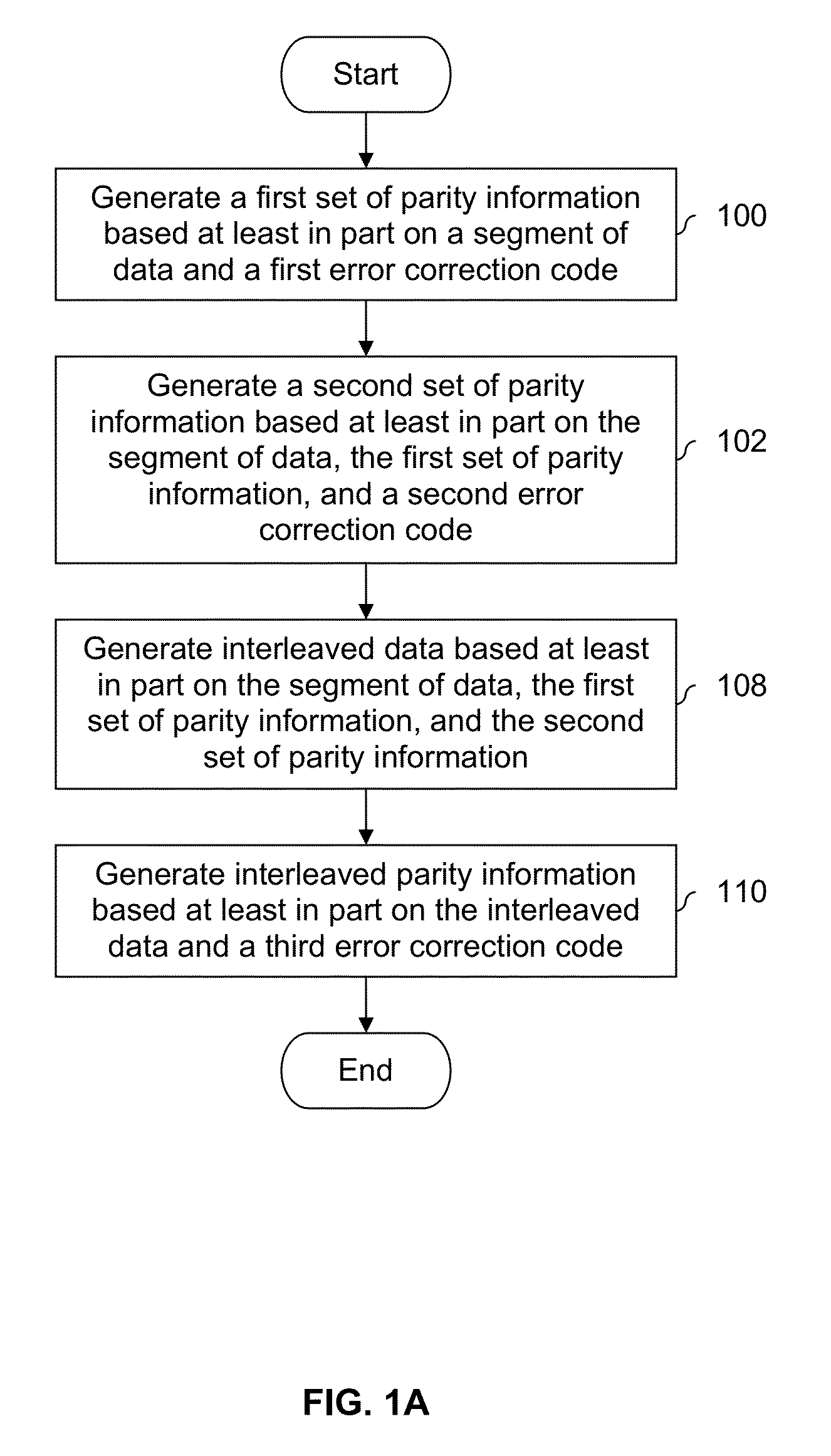

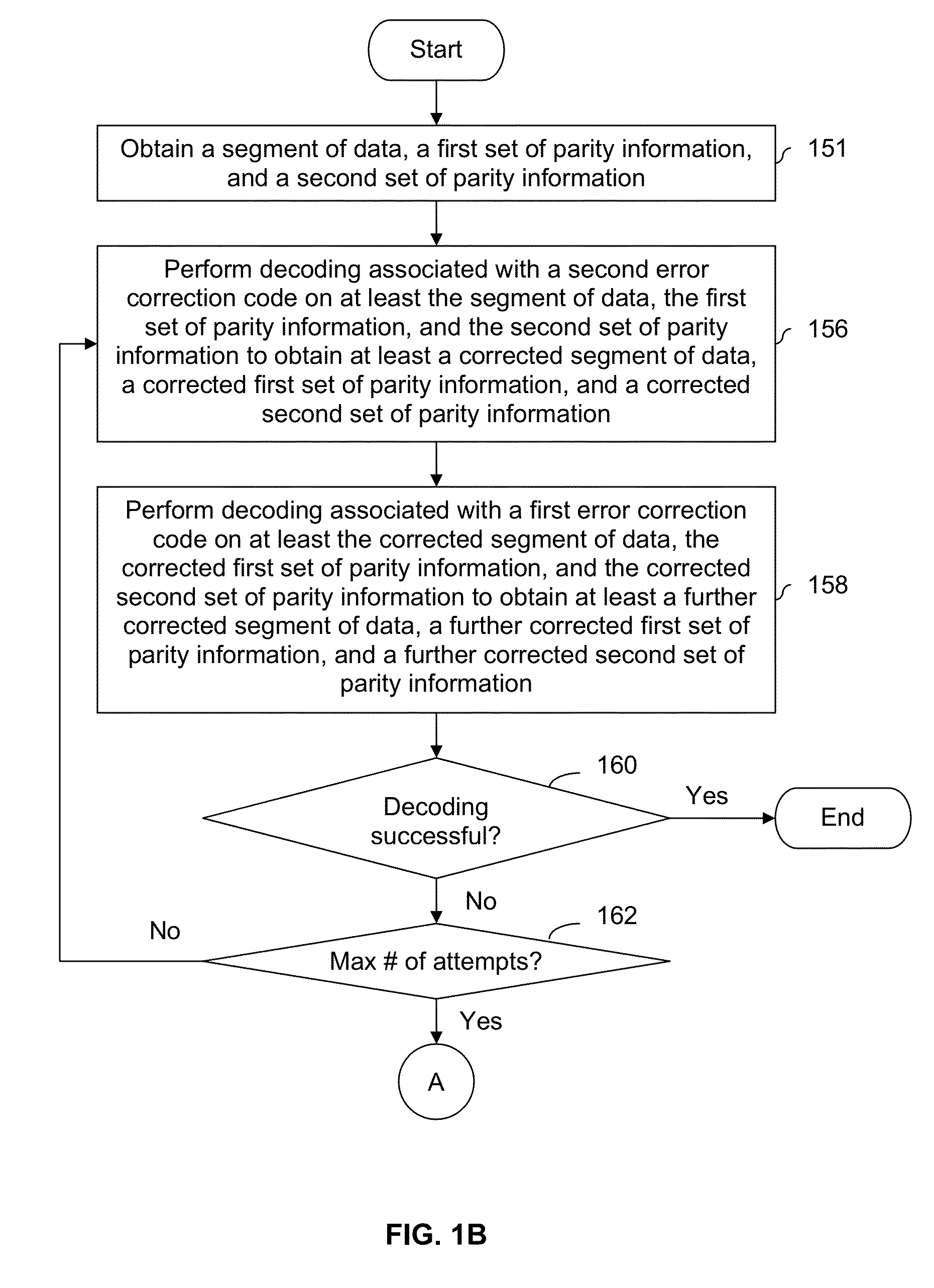

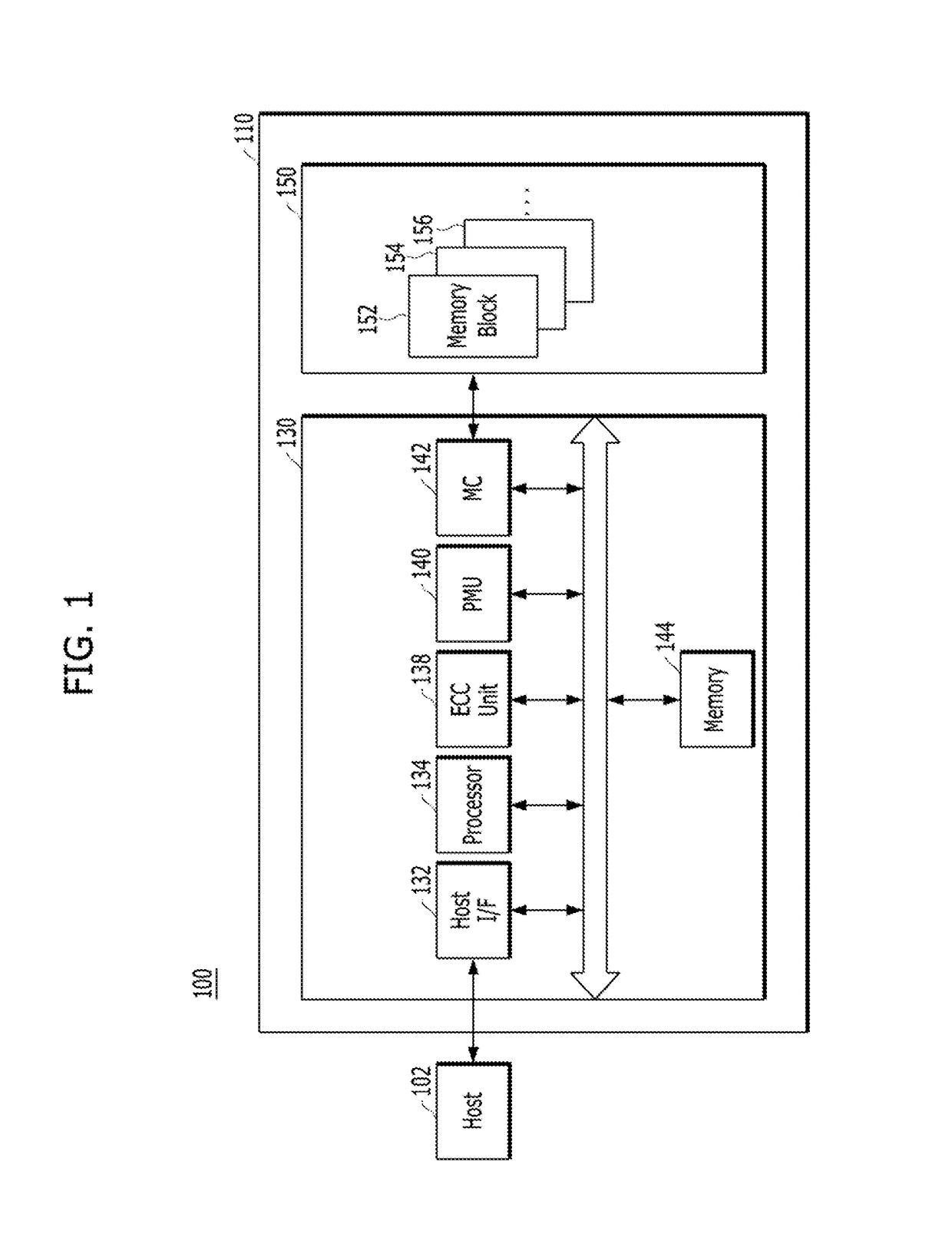

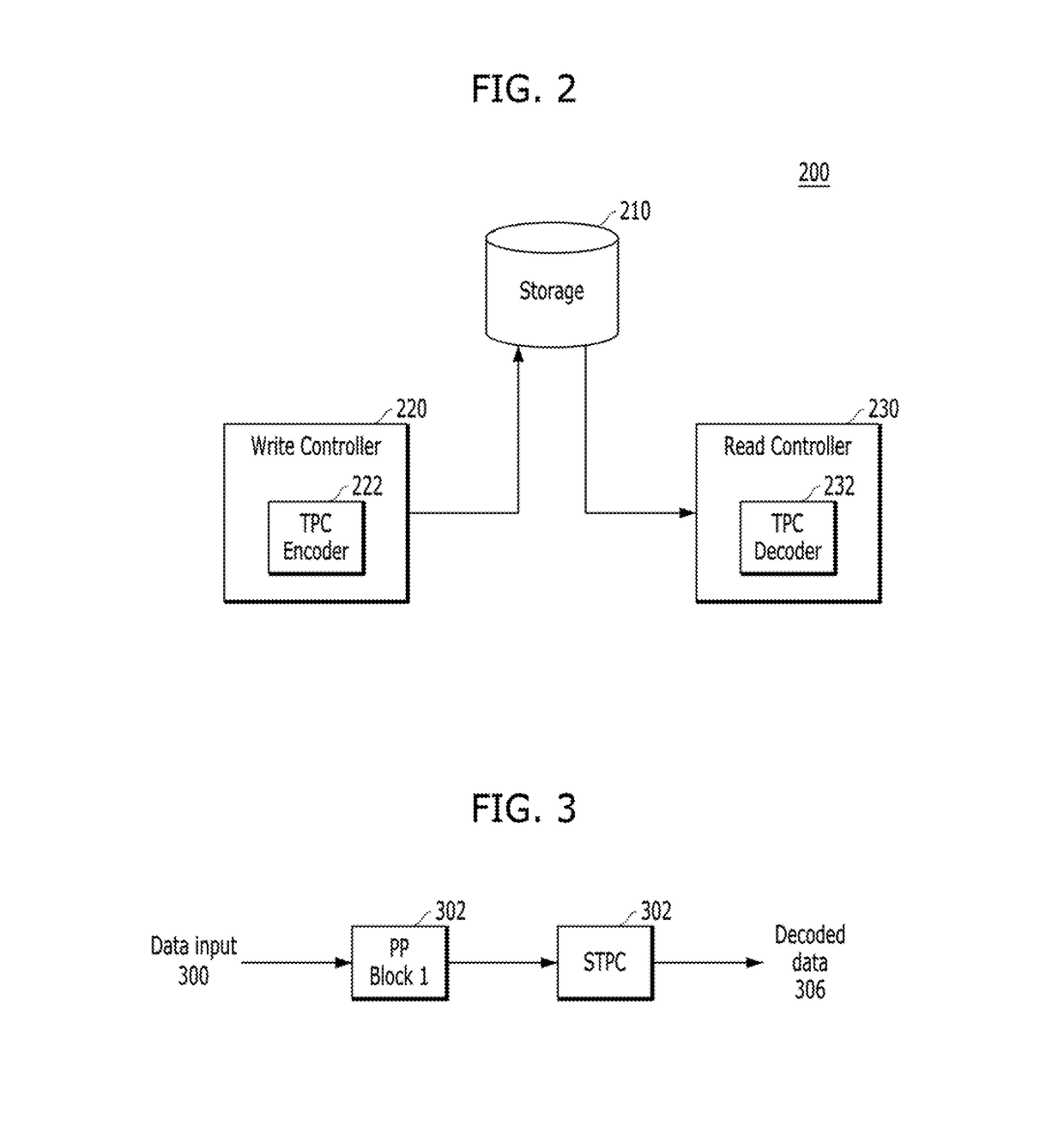

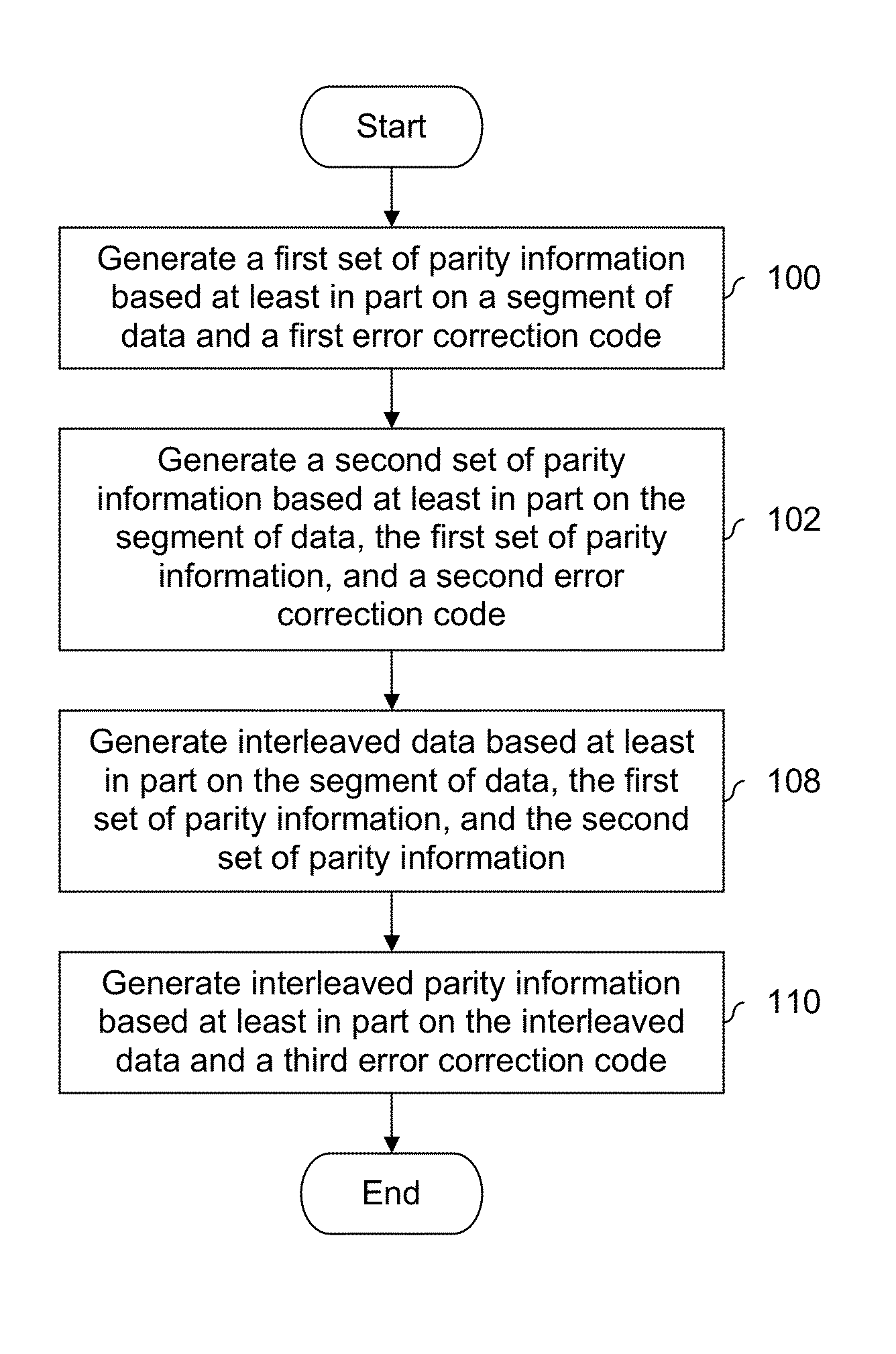

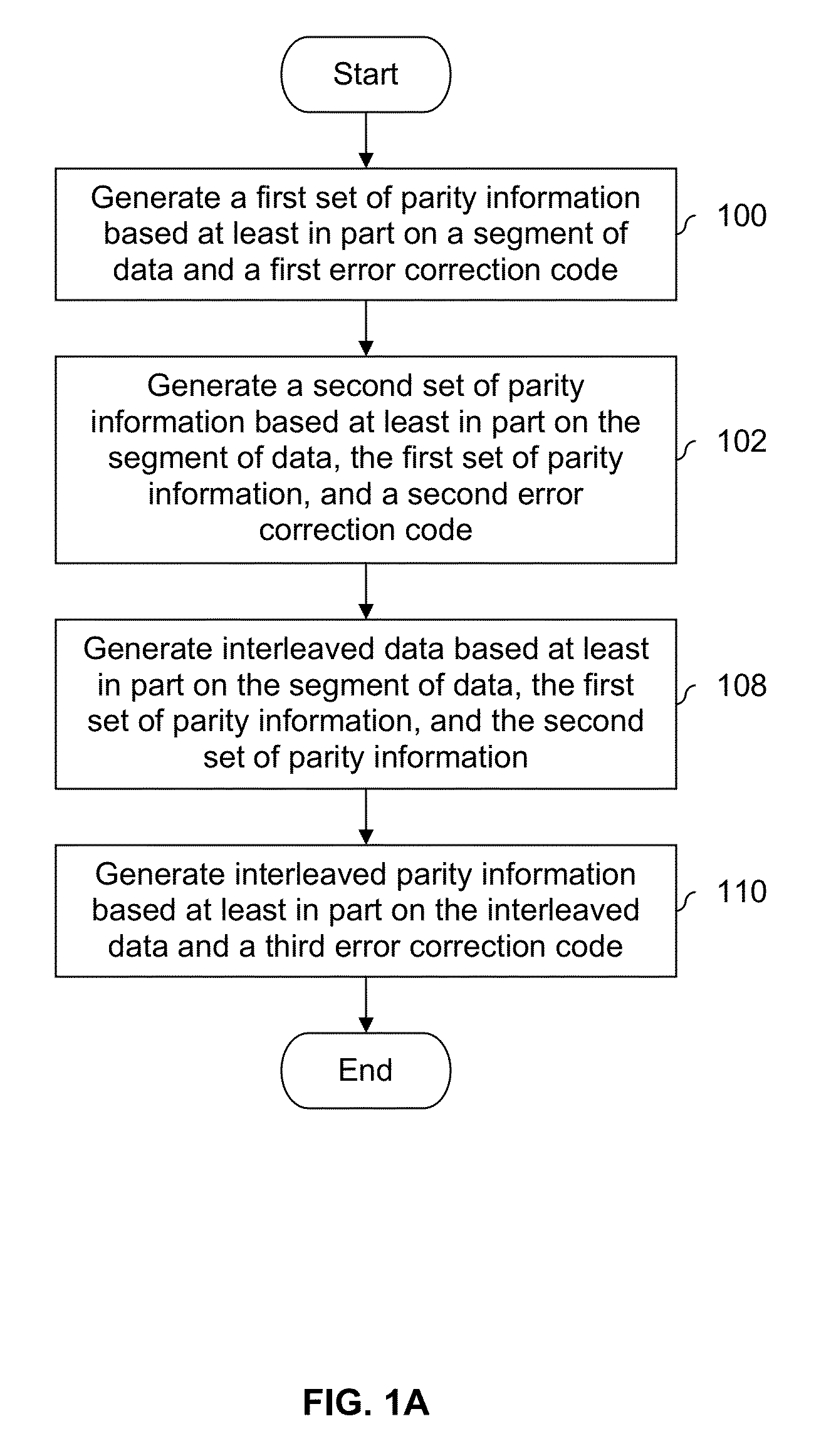

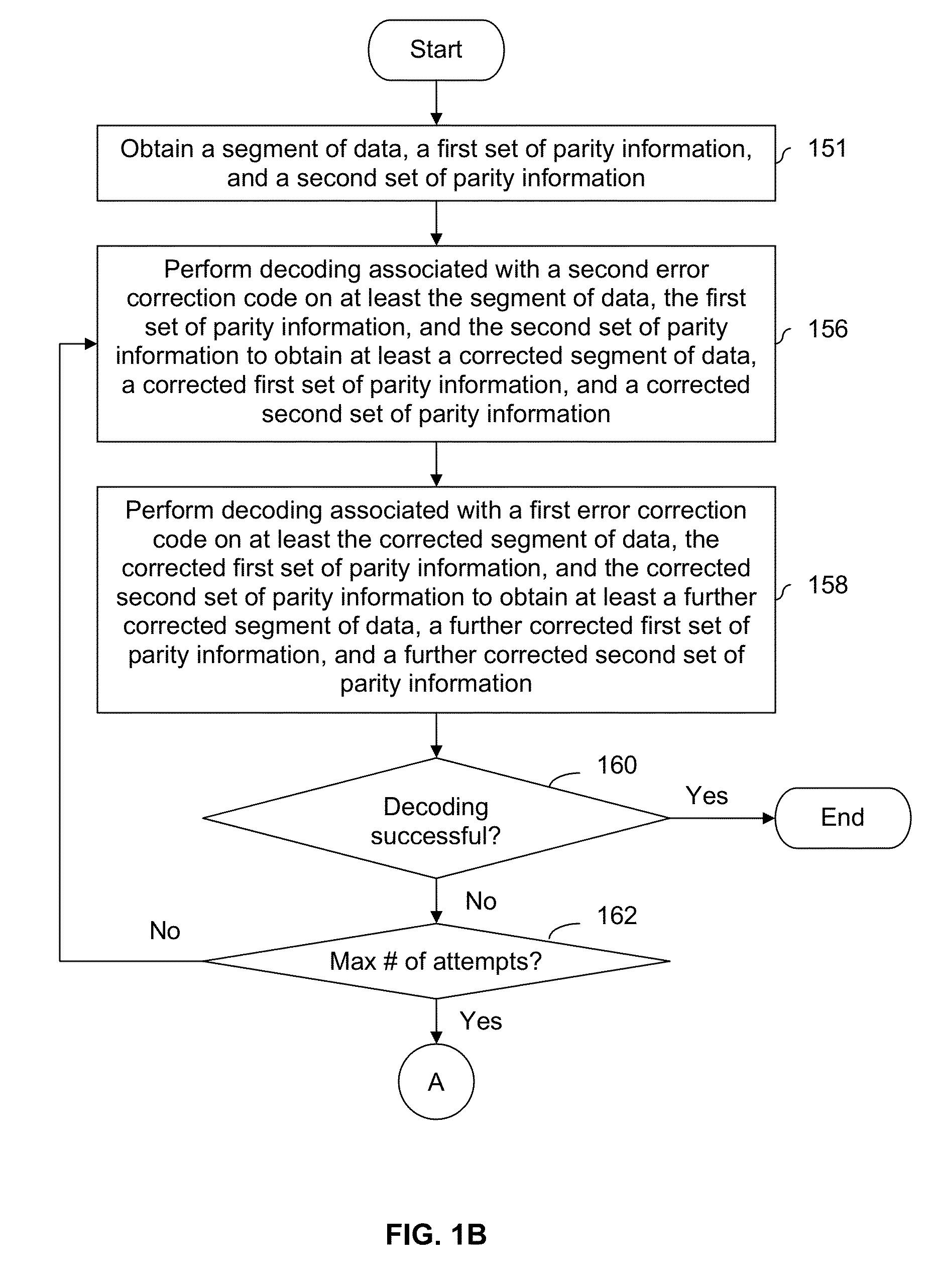

Turbo-product codes (TPC) with interleaving

ActiveUS20140129899A1Code conversionError correction/detection using interleaving techniquesComputer hardwareCorrection code

Decoding associated with a second error correction code and a first error correction code is performed. Ns first and second-corrected segments of data, first sets of parity information, and second sets of parity information are intersegment interleaved to obtain intersegment interleaved data, where the Ns segments of data, the Ns first sets of parity information, and the Ns second sets of parity information have had decoding associated with the first and the second error correction code performed on them (Ns is the number of segments interleaved together). Decoding associated with a third error correction code is performed on the intersegment interleaved data and interleaved parity information to obtain at least third-corrected interleaved data. The third-corrected interleaved data is de-interleaved.

Owner:SK HYNIX MEMORY SOLUTIONS

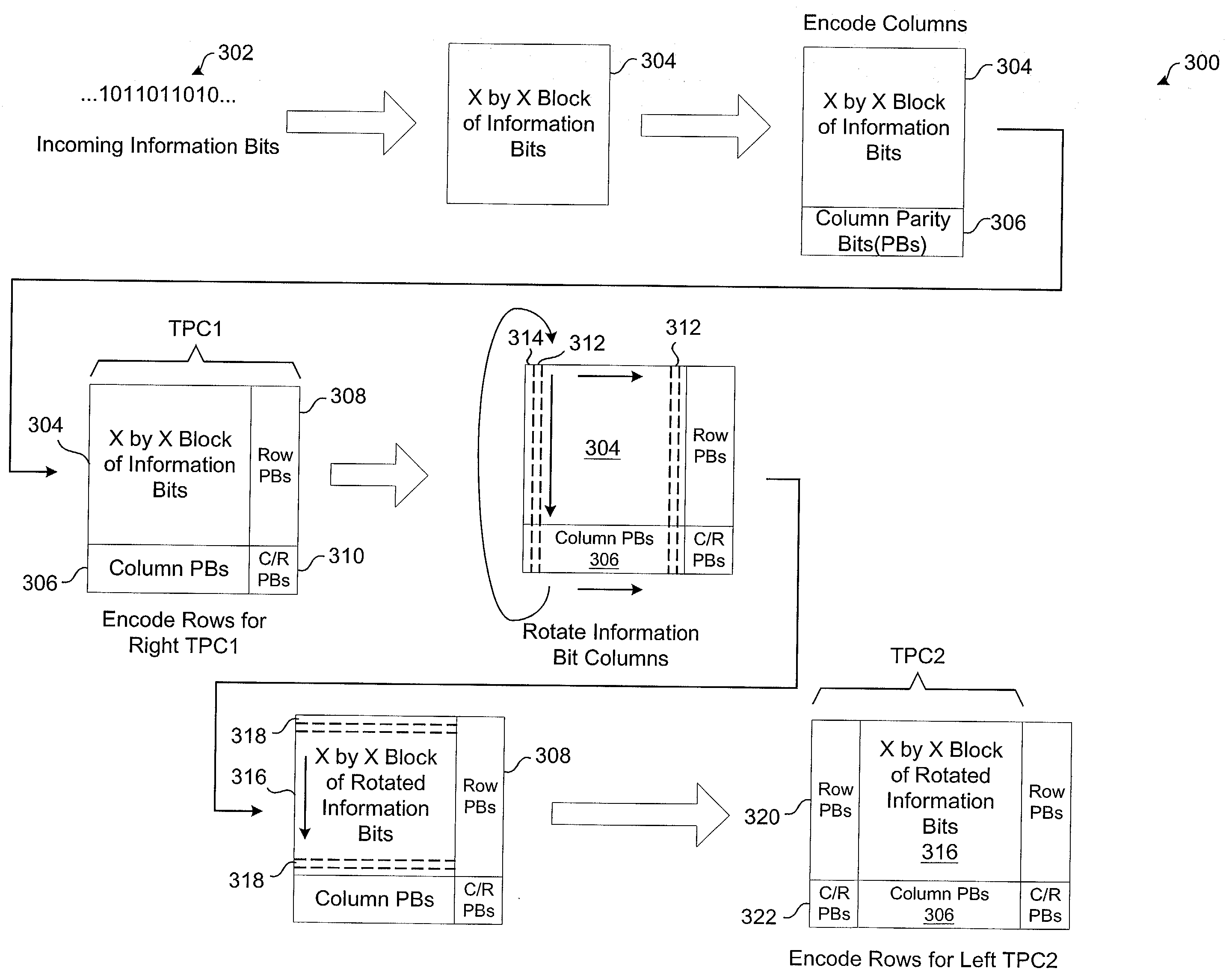

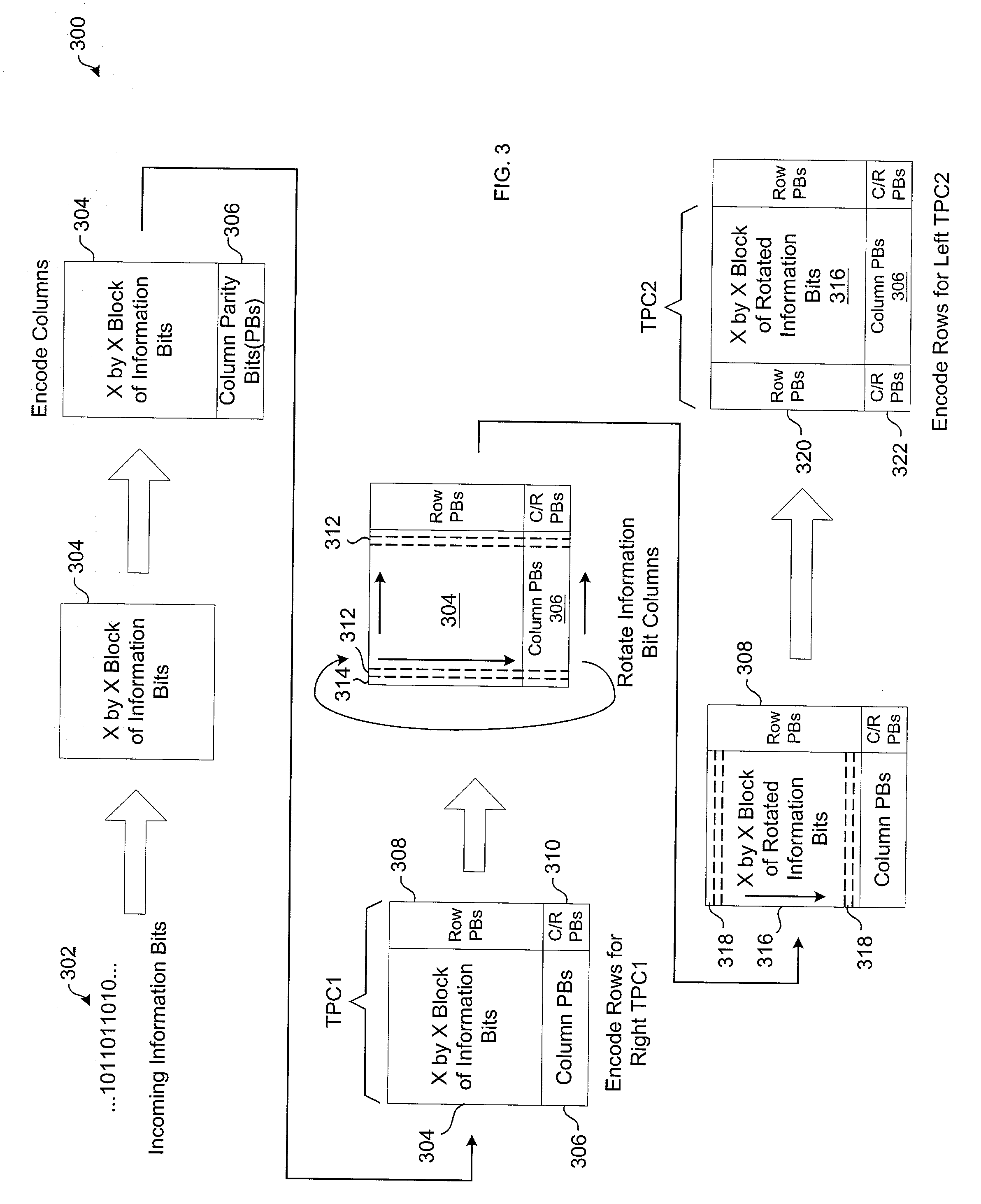

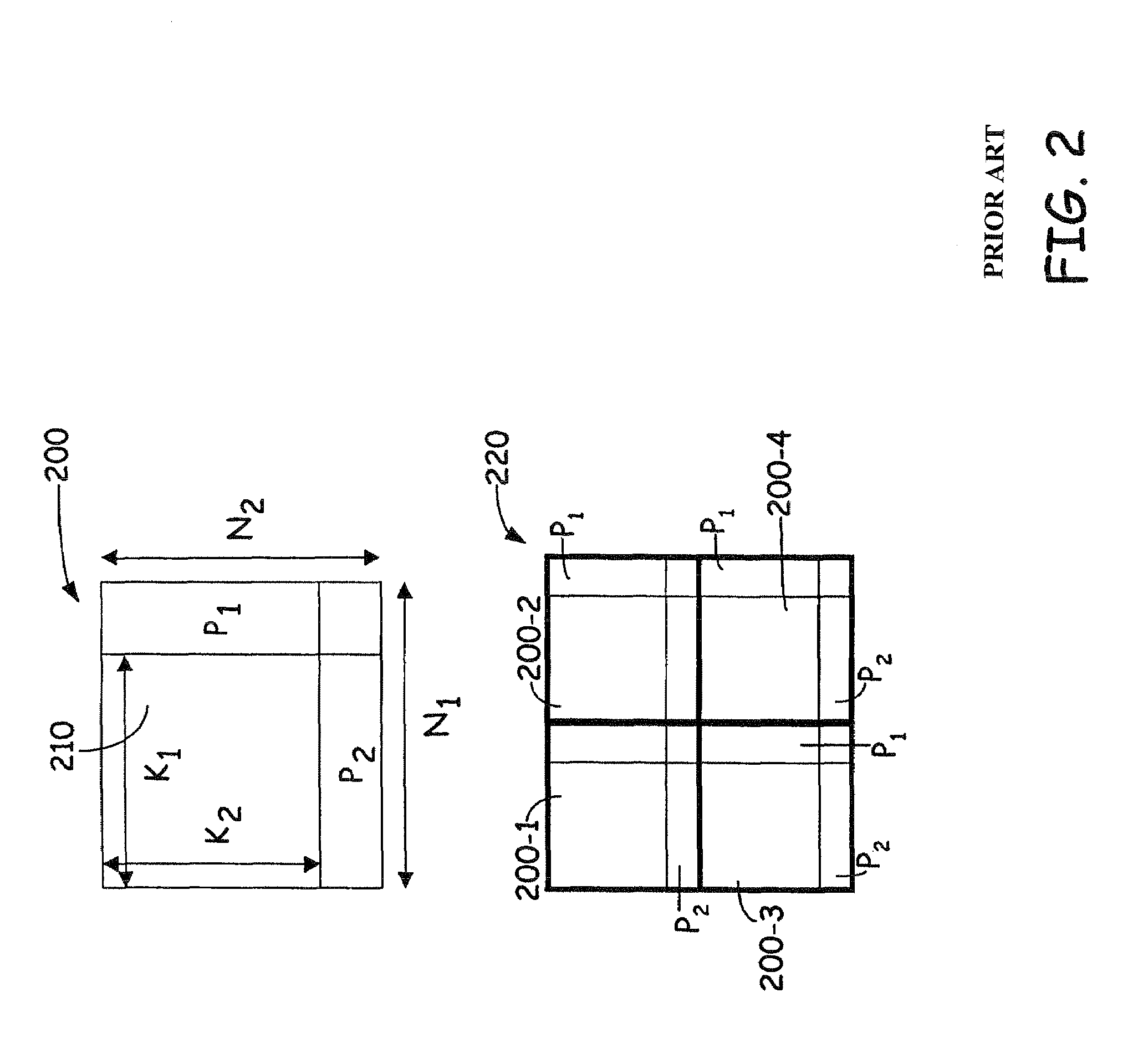

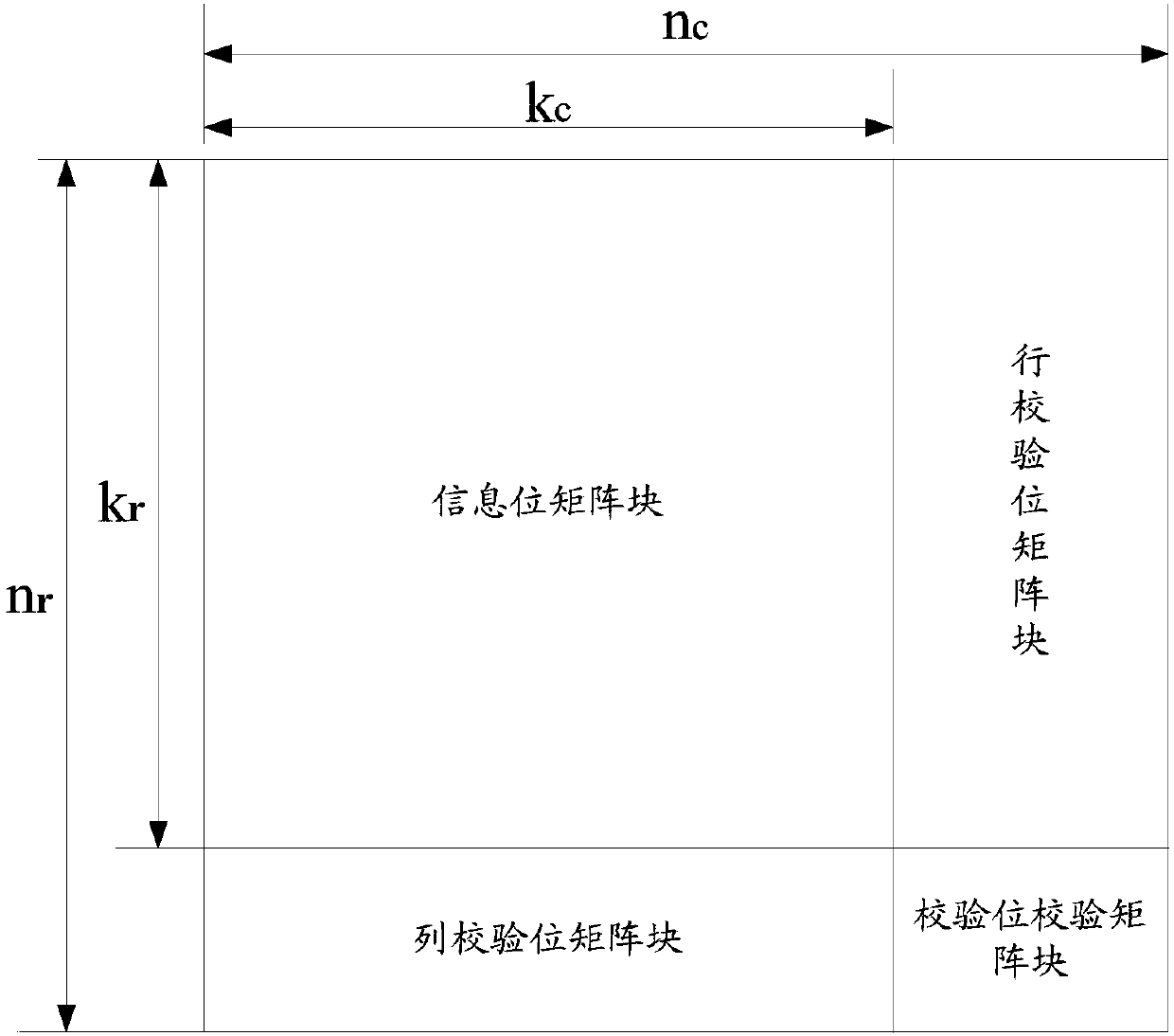

Concatenated turbo product codes for high performance satellite and terrestrial communications

InactiveUS7107505B2Increase minimum distanceError detection/correctionCode conversionArray data structureParallel computing

Architecture for enhancing the encoding / decoding of information of a channel. A stream of incoming information bits are arranged into a first array of information bits. The first array of information bits are processed into a first code of bits, which bits form a plurality of first code words having a minimum distance to neighboring error events. Selected bits of the first code are rearranged into a second array of bits by intermittent successive rotations of the selected bits of the first code. A second code is then generated from the second array of bits to increase the minimum distance to the neighboring error events.

Owner:COMTECH EF DATA

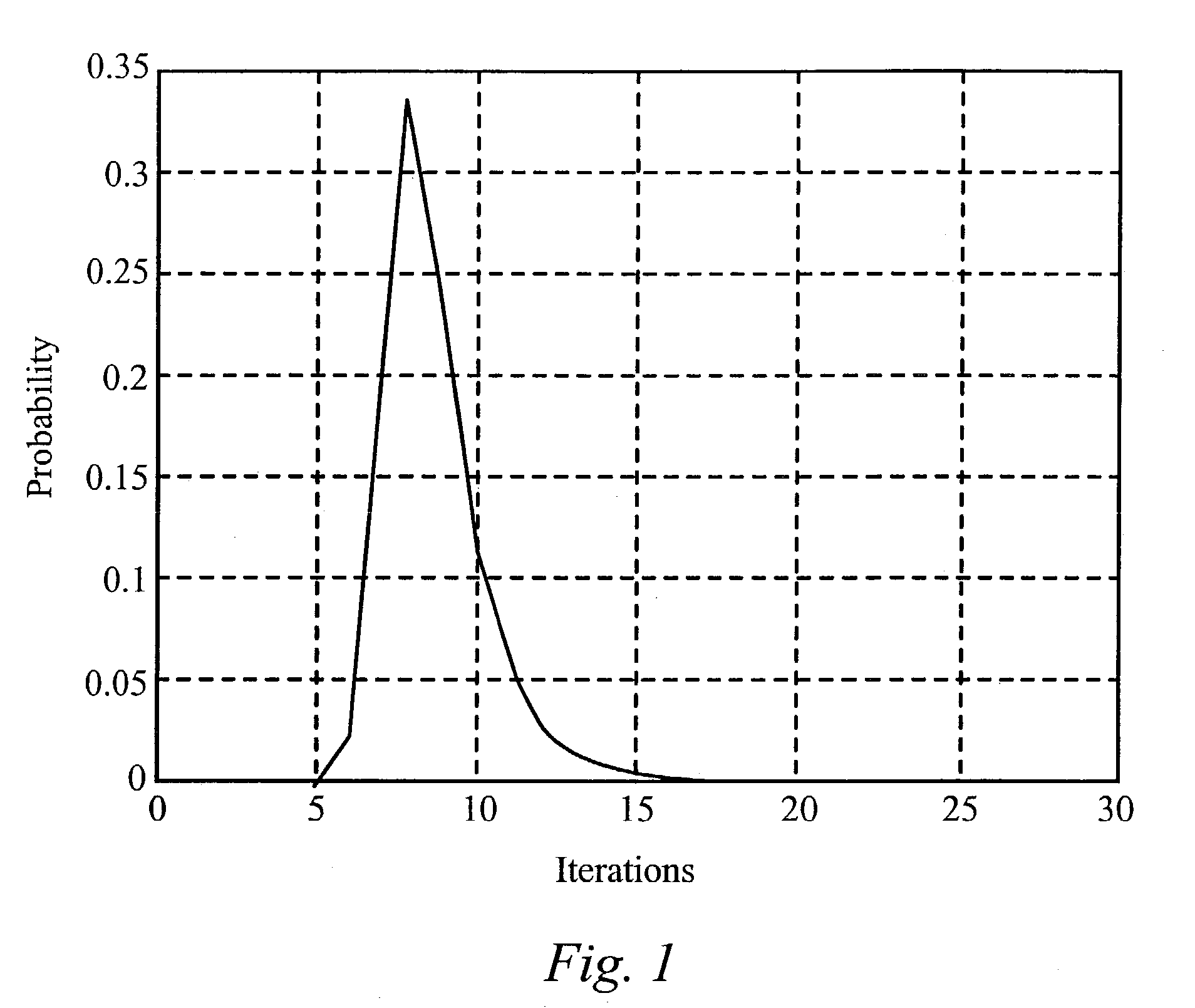

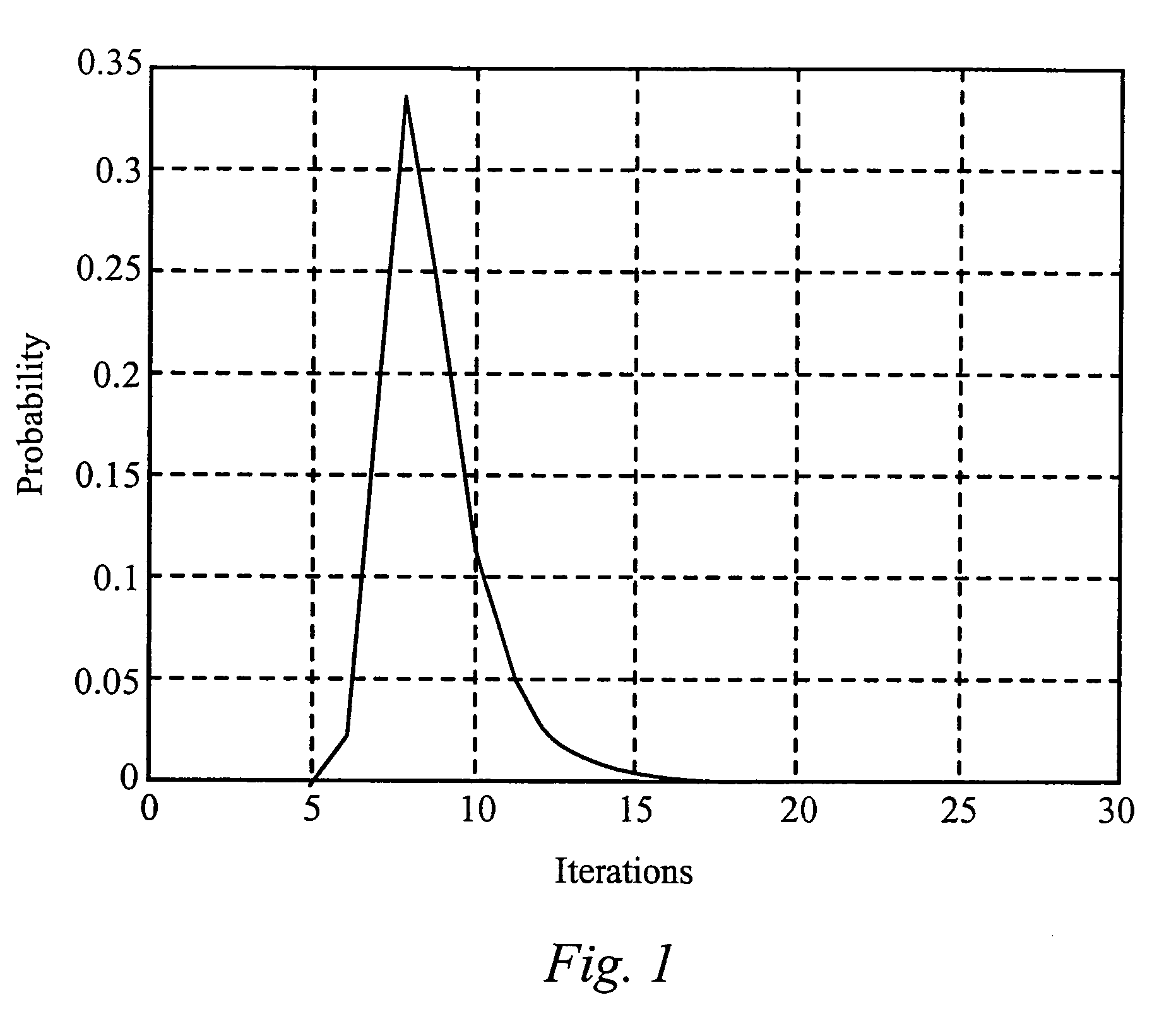

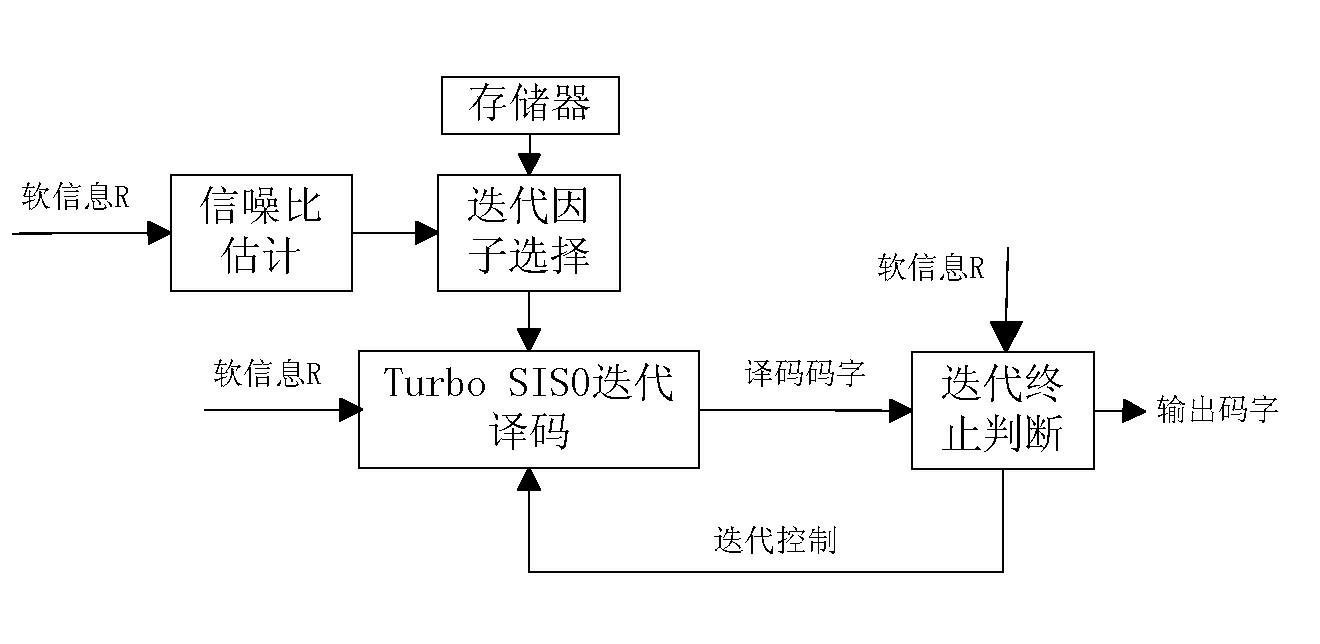

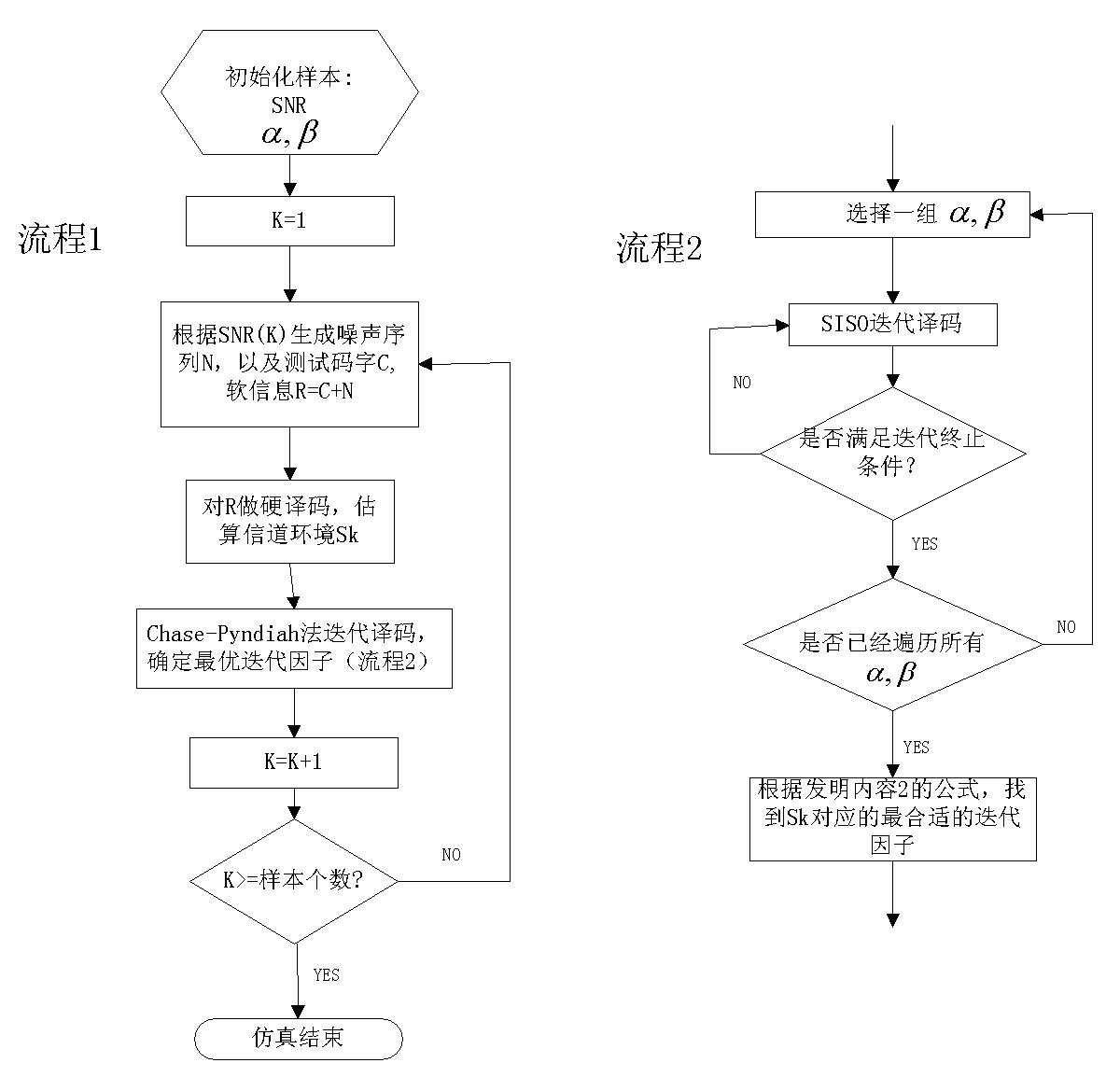

Self-adaptive iterative decoding method for Turbo product codes

ActiveCN102571108AReduce power consumptionExcellent decoding resultError correction/detection by combining multiple code structuresIterative methodSelf adaptive

The invention provides a self-adaptive iterative decoding method for Turbo product codes. The self-adaptive iterative decoding method comprises the steps as follows: channel environment values obtained through simulation and simulation samples of corresponding iterative factors are stored in a storer; the channel environment values S are estimated according to soft information R output by a demodulation terminal; corresponding groups of most suitable iterative factors are selected according to different channel environment values S; then the soft information R and the selected iterative factors are sent into a Turbo code soft-input soft-output (SISO) iterative decoder to be decoded; a code word of the current time of decoding is detected by an iterative stopping judging unit and compared with a code word of the last time of decoding; and when the distance between the code word of the current time of decoding and the last time of decoding is smaller than or equal to an iterative threshold, the decoding is stopped and the code words are output, otherwise iterative decoding is continued. The self-adaptive iterative decoding method has the advantages that suitable iterative factors can be selected according to different channel environments to realize optimal decoding, the iterative times are selected in a self-adaptive manner, and power consumption of a receiver is effectively reduced.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

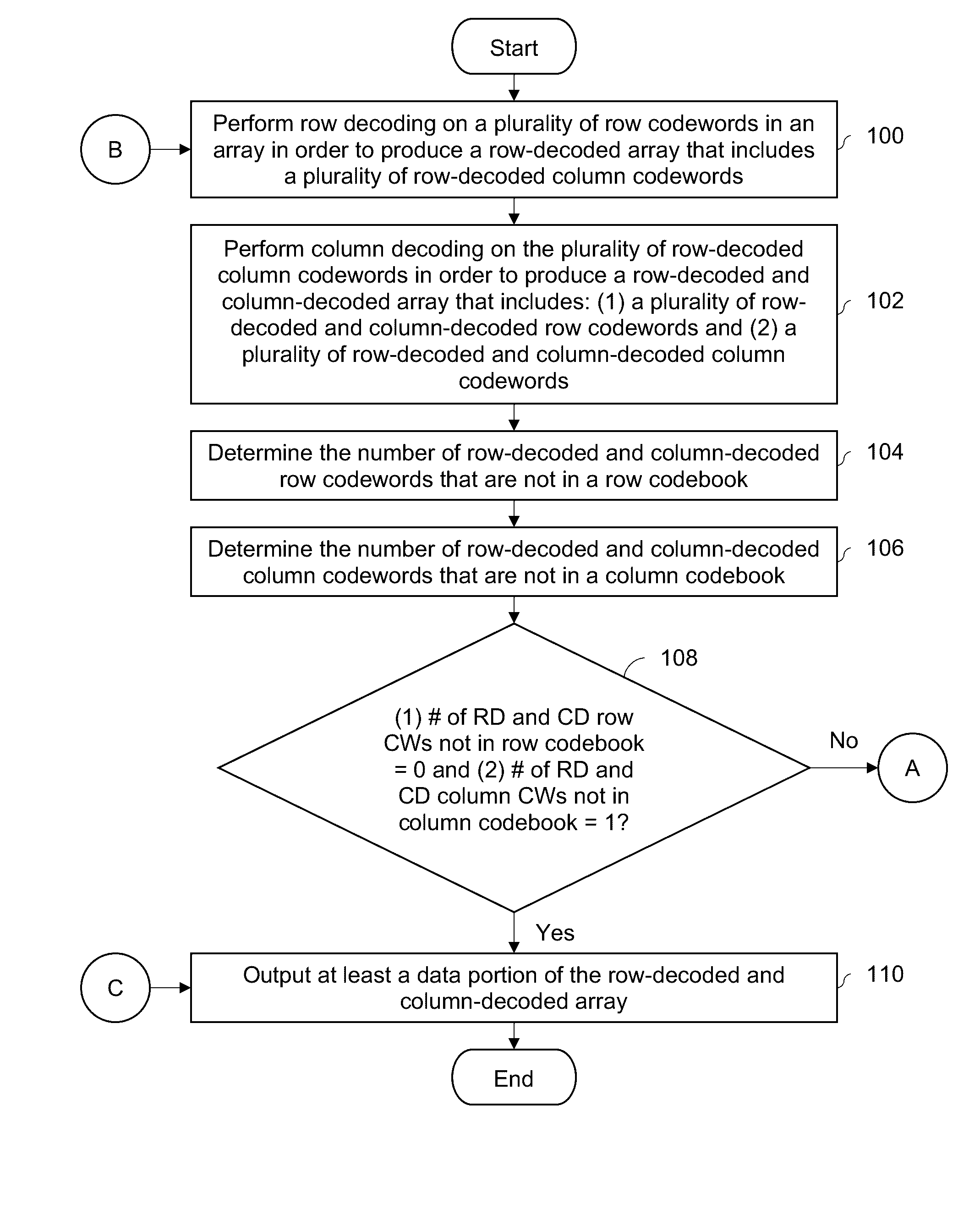

Stopping rules for turbo product codes

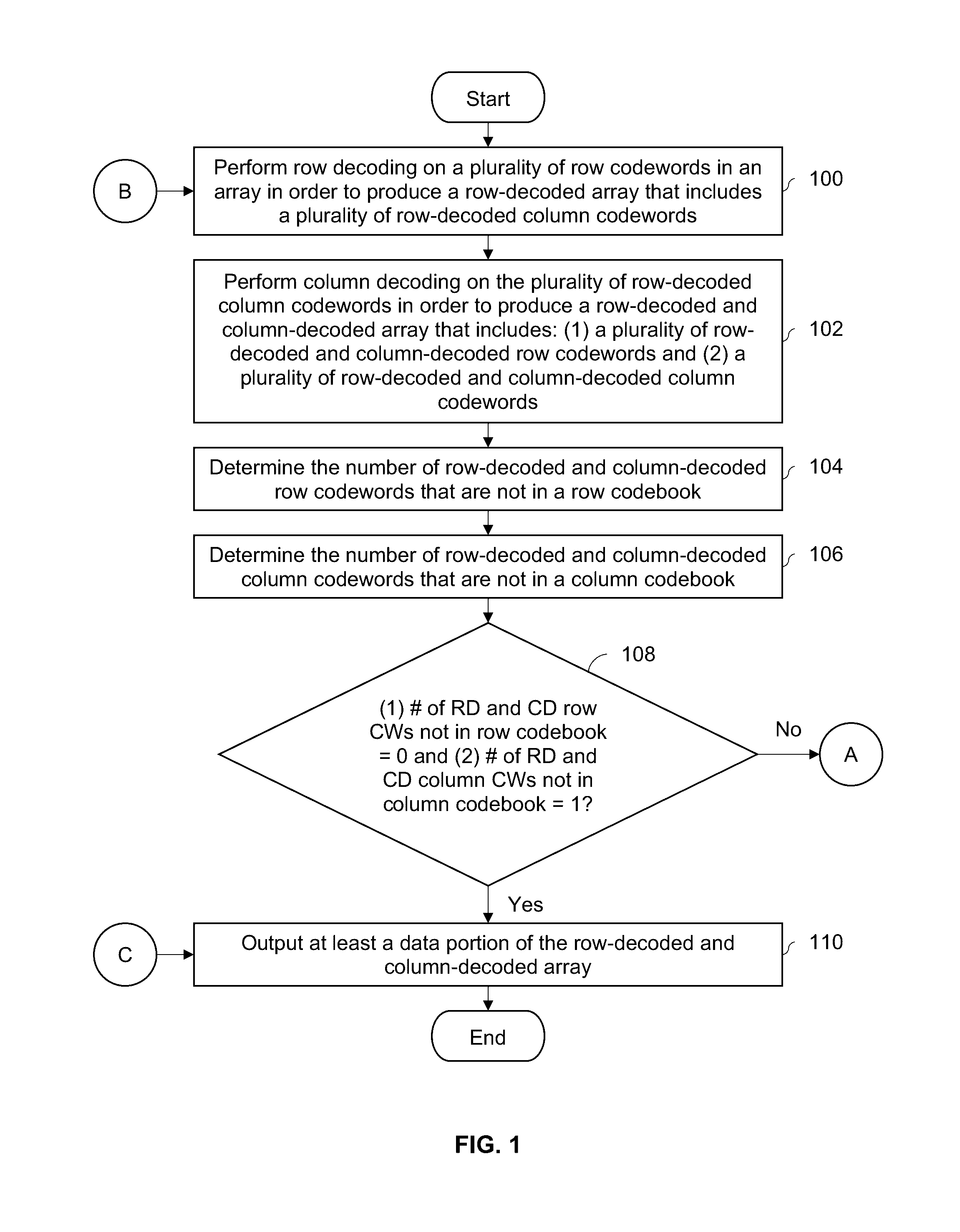

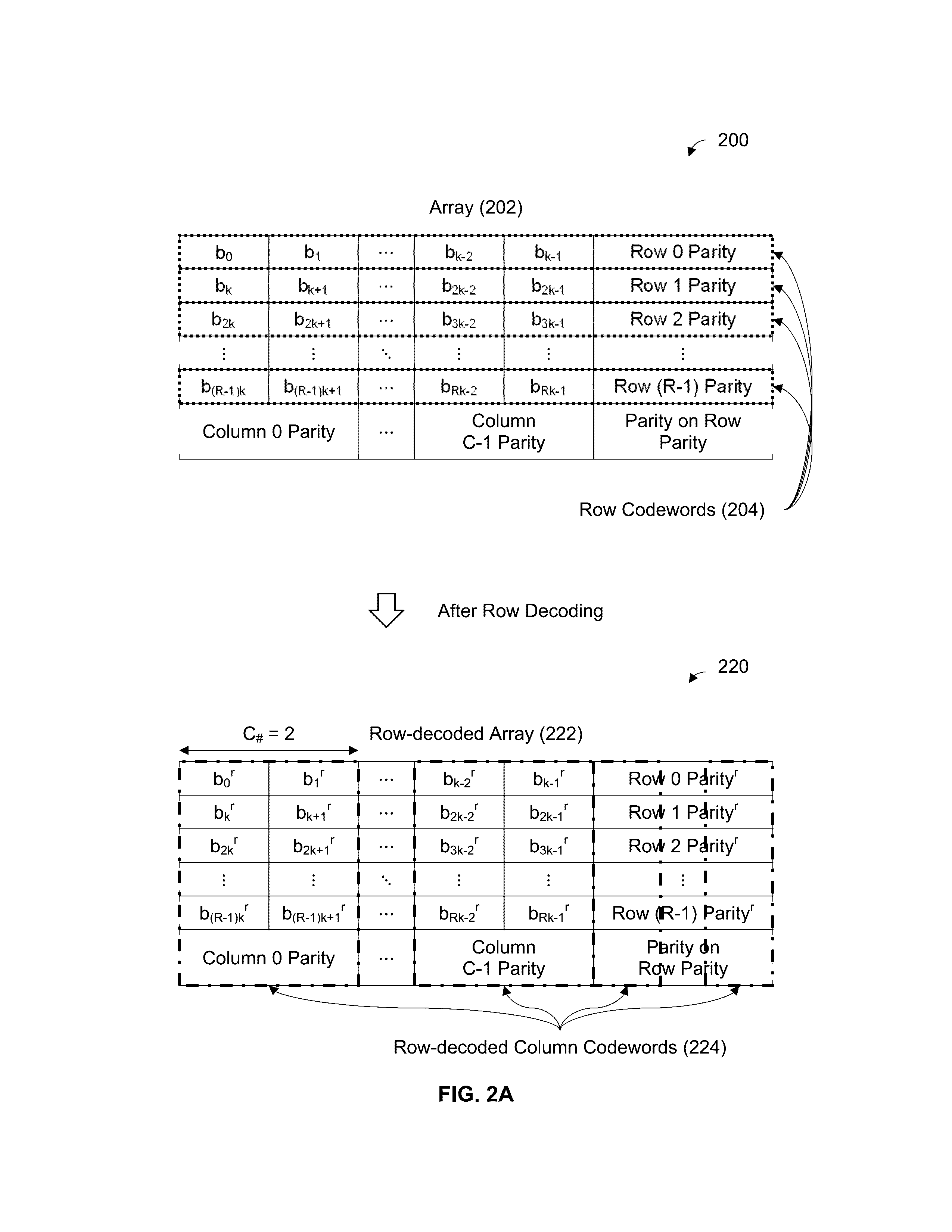

Row decoding is performed on row codewords in an array in order to produce a row decoded array that includes row decoded column codewords. Column decoding is performed on the row decoded column codewords in order to produce a row and column decoded array that includes row and column decoded row codewords and row and column decoded column codewords. The number of row and column decoded row codewords that are not in a row codebook is determined and the number of row and column decoded column codewords that are not in a column codebook are determined. If the number not in the row codebook equals 0 and the number not in the column codebook equals 1, at least a data portion of the row and column decoded array is output.

Owner:SK HYNIX INC

FPGA implementing method for Turbo product code optimized encoding and decoding algorithm

ActiveCN101483443AImprove encoding performanceHigh data rateError preventionOther error detection/correction/protectionFpga implementationsRandom access memory

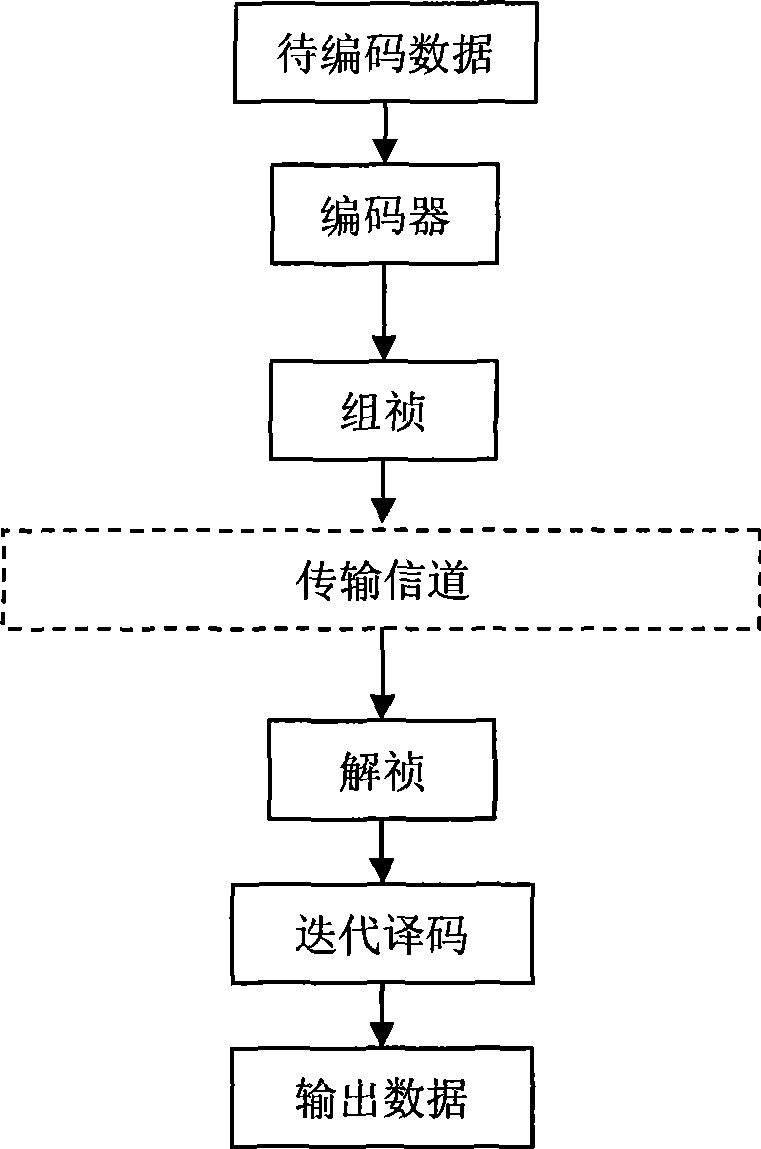

An FPGA realization method for optimizing coding / decoding algorithm with Turbo product code comprises the following steps: 1) coding, after the data to be coded is transmitted to a random access memory, reading in by the coder from the random access memory line by line or row by row, executing lien or row coding with Turbo product code, after line coding or row coding is finished, coding row by row or line by line, writing the coded data into an output Ram, when the output Ram is full, outputting frame header, then reading out the whole block of data in the output Ram, complementing the clock gap from the completion of data output to the output of next data block; and shortening the information bit according to the requirement of code rate; 2) framing, framing and transmitting the output data after coding; and 3) decoding, de-framing and decoding the received data. The invention can be flexibly configured for aiming at different application requirements. A higher data speed can be obtained through parallel using a plurality of decoding units. The FPGA realization method can be used for high-speed data transmission.

Owner:CHINESE AERONAUTICAL RADIO ELECTRONICS RES INST

Turbo product code implementation and decoding termination method and apparatus

A method of decoding a turbo product code (TPC) code word comprises iteratively decoding the TPC code word using an iterative decoder. The method further comprises terminating the iterative decoding when the TPC code word satisfies a cyclic redundancy check (CRC). The TPC code word can include a plurality of square code blocks of user data, with CRC data bits appended to one of the plurality of code blocks instead of replacing user data within the code blocks. Apparatus for implementing the method are also provided.

Owner:SEAGATE TECH LLC

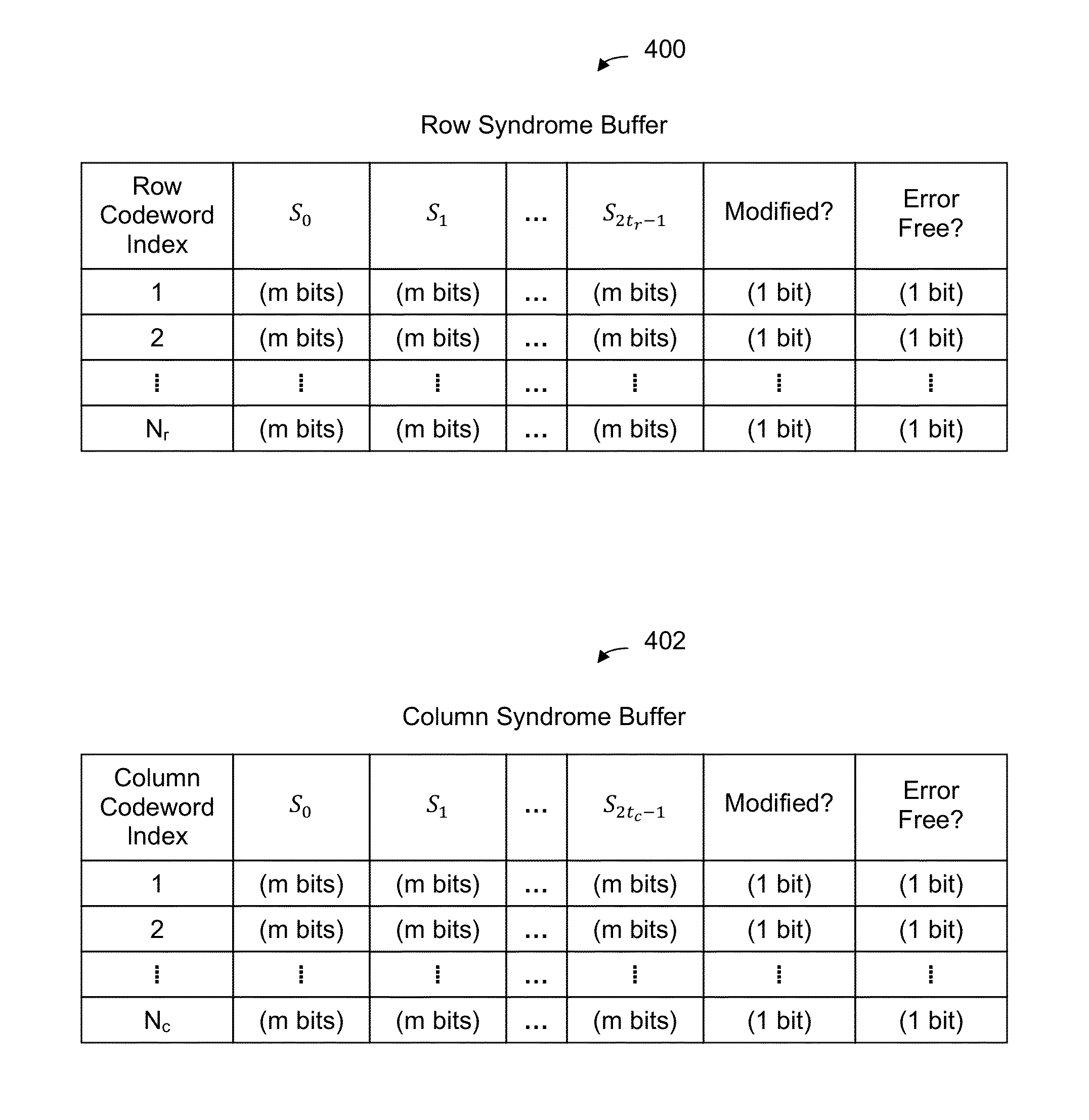

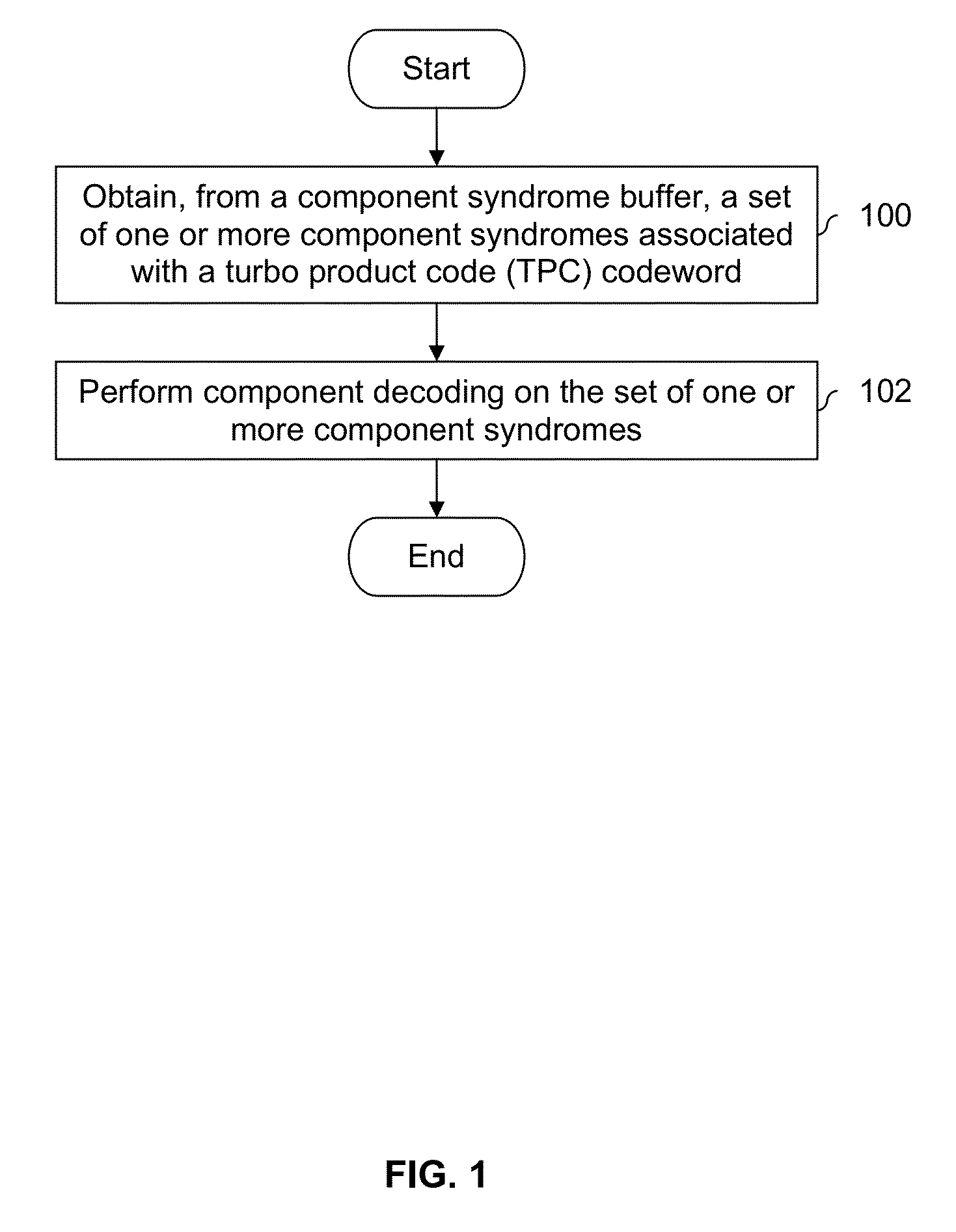

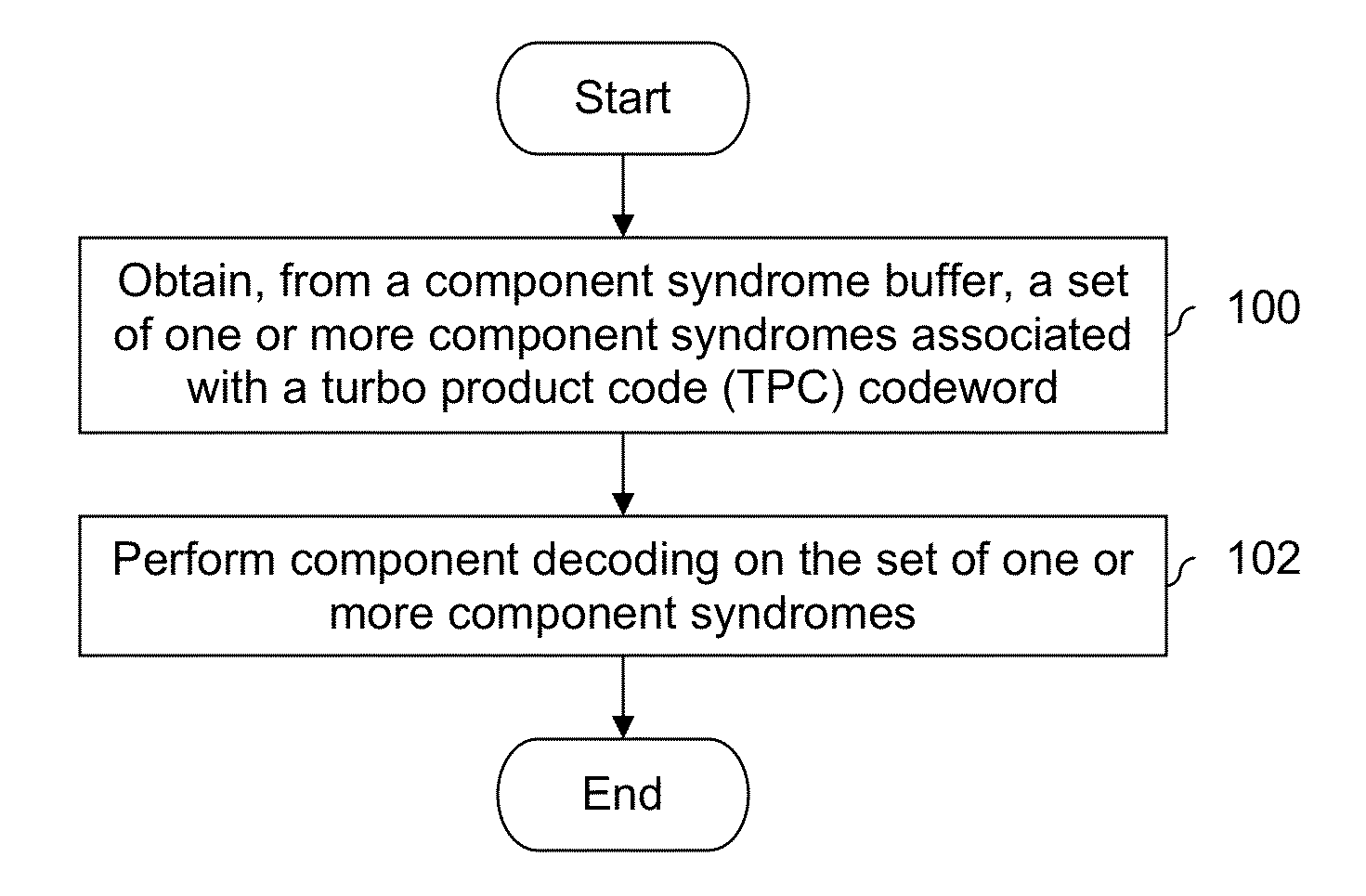

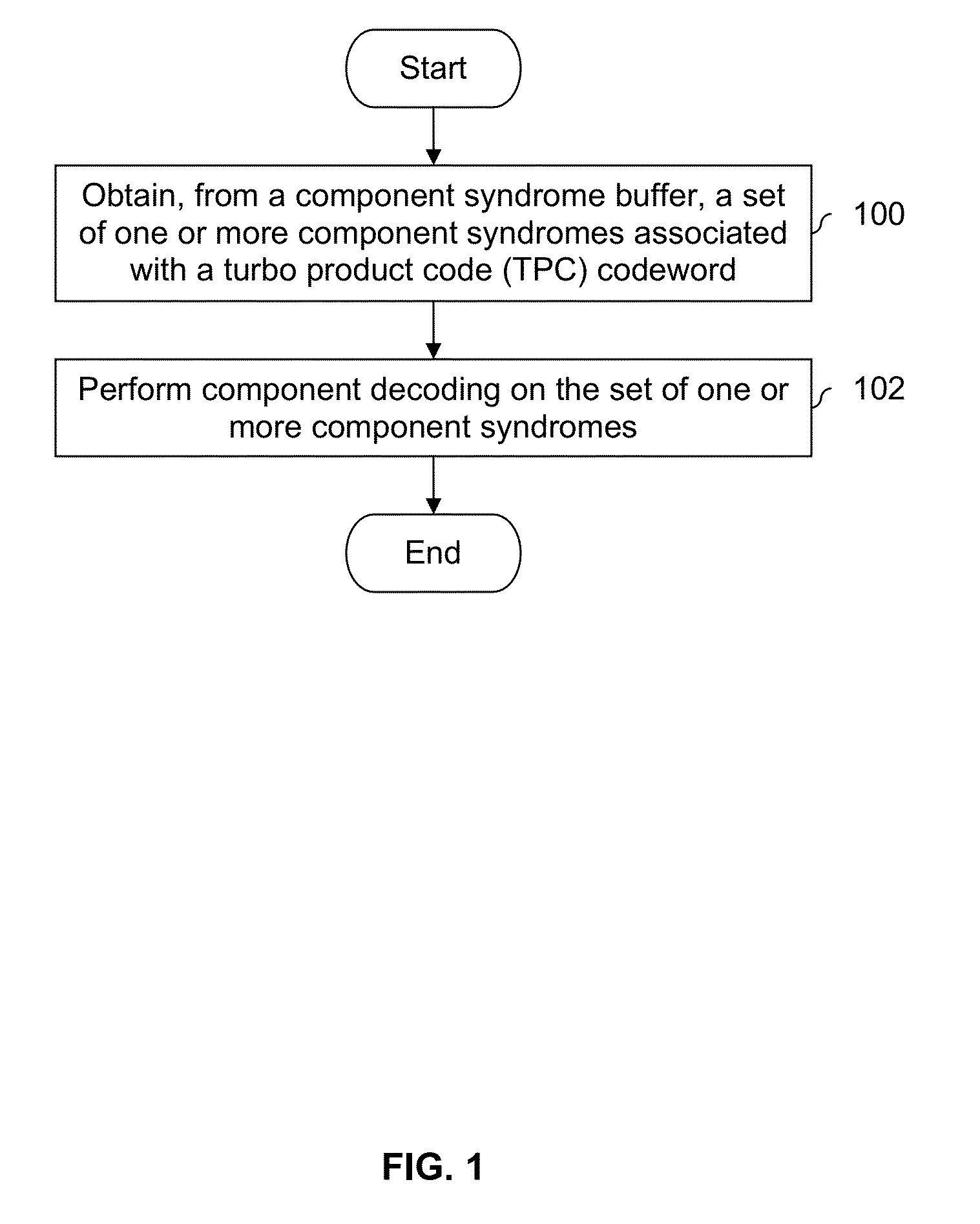

Syndrome tables for decoding turbo-product codes

ActiveUS9391641B2Code conversionError correction/detection by combining multiple code structuresSoftware engineeringTurbo product codes

Owner:SK HYNIX INC

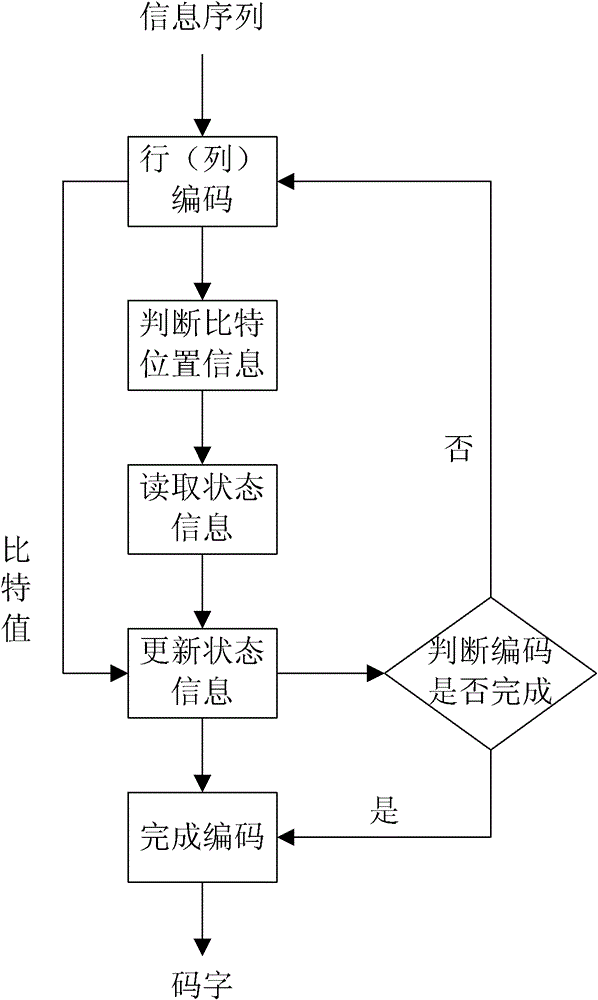

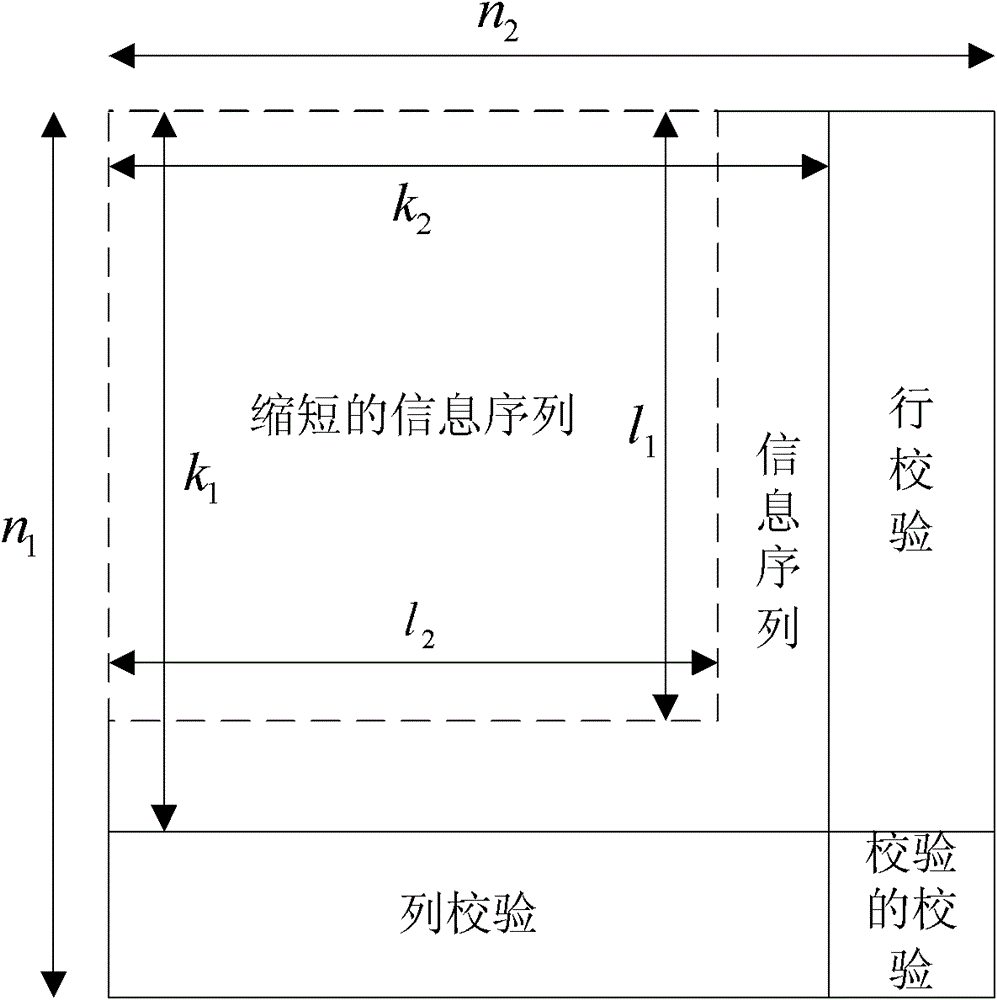

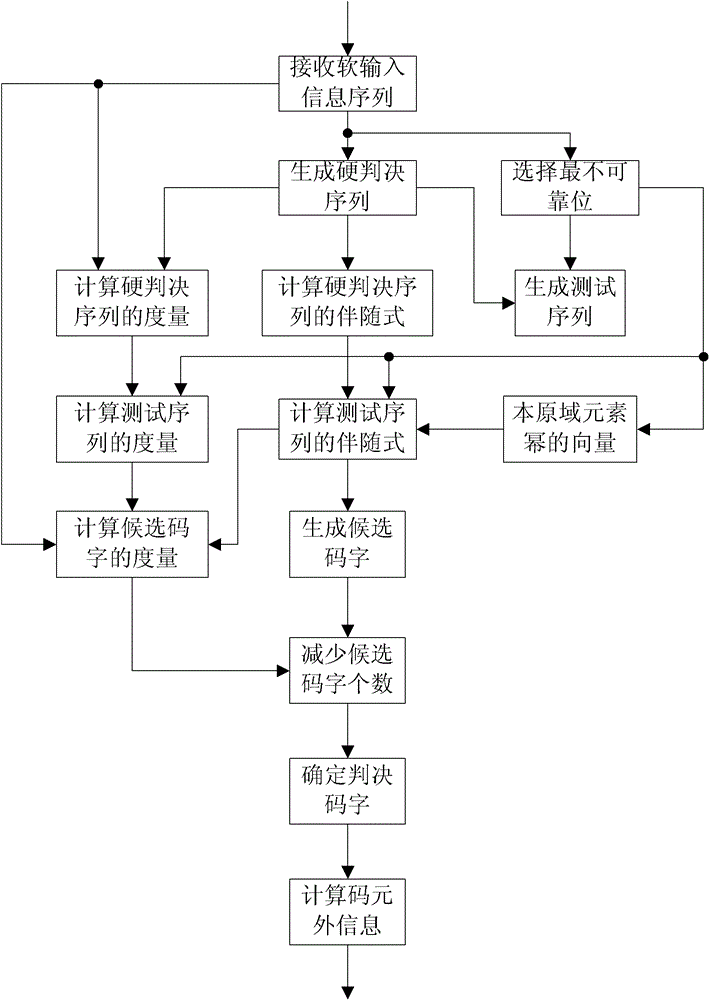

Encoding and decoding methods for shortening Turbo product code

InactiveCN101958720BIncrease storage resourcesImprove data throughputError correction/detection by combining multiple code structuresParallel encodingTheoretical computer science

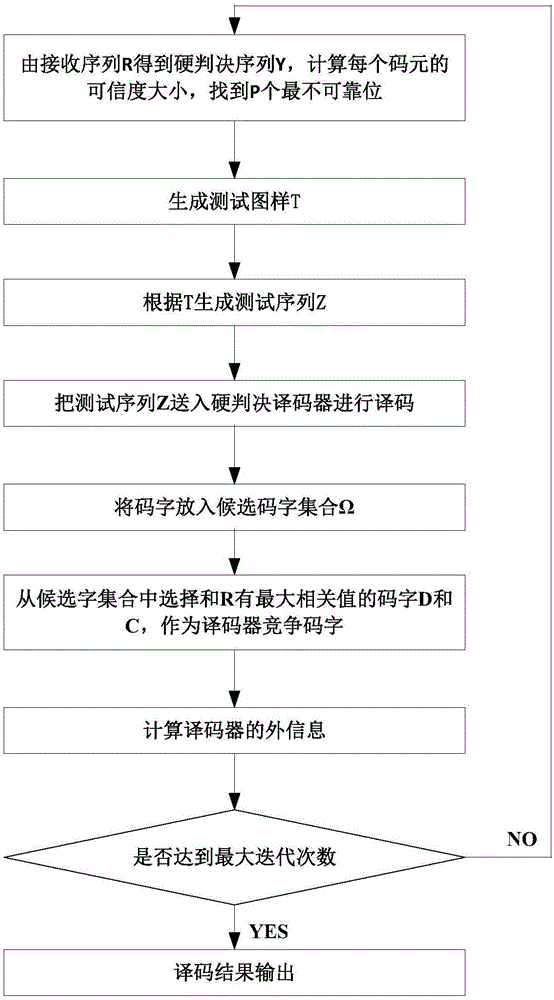

The invention relates to encoding and decoding methods for shortening a Turbo product code. The encoding method comprises the following steps of: performing row or column encoding on an information sequence to be encoded; performing parallel encoding on code words of row or column component codes generated by the row or column encoding; and judging whether the encoding is finished. The decoding method comprises the following steps of: generating a hard decision sequence of a soft-input information sequence; selecting the least reliable bits in the soft-input information sequence; generating a test sequence according to the hard decision sequence and the least reliable bits; decoding the test sequence to generate candidate code words; calculating the measurement of the candidate code words and the soft-input information sequence; reducing the number of the candidate code words; determining decision code words according to the measurement of the candidate code words; and calculating external information of each code element in the decision code words. The encoding method has the advantages of improving data throughput and reducing encoding delay; and the decoding method has the advantages of saving a mass of logical resources and storage resources, particularly well balancing decoding complexity and data throughput under the condition of longer code length of component codes.

Owner:XIDIAN UNIV

Method and apparatus for encoding Turbo product code

ActiveCN107659319AReduce bit error rateImprove hard decoding performanceCode conversionError correction/detection by combining multiple code structuresComputer scienceBit error rate

The invention provides a method and apparatus for encoding a Turbo product code, to that the defect of uncorrectable pattern generated at a decoding state of the Turbo product code provided by the prior art can be avoided during the decoding process of the decoder. The method comprises the following steps: encoding an original information matrix to obtain a first codeword matrix; performing interweaving on the original information matrix in the first codeword matrix to obtain a second information matrix block; and encoding the second information matrix block to obtain a first verification matrix block, and placing the first verification matrix block on the right side of a row verification matrix block to obtain a second codeword matrix. The original information matrix in the first codewordmatrix obtained in the encoding mode the same as the traditional 2D Turbo product code is interweaved, so that when a hard decoding algorithm is used for decoding, some uncorrectable patterns are disorganized and broken, so that the bit error rate of the hard decoding algorithm can be greatly reduced, and the decoding performance of the Turbo product code is improved.

Owner:饶德阳

Syndrome tables for decoding turbo-product codes

Owner:SK HYNIX INC

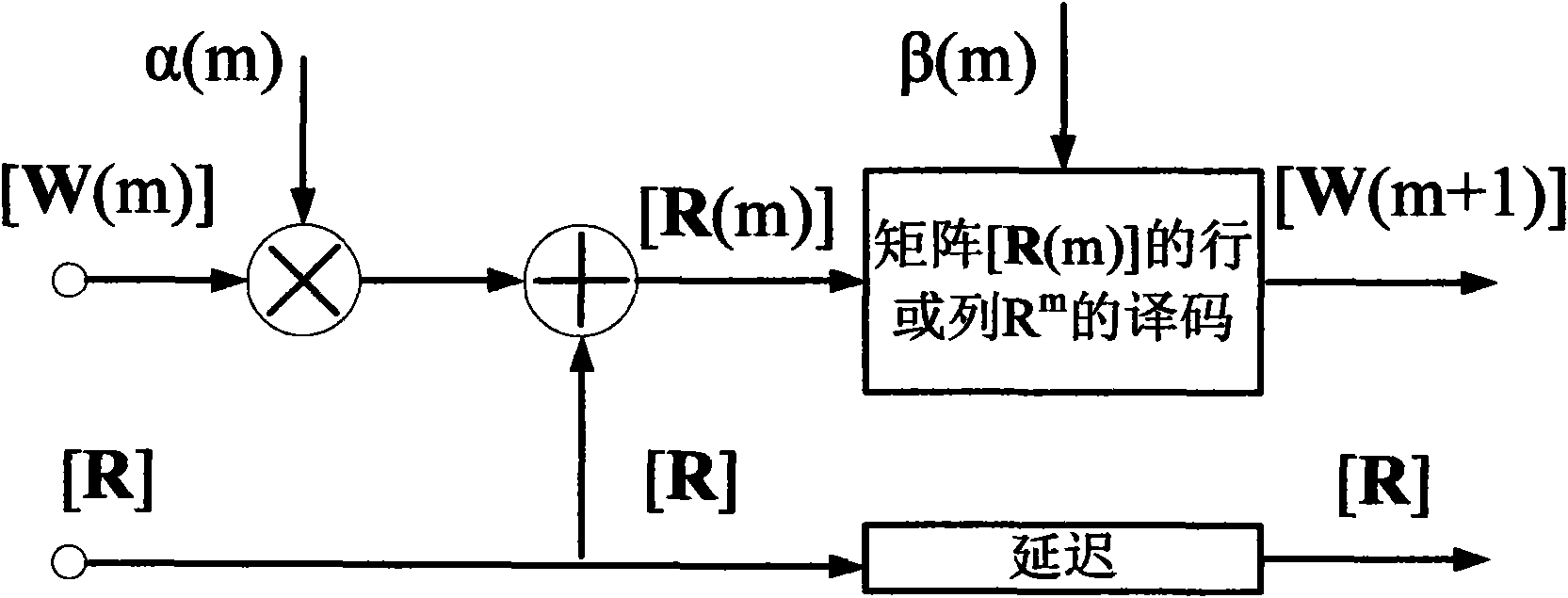

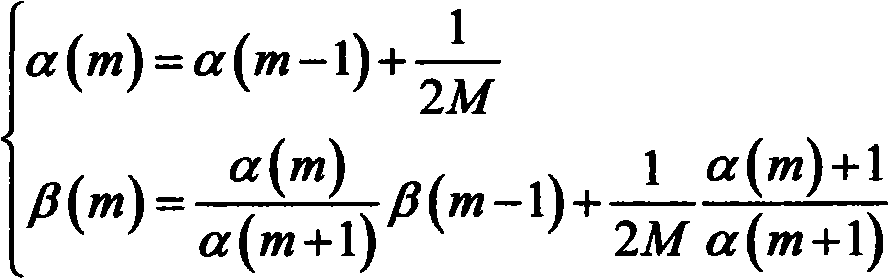

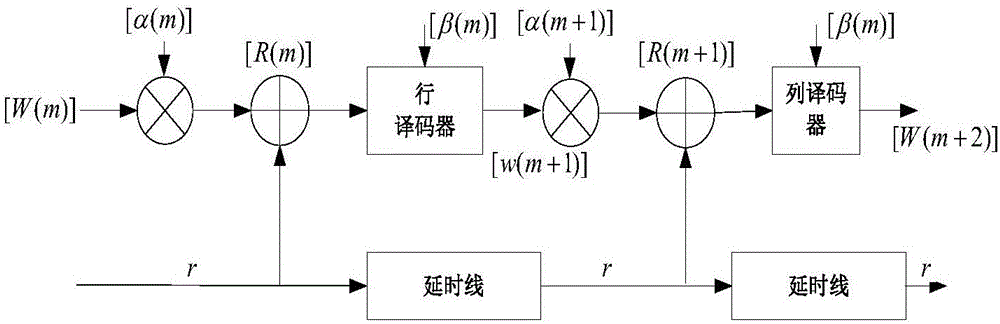

Iterative factor construction method of Turbo product code decoder

InactiveCN101557235AShorten the timeReduce the number of iterationsError correction/detection by combining multiple code structuresComputer scienceWeight factor

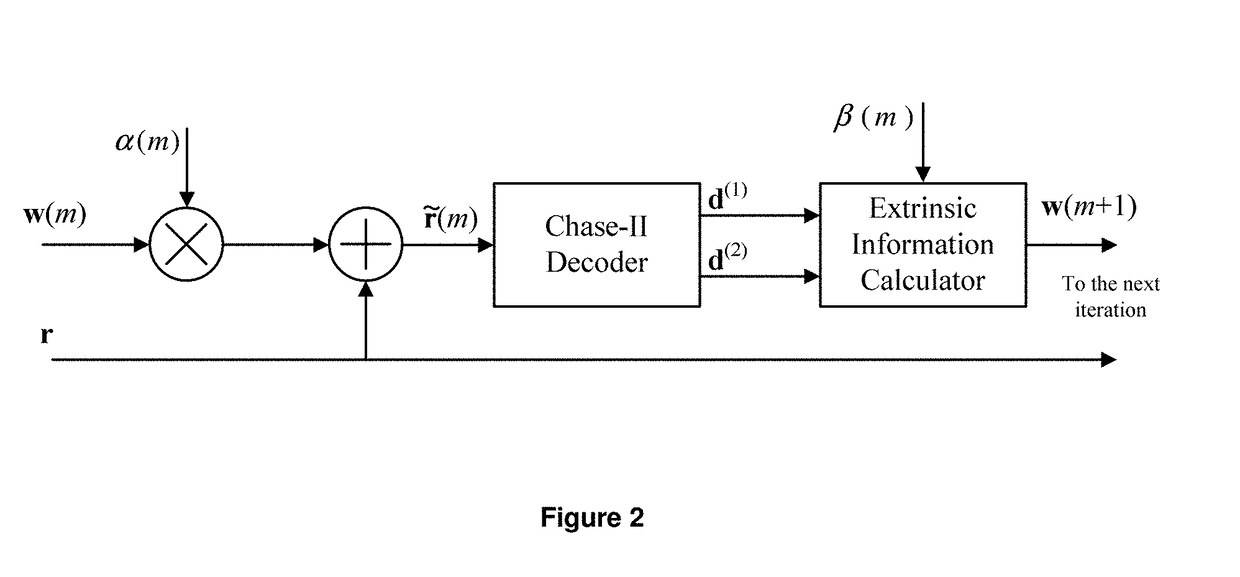

The invention provides an iterative factor construction method of a Turbo product code decoder, which comprises the following steps of: a. selecting a Turbo product code structure, presetting iterations according to the required error rate of communication protocols and setting the values of a weighing factor alpha (1) and a reliability factor beta (1); b. calculating a weight factor alpha (m) and a reliability factor beta (m) through a formula; and c. conducting simulation on the property of the Turbo product code decoder according to the obtained weight factor alpha (m) and the reliability factor beta (m); if the simulation result is not conformable to requirements, increasing the iterations and transferring to step b to re-calculate the weight factor alpha (m) and the reliability factor beta (m) until the simulation result is conformable to the requirements; and taking the weight factor alpha (m) and the reliability factor beta (m) obtained at the last time as the iterative factor of the Turbo product code decoder. The method greatly reduces the required time for determining the iterative factor and can be widely applied to the realization of the soft-input and soft-output decoder of the Turbo product code of different protocols and different structures.

Owner:SHENZHEN GRADUATE SCHOOL TSINGHUA UNIV

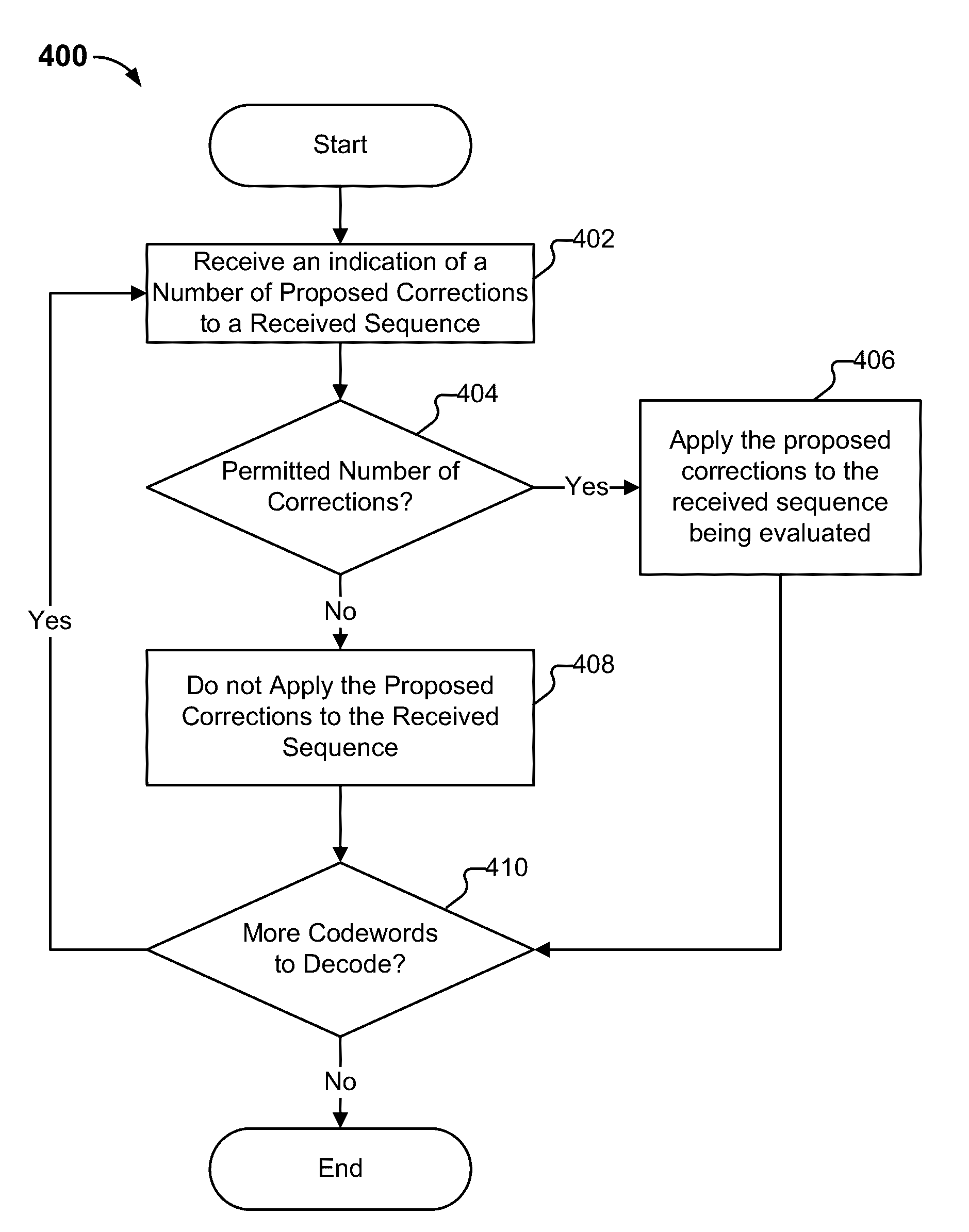

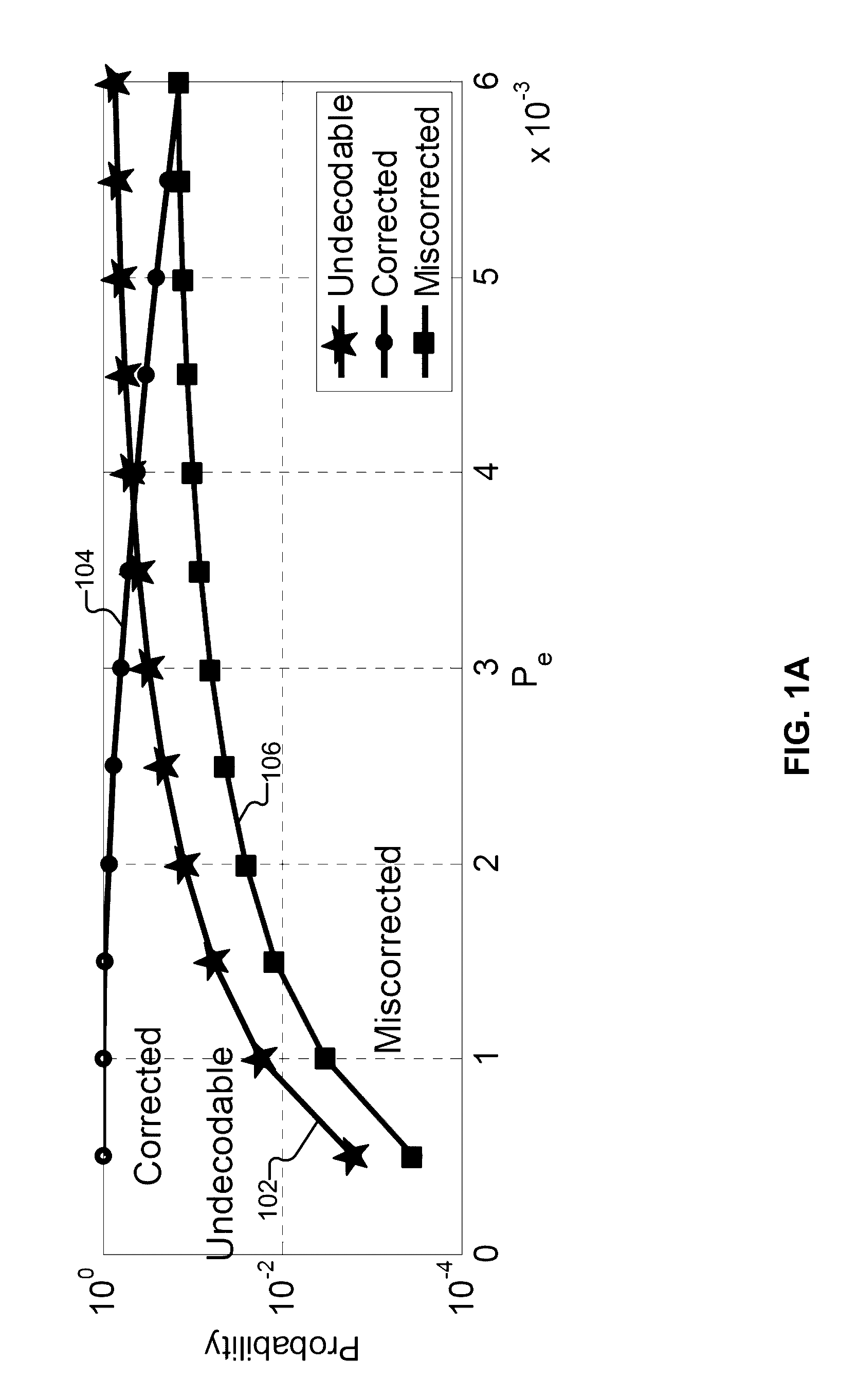

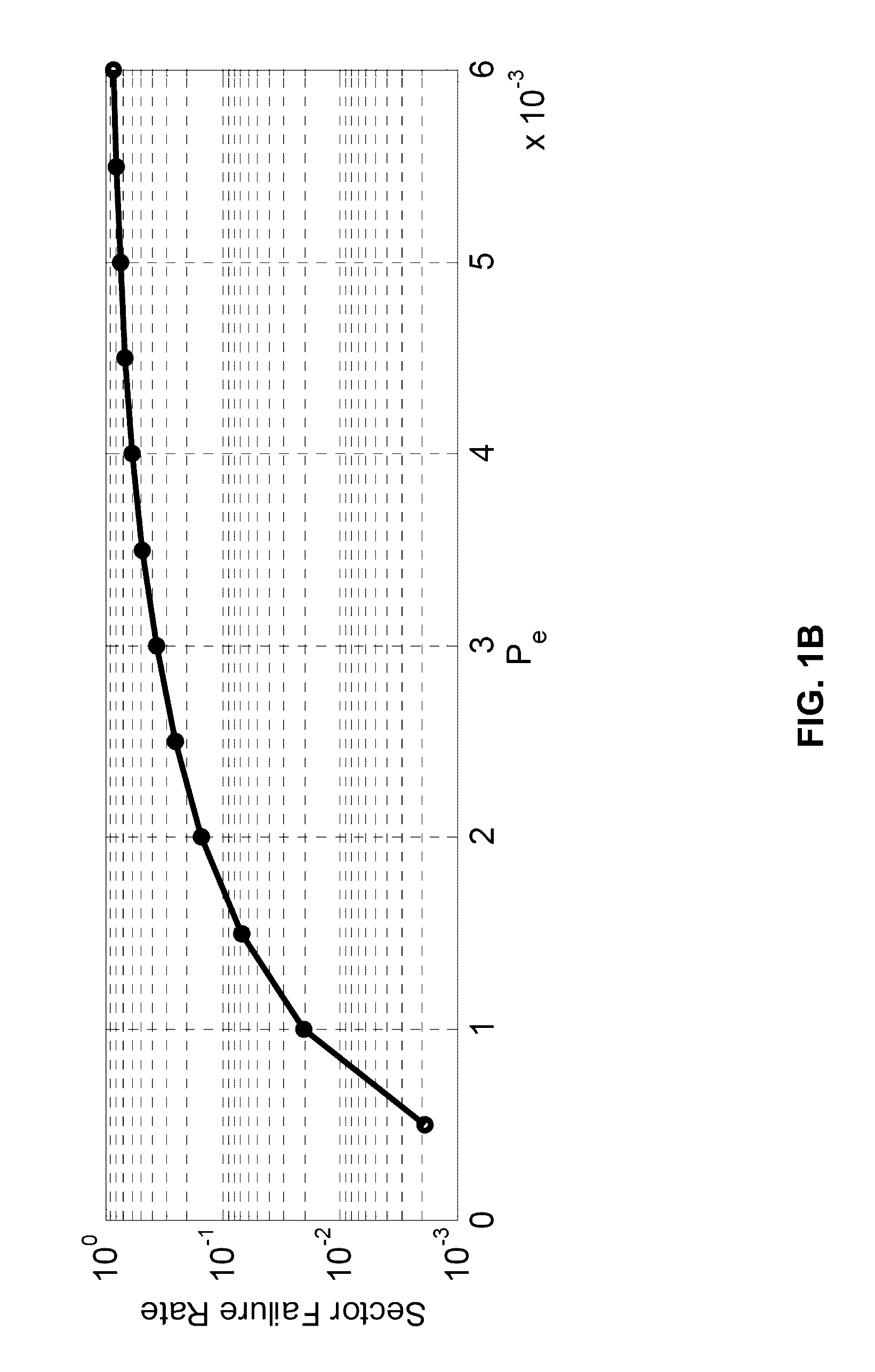

Decoding of turbo product codes using miscorrection detection

ActiveUS9569302B1Code conversionError correction/detection by combining multiple code structuresComputer scienceTurbo product codes

Owner:SK HYNIX INC

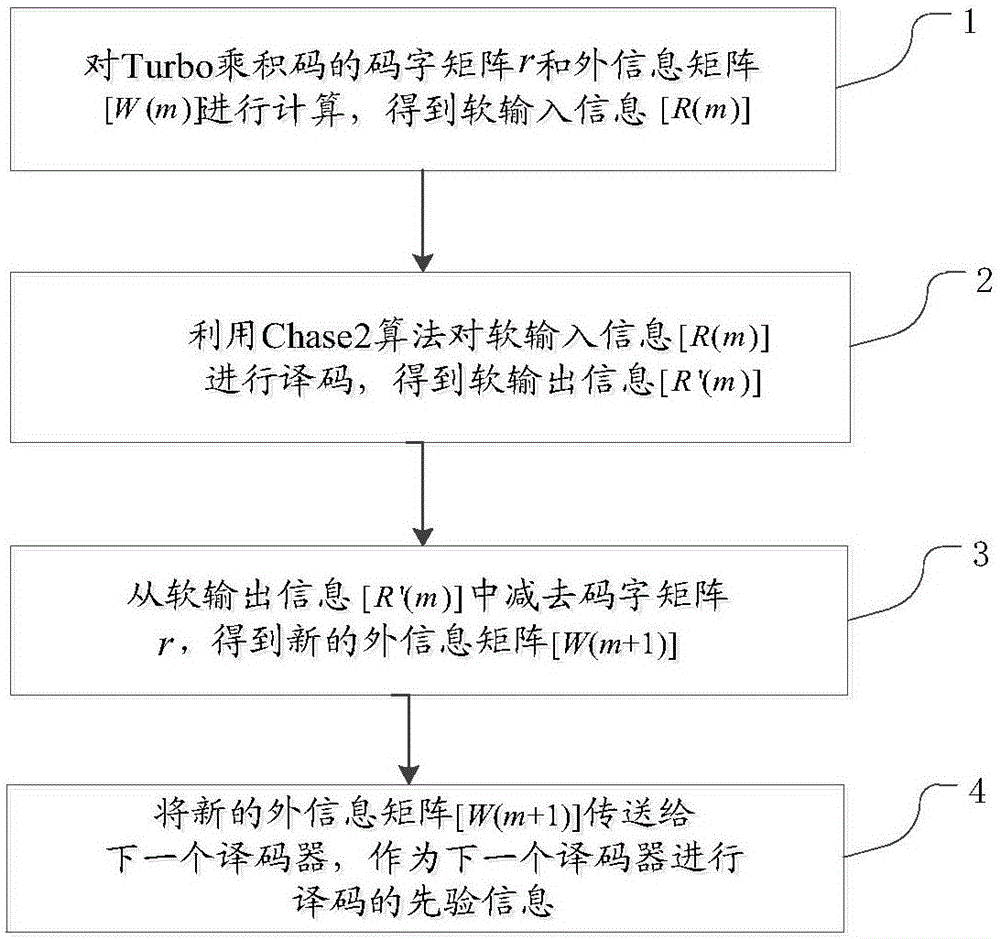

Modified soft-input soft-output decoding method for Turbo product codes

InactiveCN106656216AImprove coding efficiencyHigh coding gainCode conversionError correction/detection by combining multiple code structuresComputer scienceCode word

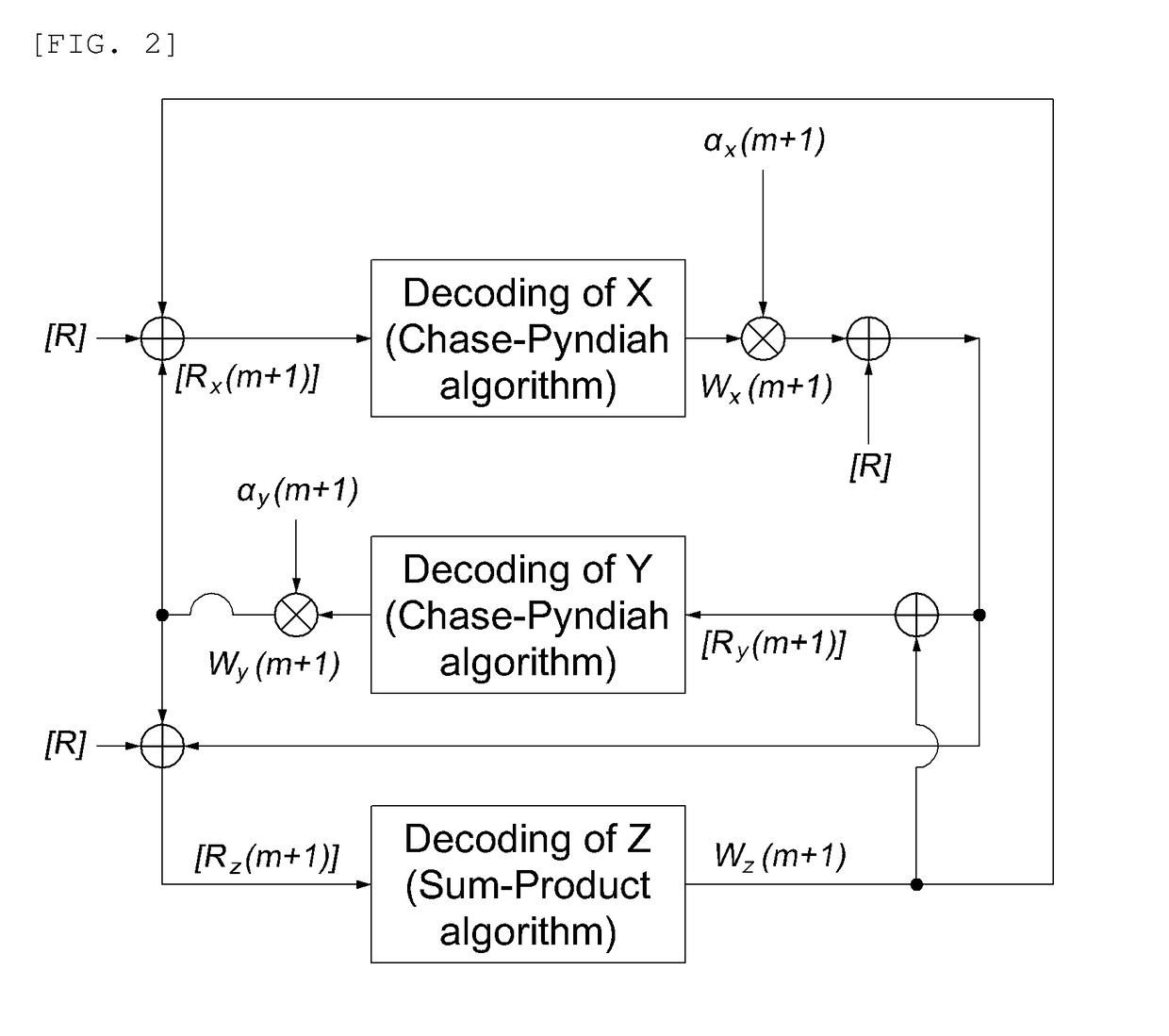

The present invention discloses a modified soft-input soft-output decoding method for Turbo product codes. The method includes the following steps that: the code word matrix r and an outer information matrix [W (m)] of the turbo product codes are calculated, so that soft-input information [R(m) is obtained; a Chase2 algorithm is utilized to decode the soft-input information [R(m), so that soft-output information [R '(m)] is obtained; the code word matrix r is subtracted from the soft-output information [R '(m)], so that a new outer information matrix [W (m+1)] is obtained; and the new outer information matrix [W (m+1)] is transferred to a next decoder and is adopted as priori information for the next decoder to perform decoding. With the method adopted, the complexity of decoding can be reduced.

Owner:HUNAN KEAYSHARE COMM TECH CO LTD

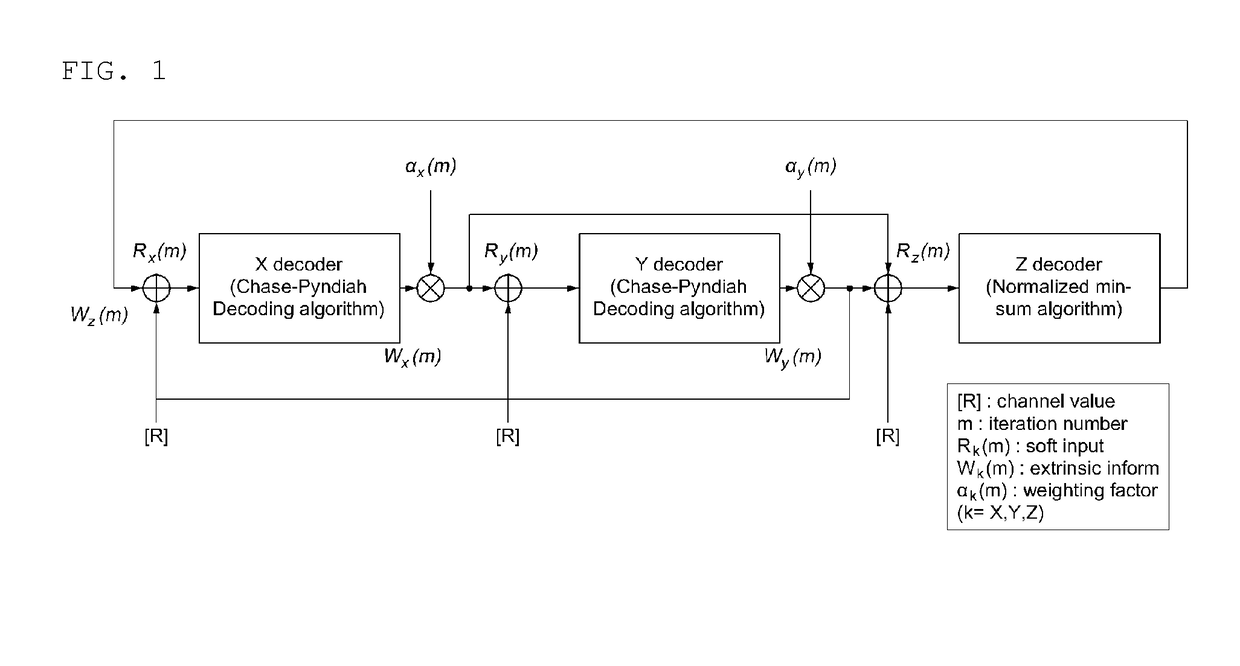

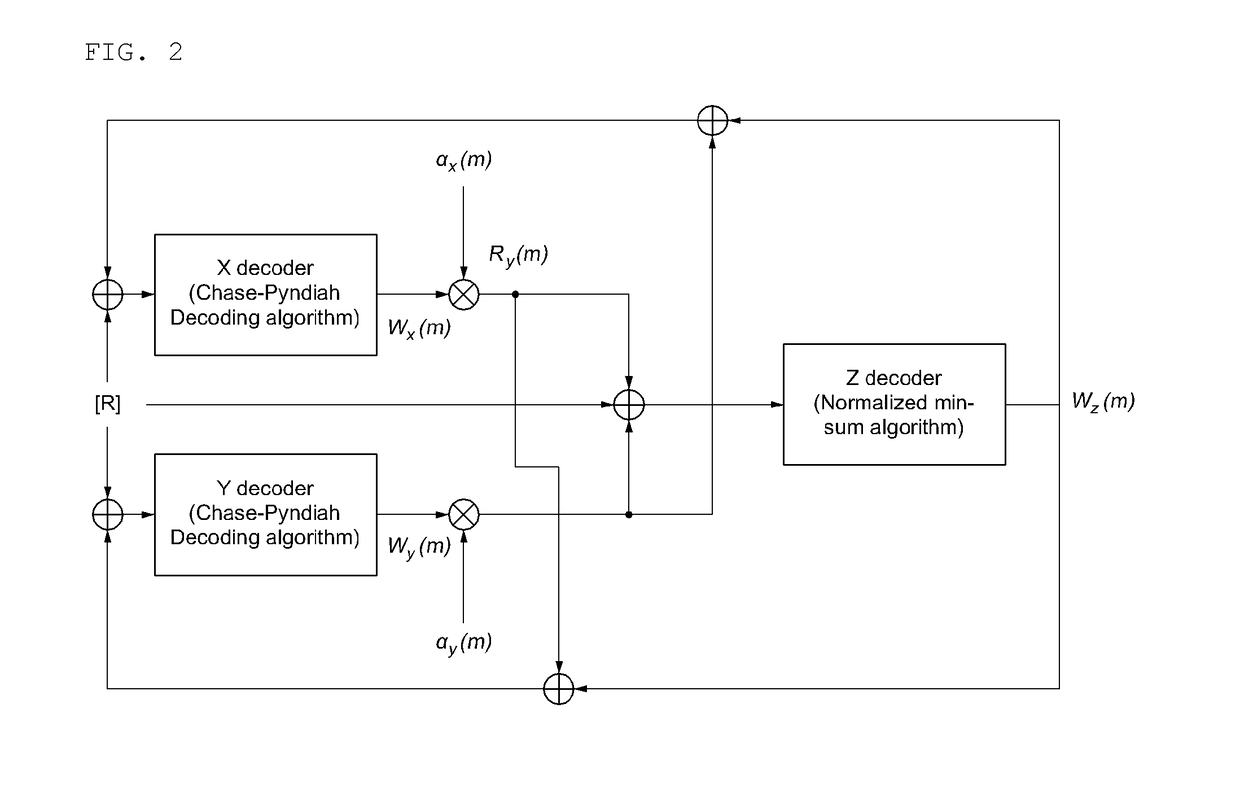

Method and apparatus for decoding three-dimensional turbo product code based on crossing layers

ActiveUS20180302109A1Guaranteed accuracyThroughput be ensuredCode conversionSingle error correctionComputer scienceCross layer

Disclosed is a three-dimensional TPC decoding apparatus. A three-dimensional TPC decoding apparatus includes an X decoder which decodes an X axis of an m-th upper half layer based on decoding results of a Y axis and a Z axis of an m−1-th upper half layer; a Y decoder which decodes a Y axis of an m-th lower half layer based on decoding results of an X axis and a Z axis of an m−1-th lower half layer; and a Z decoder which decodes a Z axis based on a decoding result of the Y axis of an m-th upper half layer and a decoding result of the X axis of an m-th lower half layer.

Owner:KOREA UNIV RES & BUSINESS FOUND

Scheme to avoid miscorrection for turbo product codes

The present invention discloses a memory system and operating method thereof. The major features of the memory system and the method of operating thereof are identifying a stuck error pattern including failing constituent codes and decoding the stuck error pattern. The decoding the stuck error pattern is achieved by following steps: step 1 of using possible flipping patterns for decoding the failing constituent codes, and the number of the possible flipping patterns is 2 or more in accordance with at least the number of error bits, step 2 of obtaining a number of successfully decoded codewords after using the possible flipping patterns, and step 3 of selecting the most probable codeword from the number of successfully decoded codewords.

Owner:SK HYNIX INC

Turbo-product codes (TPC) with interleaving

ActiveUS9300329B2Other error detection/correction/protectionCode conversionComputer hardwareCorrection code

Decoding associated with a second error correction code and a first error correction code is performed. Ns first and second-corrected segments of data, first sets of parity information, and second sets of parity information are intersegment interleaved to obtain intersegment interleaved data, where the Ns segments of data, the Ns first sets of parity information, and the Ns second sets of parity information have had decoding associated with the first and the second error correction code performed on them (Ns is the number of segments interleaved together). Decoding associated with a third error correction code is performed on the intersegment interleaved data and interleaved parity information to obtain at least third-corrected interleaved data. The third-corrected interleaved data is de-interleaved.

Owner:SK HYNIX MEMORY SOLUTIONS

Sdd decoder for digital communications

There is provided an ultra-light decoder for high speed digital communications based on block codes such as turbo product codes (TPCs). The new decoder can perform soft decision decoding without an algebraic hard decision decoder, which is the core of conventional soft decision decoders. The elimination of algebraic decoder significantly reduces the number of computations required per codeword, consequently, it reduces the decoding delay and processing power. However, reducing the decoding delay would immediately enable increasing the transmission speed, and minimize the need for large buffers at the receiver. Moreover, reducing the complexity and delay would enable using codes with high code rates to increase the system capacity, or use powerful codes with low code rates to reduce the transmission power. Such benefits can be achieved for about 1 dB loss in coding gain. There is also provided a receiver comprising the ultra-light decoder, as well as a decoding process.

Owner:KHALIFA UNIV OF SCI & TECH

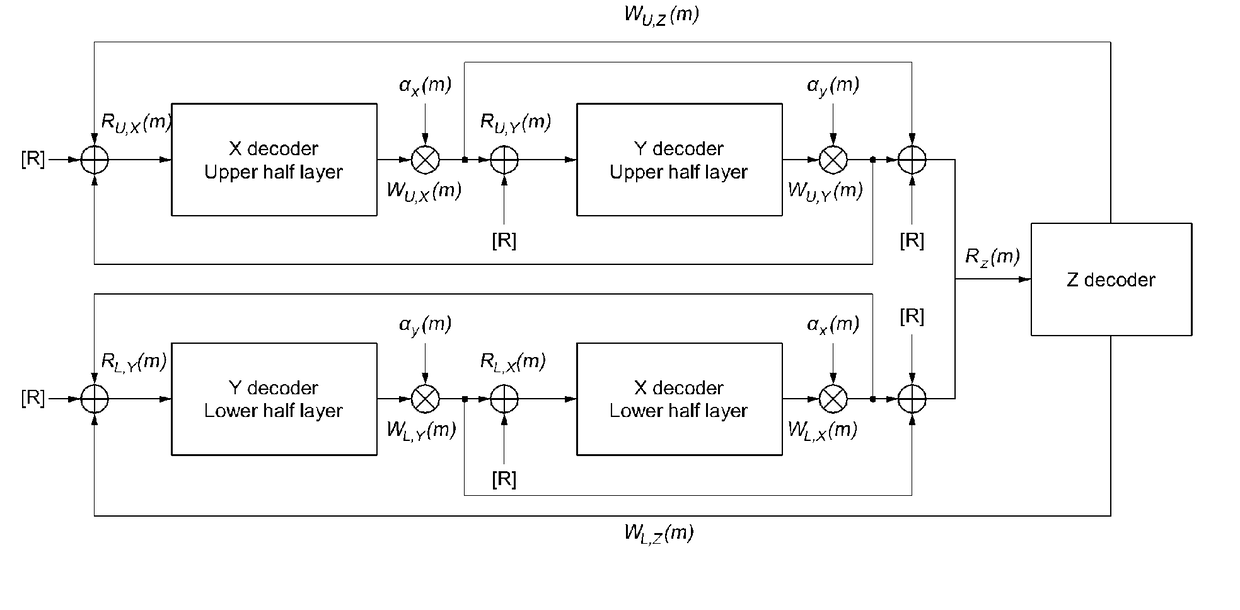

Hybrid type iterative decoding method and apparatus

ActiveUS20180309463A1Ensure correct executionCode conversionSingle error correctionHybrid typeComputer science

A hybrid type iterative decoding method for a three-dimensional turbo product code (TPC) having a first axis (FA), a second axis (SA), and a third axis (TA) including: a parallel decoding step of applying a predetermined decoding algorithm (PDA) in parallel to current FA and SA input values (IVs) which are determined based on at least two previous decoding values (DVs), respectively, among the previous FA, SA and TA DVs which are generated in advance to generate a current FA DV and a current SA DV, respectively; a serial decoding step of applying PDA to a current TA IV determined based on the current FA and SA DVs to generate a current TA DV; and performing hard decision based on the current FAs DV, the current SA DV, the current TA DV, and the received signal value.

Owner:KOREA UNIV RES & BUSINESS FOUND

Apparatus and method for turbo product codes

ActiveUS20160149592A1Improve acceleration performanceReduce hardware complexityCode conversionError correction/detection by combining multiple code structuresComputer hardwareComputer science

An apparatus for a turbo product codes includes a codeword generator and an interleaver. The codeword generator receives a data in a matrix, and generate a turbo product code (TPC) codeword including the data, row parities and column parities. The interleaver interleaves the TPC codeword by assigning at least one bit in at least one row-column intersection of the TPC codeword to at least one master code, and outputs the interleaved TPC codeword.

Owner:SK HYNIX INC

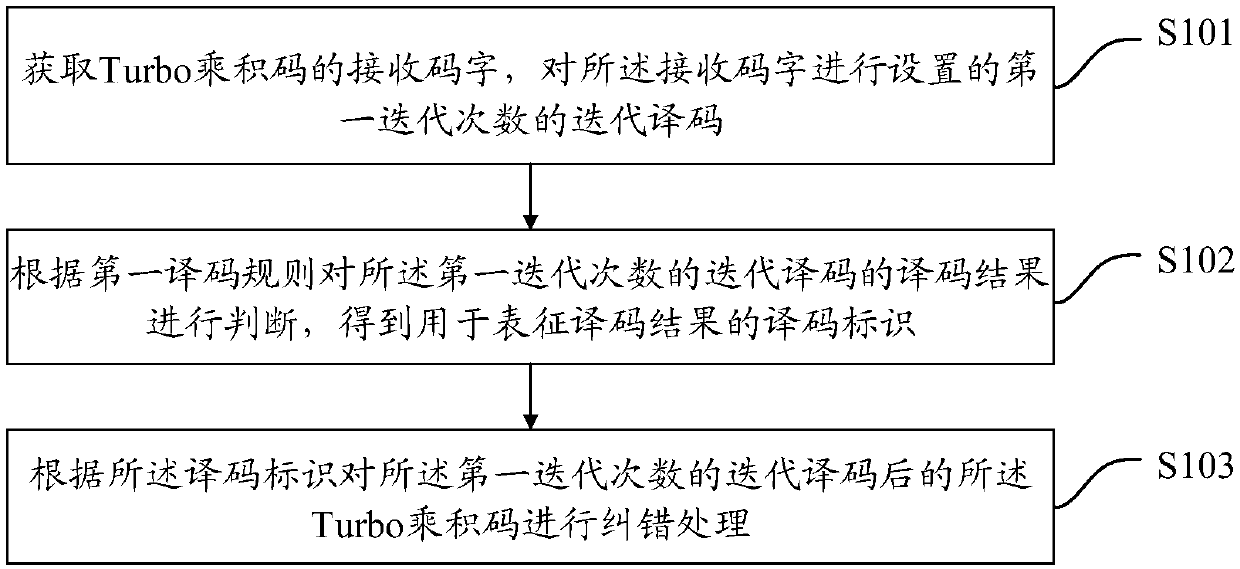

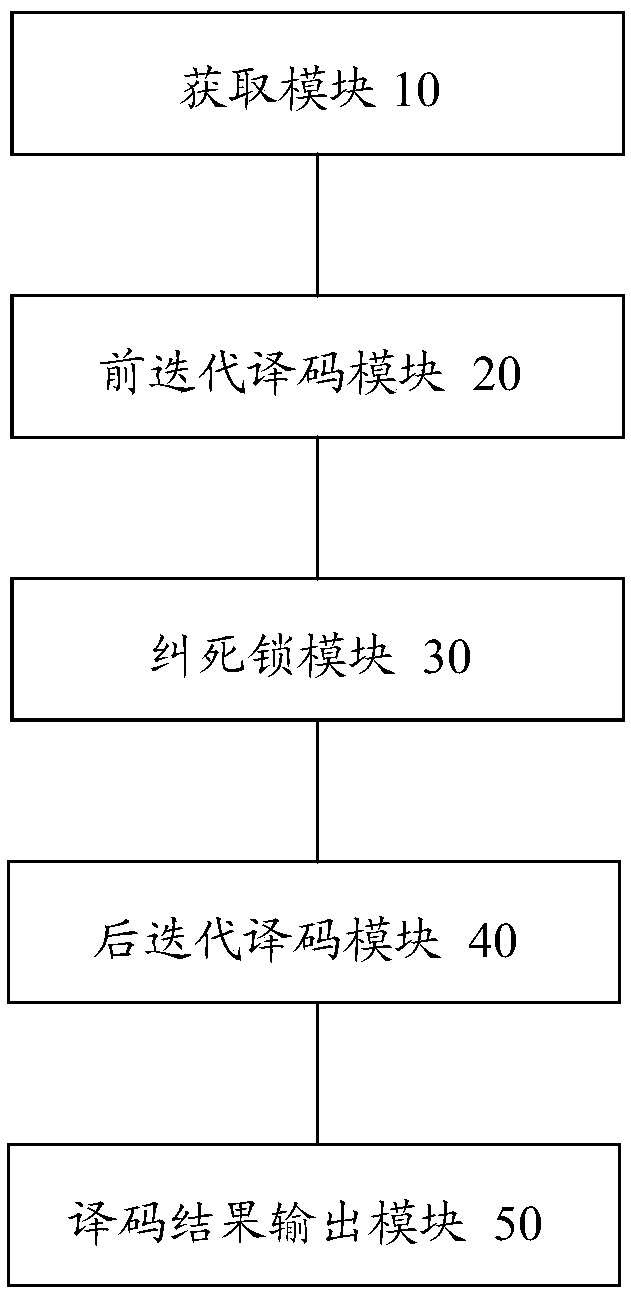

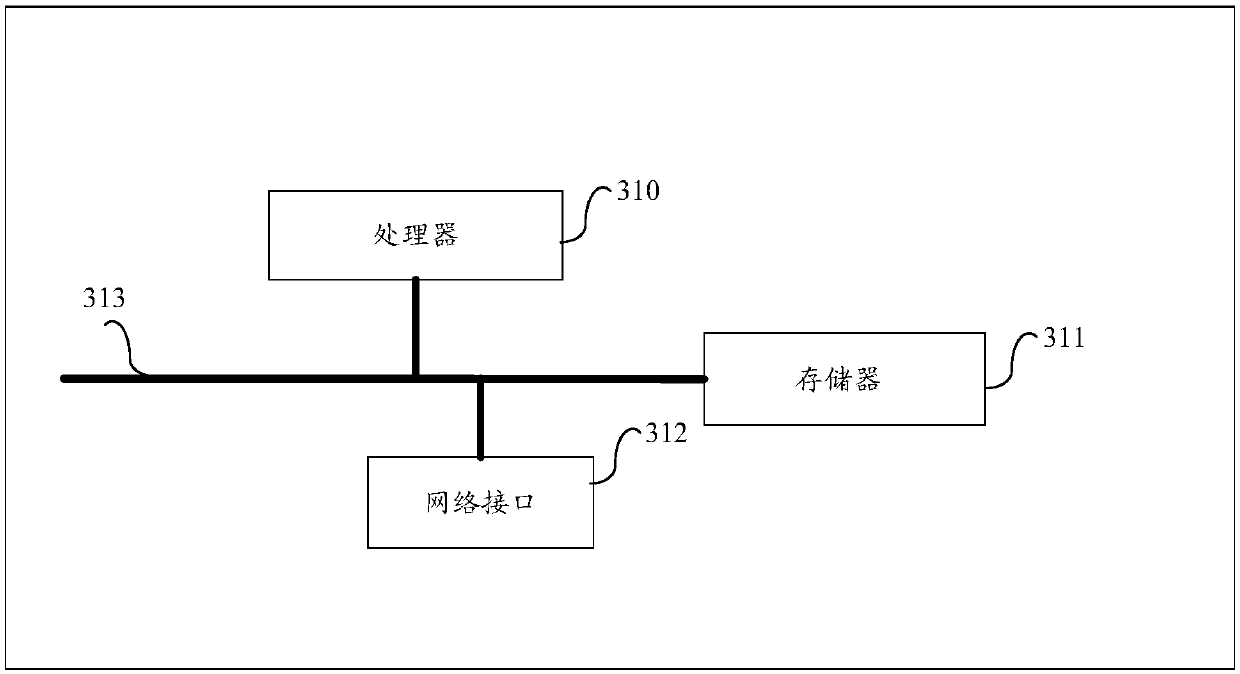

Decoding method and device of Turbo product code, decoder and computer storage medium

ActiveCN110896309ACode conversionError correction/detection by combining multiple code structuresTheoretical computer scienceProcessing

The embodiment of the invention discloses a decoding method of a Turbo product code, which comprises the following steps of: obtaining a receiving code word of the Turbo product code, and carrying outiterative decoding on the receiving code word for a set first iterative decoding frequency; judging a decoding result of iterative decoding of the first iteration times according to a first decodingrule to obtain a decoding identifier for representing the decoding result; and carrying out error correction processing on the Turbo product code after iterative decoding of the first number of iterations according to the decoding identifier. The embodiment of the invention further discloses a decoding device of the Turbo product code, a decoder and a computer storage medium.

Owner:ZTE CORP