Real-time simulation validation system and method for communication system integrated circuit design

A technology of integrated circuits and communication systems, applied in the field of real-time simulation verification systems, can solve problems such as lack of real-time performance, adding test vectors, duplication and waste of time and resources, and avoid test vectors and the time used to generate the overall frame structure , easy to find the effect of the problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

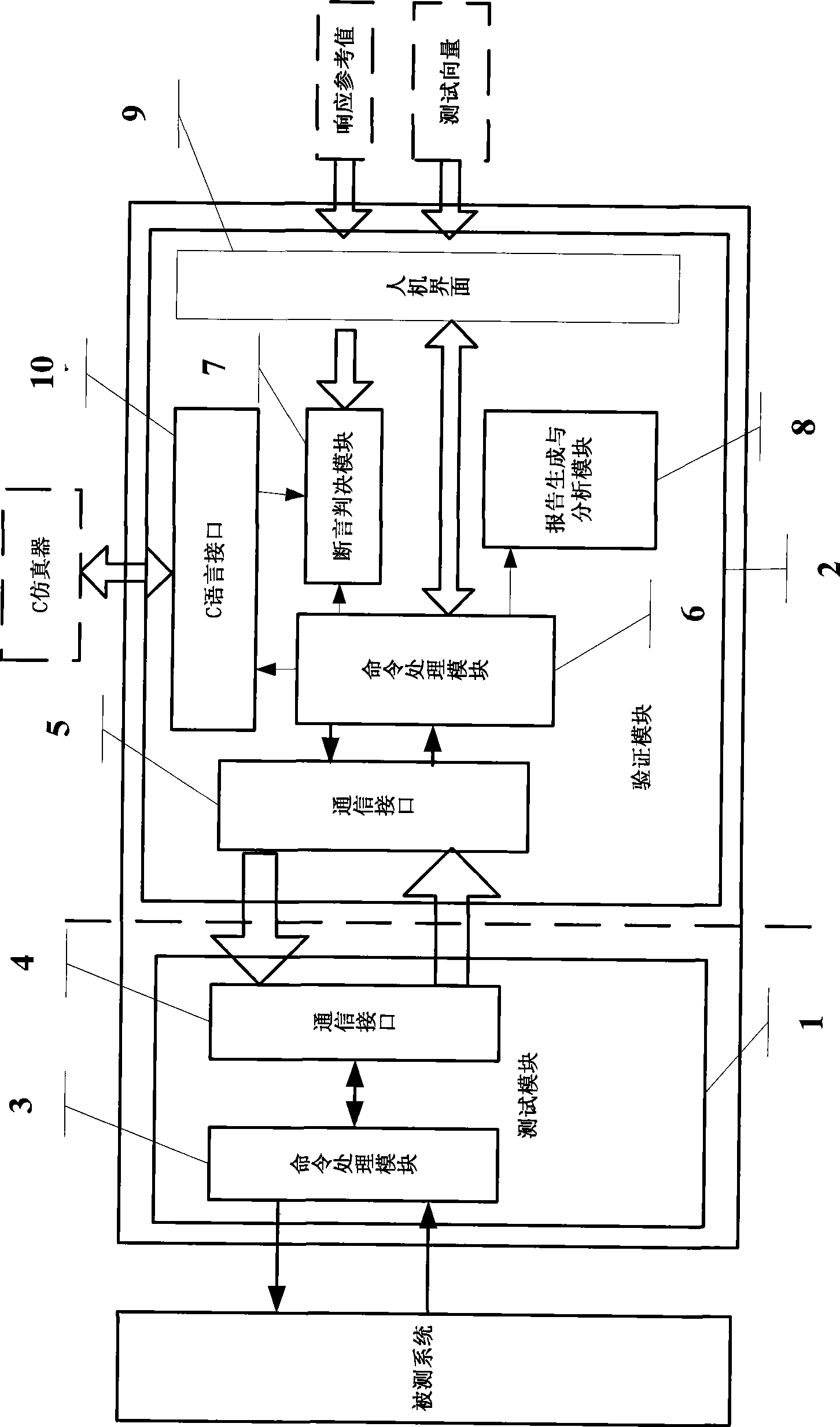

[0096] Specific embodiments of the present invention will be described below in conjunction with the accompanying drawings.

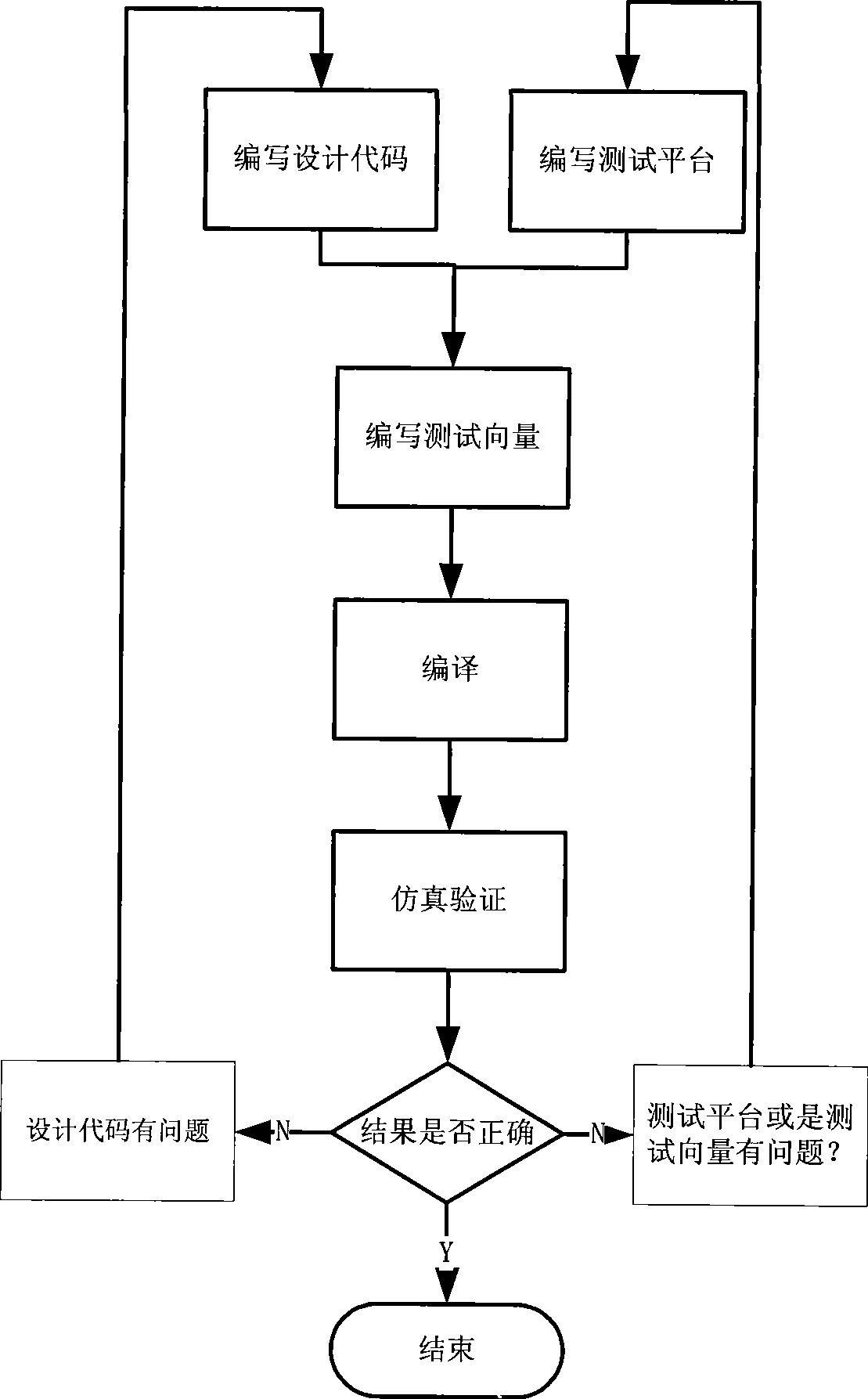

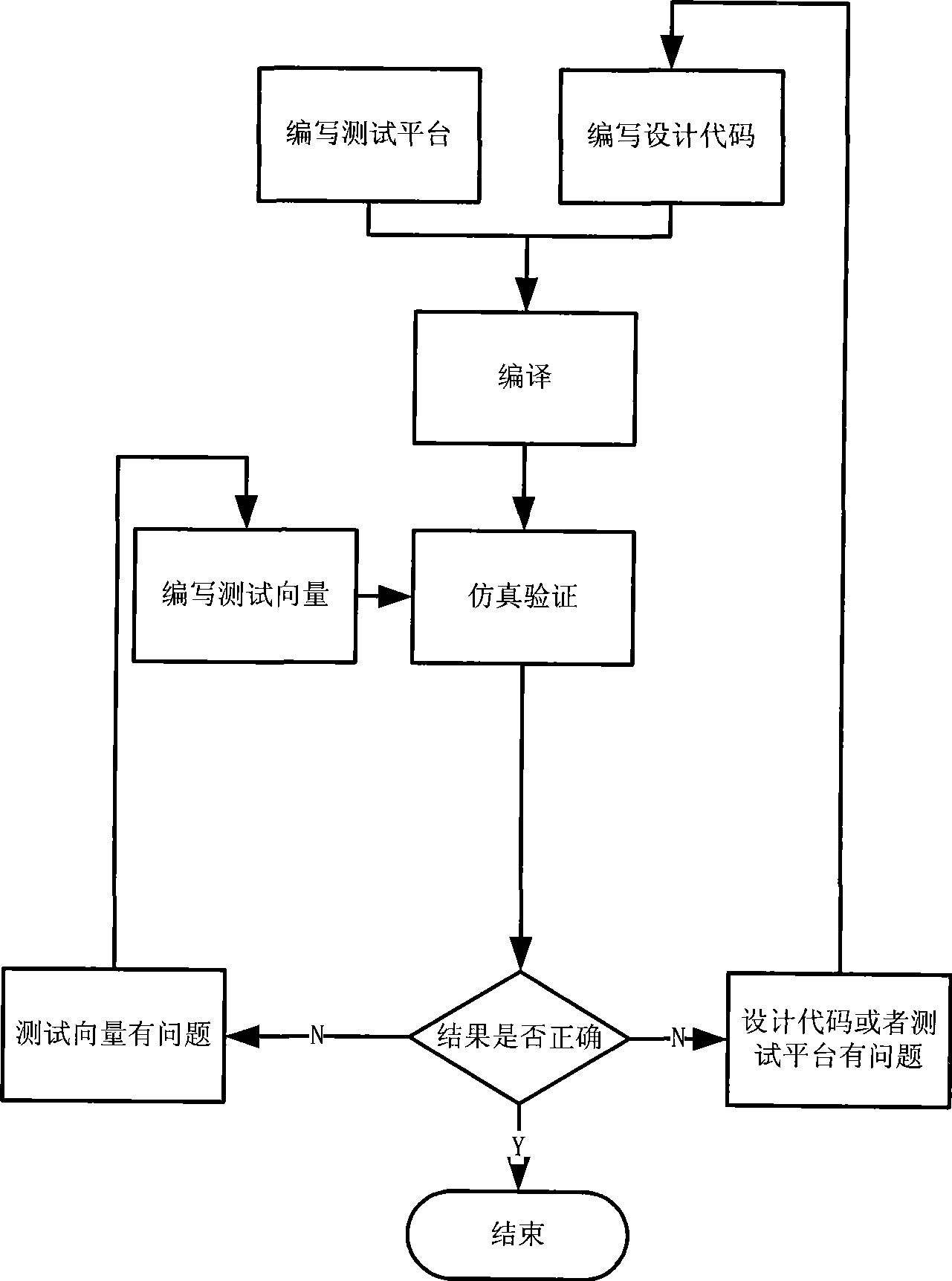

[0097] Such as figure 2 As shown, it is a flow chart of the verification process using the simulation verification system for communication system integrated circuit design provided by the present invention. The verification process shown in this flowchart can be divided into the following steps:

[0098] Step1: Write the design under test;

[0099] Step2: Write the test platform;

[0100] Step3: Use the simulation tool to compile;

[0101] Step4: Write test vectors;

[0102] Step5: Simulation and verification;

[0103] Step6: Determine whether the response is correct, and if the response is correct, end the verification process;

[0104] Step7: If the judgment of Step6 is incorrect, such as judging the problem caused by the design itself or the test platform, return to Step1;

[0105] Step8: If the judgment in Step6 is incorrect, such as the pr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More