Loading/memorizing unit of embedded processor

A technology of embedded processors and storage units, applied in memory systems, electrical digital data processing, instruments, etc., can solve problems such as blocking normal execution, and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention will be further described below in conjunction with the accompanying drawings.

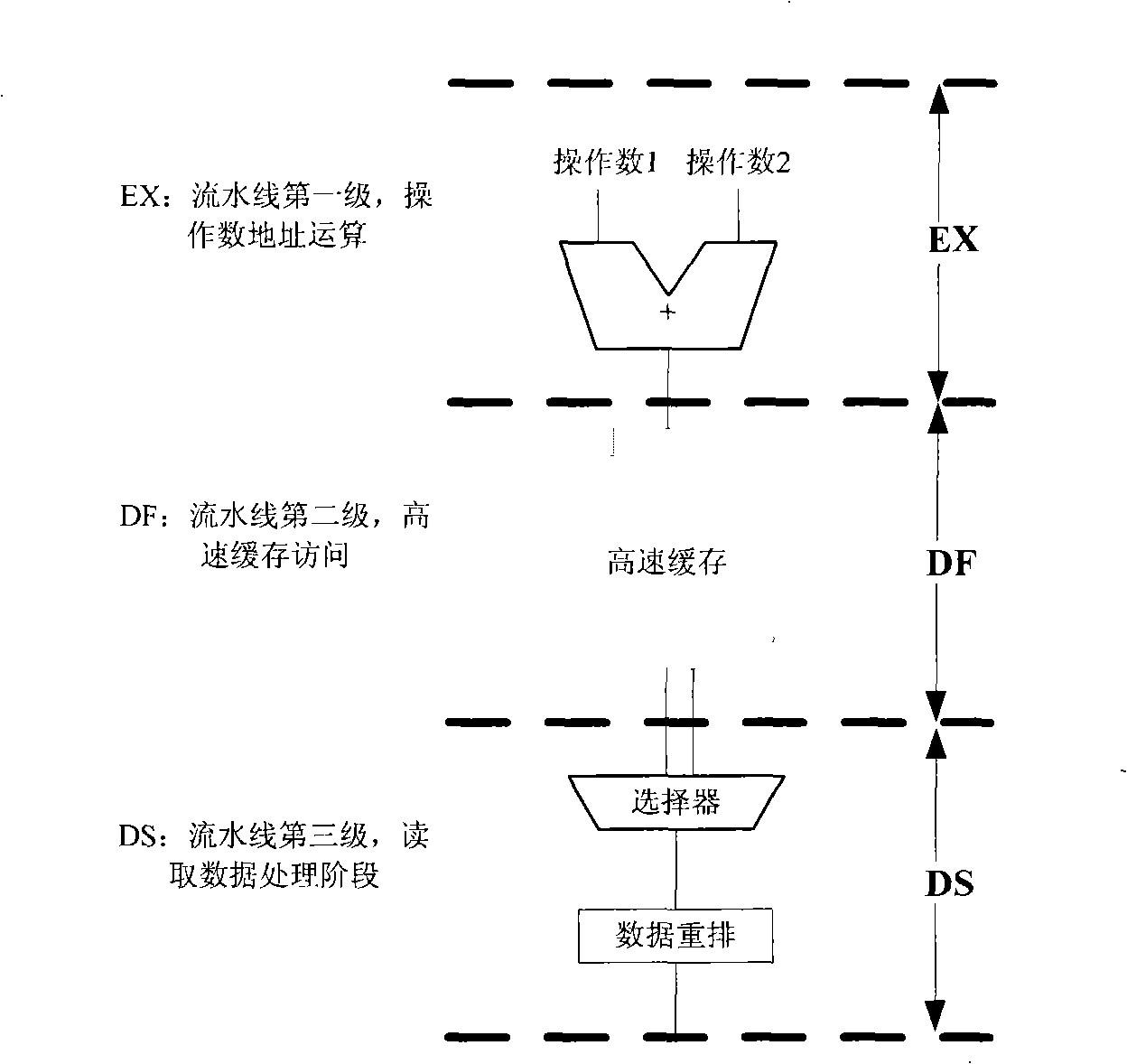

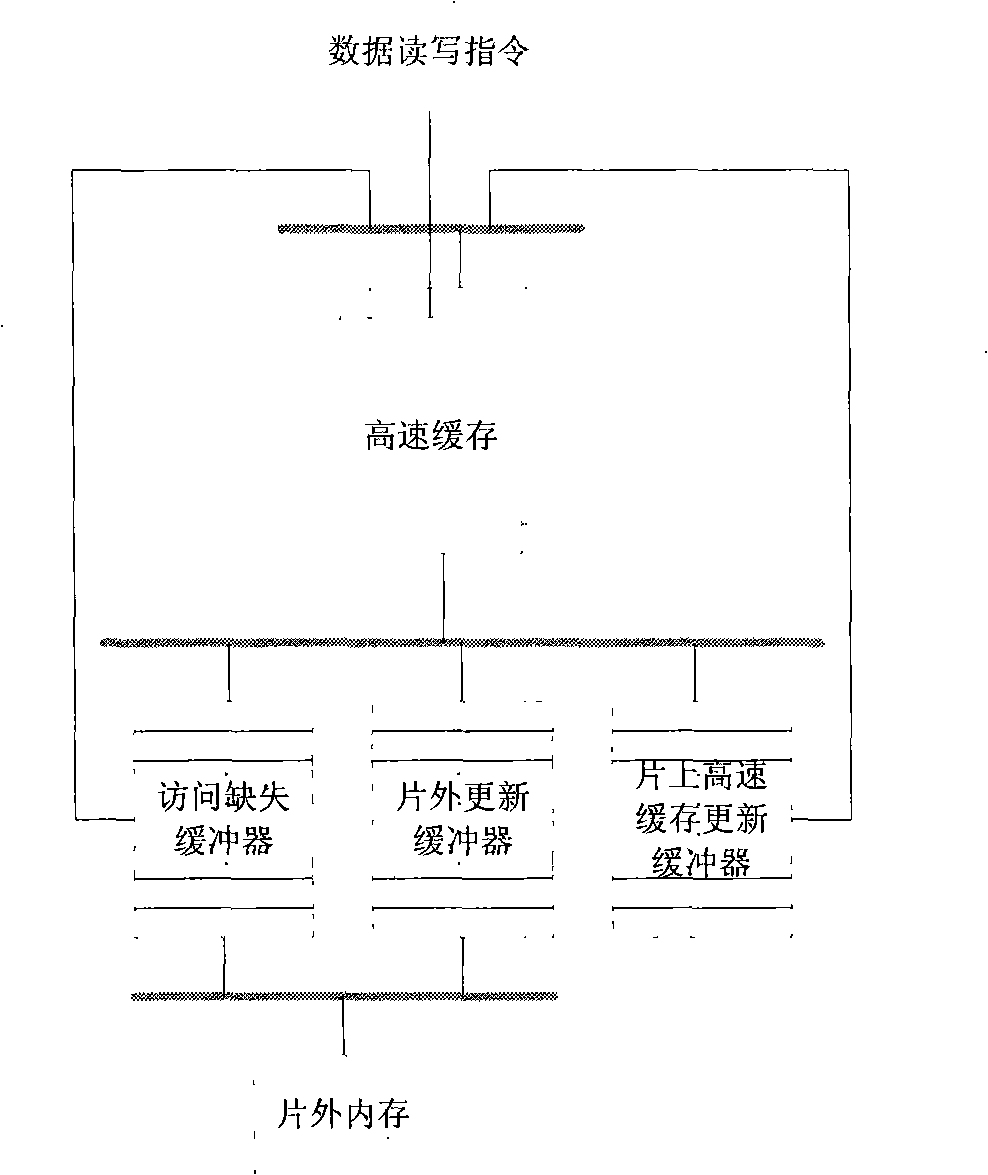

[0020] refer to figure 1 with figure 2 , a load / store unit of an embedded processor. In the load / store unit, the read and write instructions in a fully pipelined manner are used to access the on-chip cache. Instructions are saved to a dedicated access miss buffer and pipeline resources are released, and subsequent instructions continue to access the cache.

[0021] An independent off-chip update buffer is set to cache the write operation of the off-chip memory to quickly retire the off-chip memory write operation; an independent on-chip update buffer is set to cache the on-chip cache update operation to quickly retire the cache write operation.

[0022] This embodiment adopts the full pipeline method to realize the access of the read and write instructions to the on-chip cache: the full pipeline method to realize the access of the read and write instructions to the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More