Double patterning for lithography to increase feature spatial density

A pattern and spatial frequency technology, applied in the field of density of feature space, can solve problems such as not easy to be compatible with photoresist

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

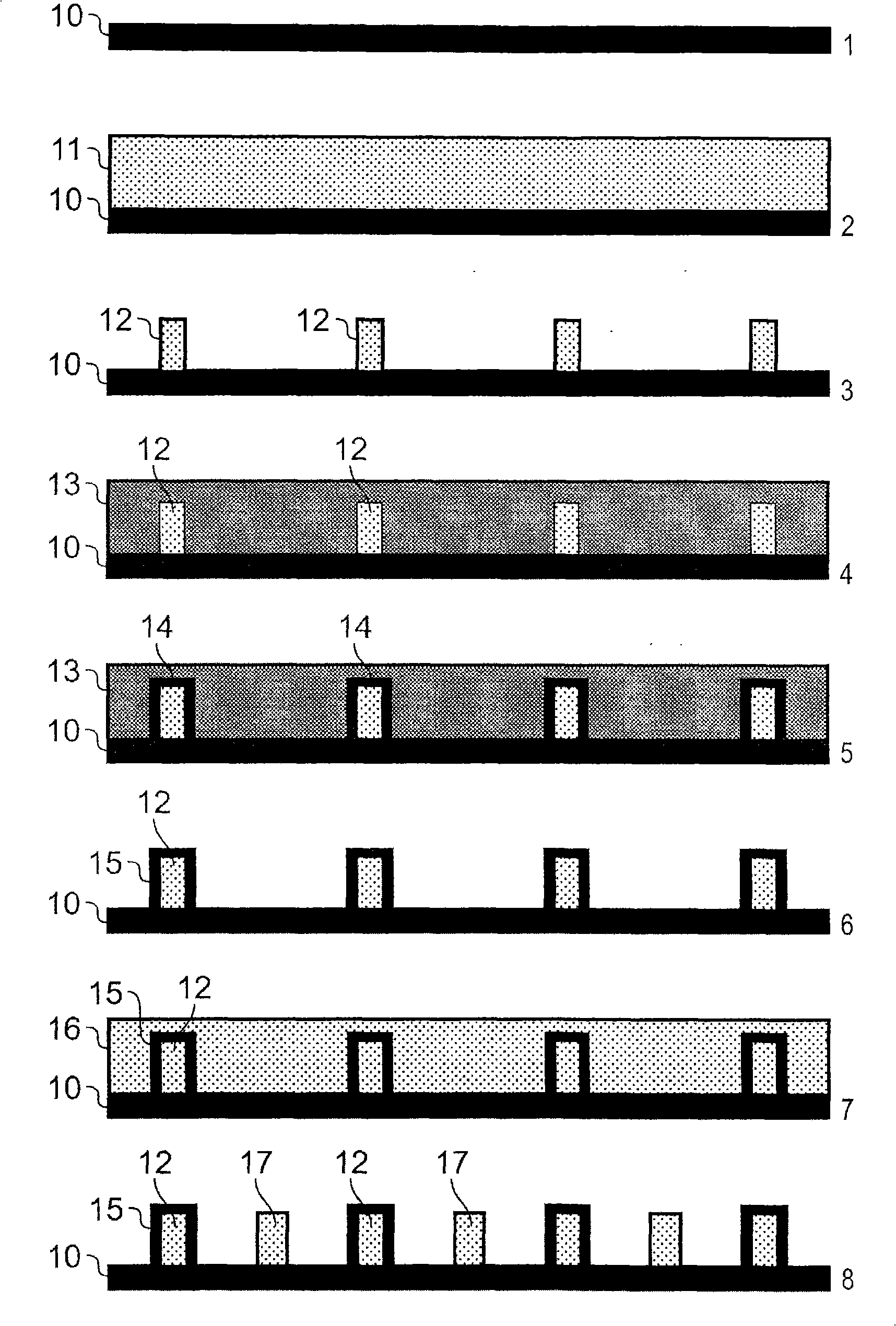

[0032] figure 1 A schematic cross-sectional view representing the process sequence of the two-time patterning technique is provided.

[0033] Picture 1-1 The device layer 10 of the substrate is shown ready for lithographic processing. Throughout the specification, unless expressly stated otherwise, the expression "substrate" does not only denote the original (eg silicon wafer) substrate, but also any subsequently deposited and / or defined layer up to the relevant point in the process being described. therefore, Picture 1-1 The device layer 10 may comprise a base silicon wafer or other semiconductor wafer or other bare substrate suitable for forming an integrated circuit, or an uppermost device layer processed by earlier deposited and / or defined layers, eg, from earlier photolithographic steps.

[0034] Accordingly, it should be understood that the device layer 10 need not be planar, especially if it includes earlier patterned layers or surface features that have not been pl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More