Gate associated transistor of trough arsenic-doped polysilicon structure

A technology of combined gate transistors and gate polysilicon, which is applied in the direction of semiconductor devices, electrical components, circuits, etc., can solve the problems of poor resistance to avalanche breakdown, and achieve enhanced ability to resist avalanche breakdown, low cost, and high cost performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

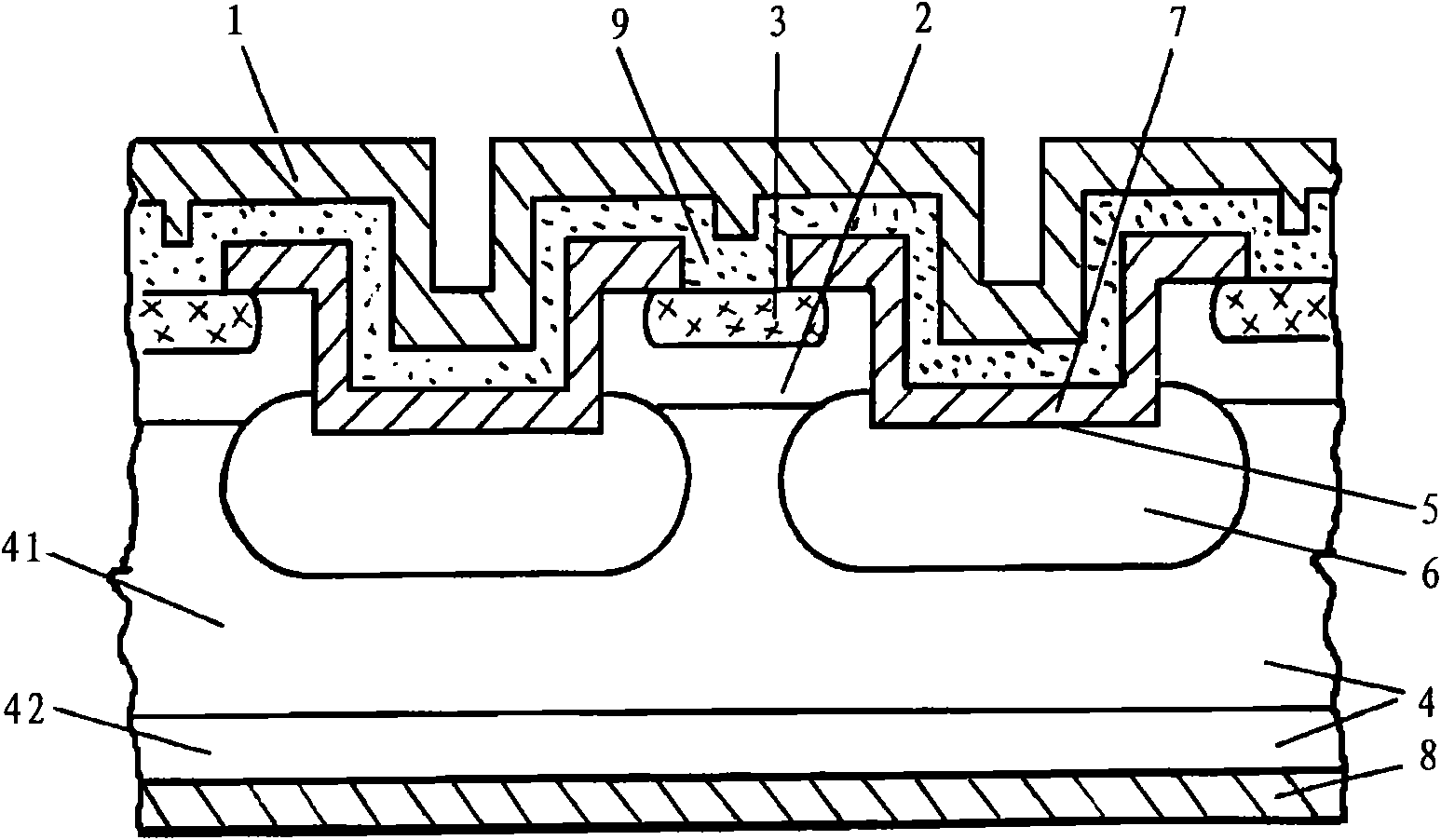

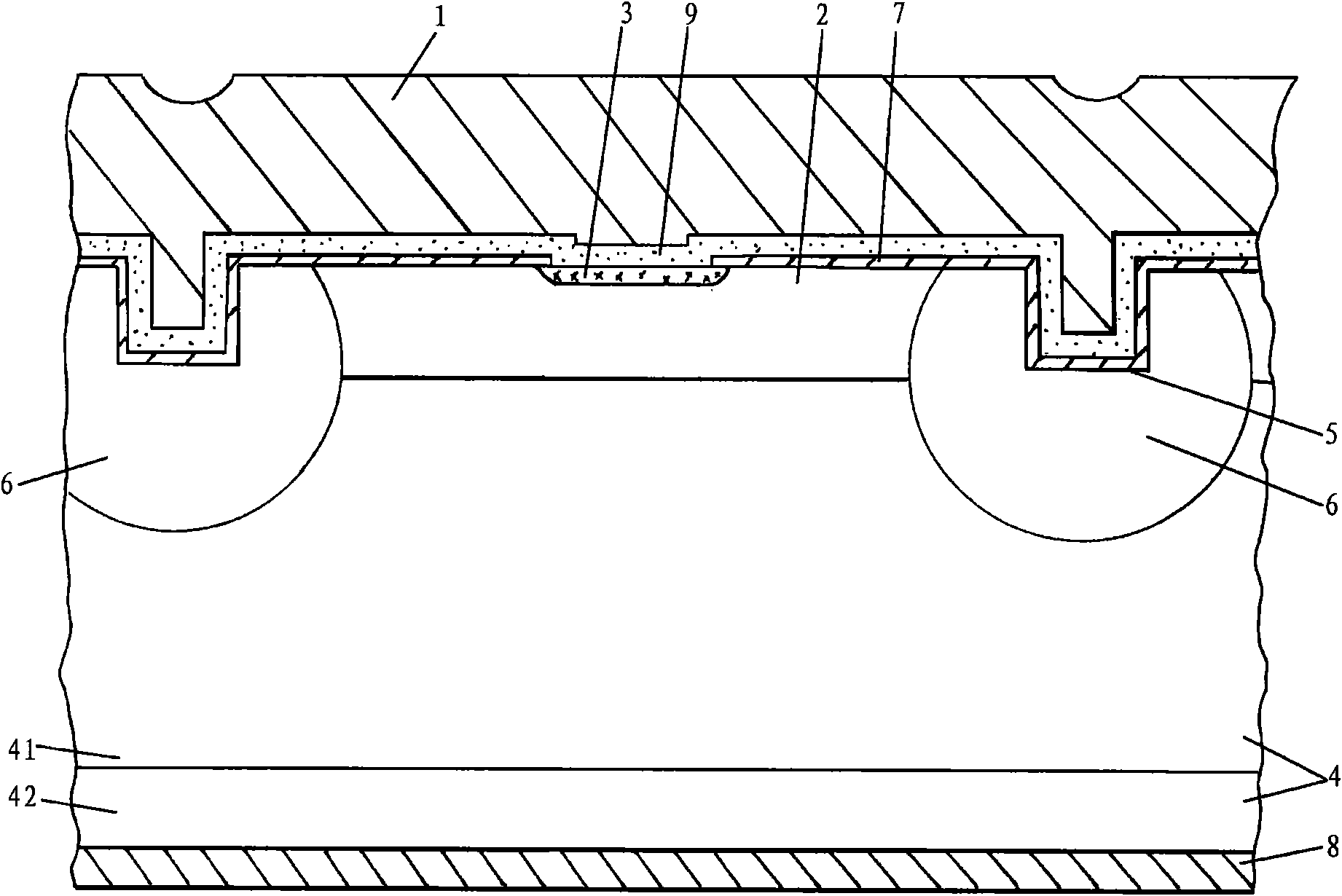

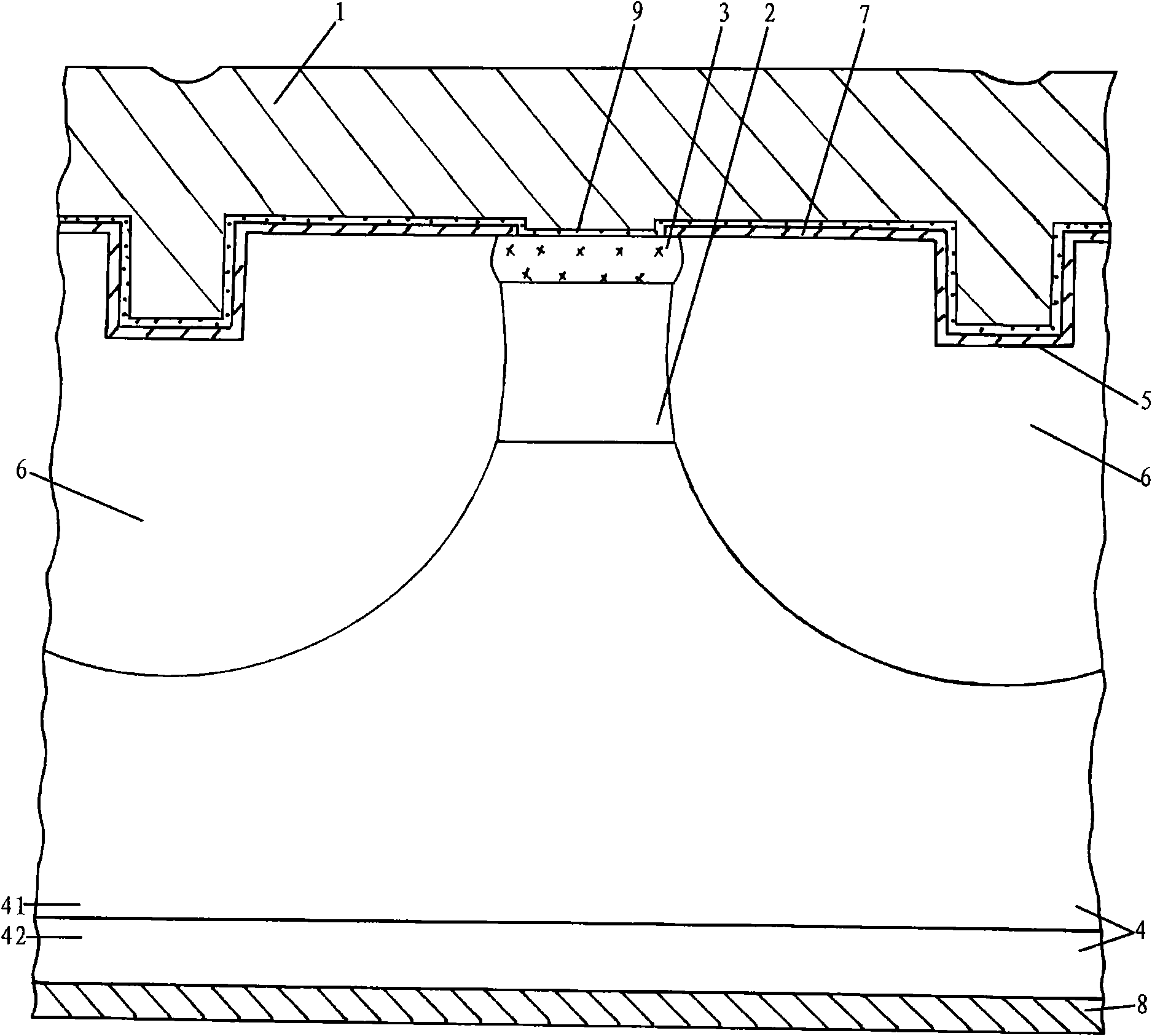

[0020] exist image 3 In the embodiment of the gate transistor with the polysilicon structure of the groove gate shown, the lower layer 42 of the silicon substrate 4 is the collector, which is N-type silicon with a thickness of 420 μm and a resistivity of 0.01 Ω·cm, and the upper layer 41 is a thickness of 60 μm. 35Ω·cm N-type silicon. A plurality of parallel elongated grooves 5 are formed on the upper surface of the silicon substrate 4, the distance between two adjacent grooves 5 is 20 μm, and the depth of the grooves 5 is 3 μm. The bottom of the groove is implanted with boron ions and pushed forward to form a P-type high-concentration groove-shaped gate region 6, and the surface concentration of boron is IE19-2E20 / cm 3 , a junction depth of 10 μm. The upper surface of the upper layer 41 of the silicon substrate is implanted and diffused with boron ions to form a P-type base region 2, and the surface concentration of boron in the P-type base region 2 is 1E17-3E18 / cm 3 , a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More