Dual-bus visual processing chip architecture

A visual processing, dual-bus technology, applied in image data processing, image data processing, instruments, etc., can solve the problems of poor scalability, insufficient memory bandwidth, low average communication efficiency, etc., and achieve the effect of perfect synchronization function

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] The present invention will be described in detail below in conjunction with the accompanying drawings and specific embodiments.

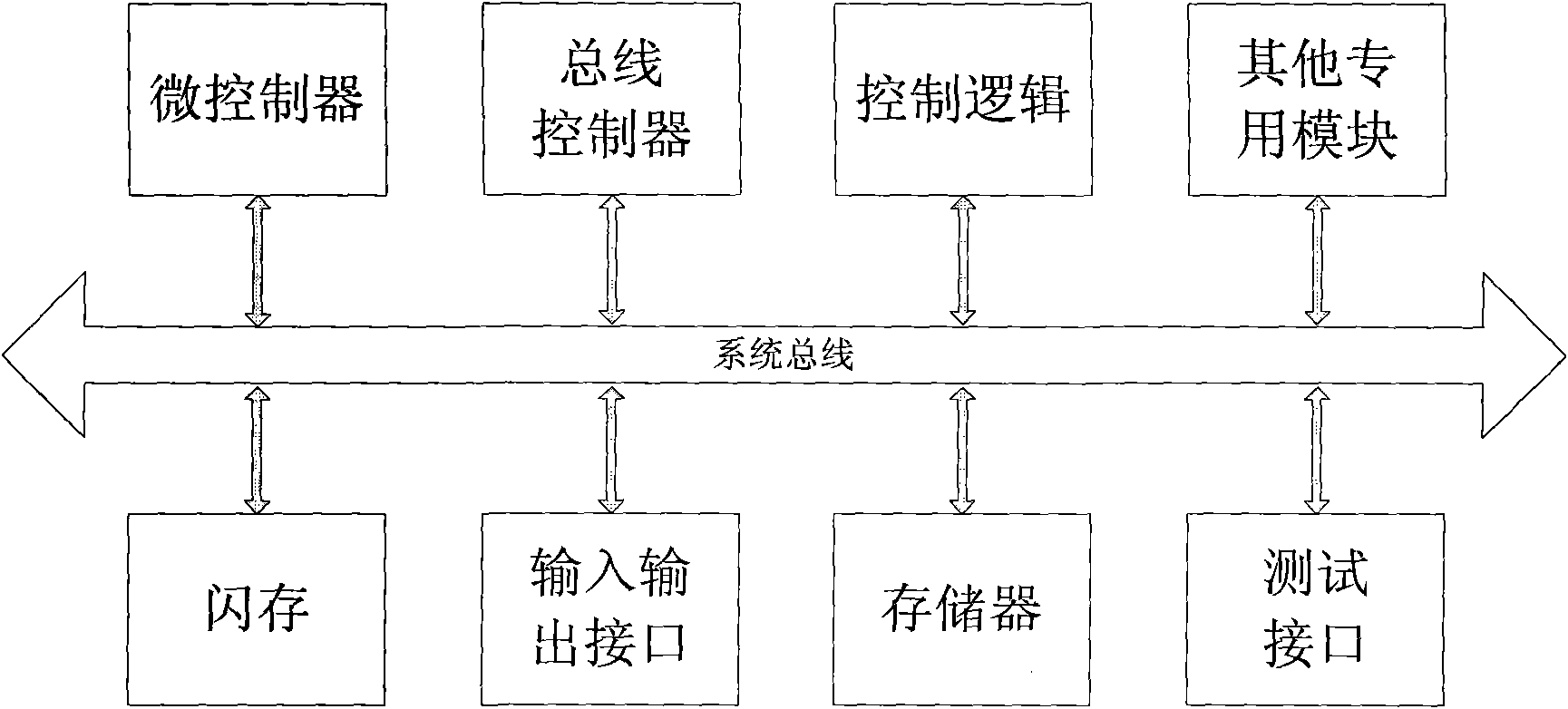

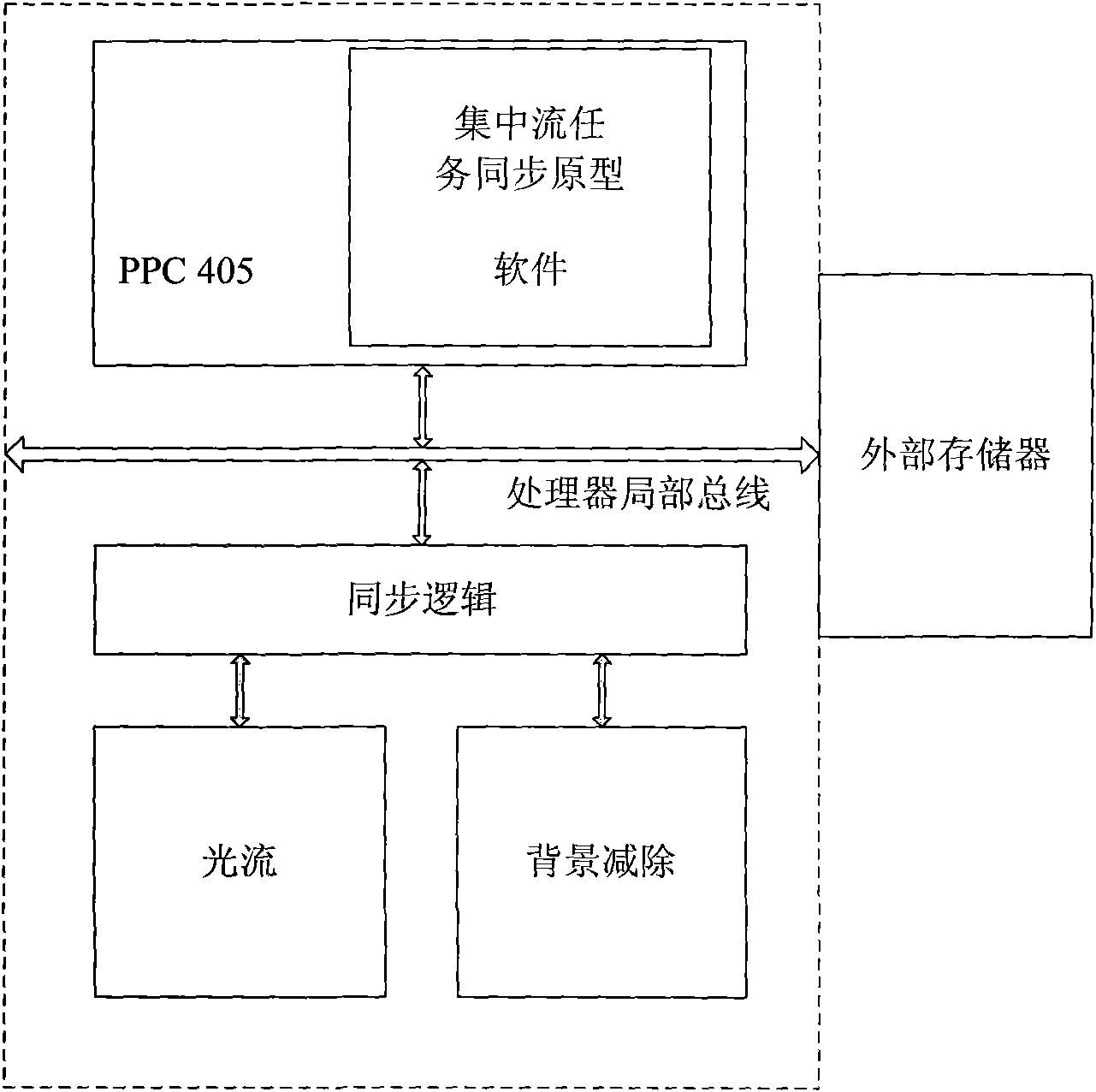

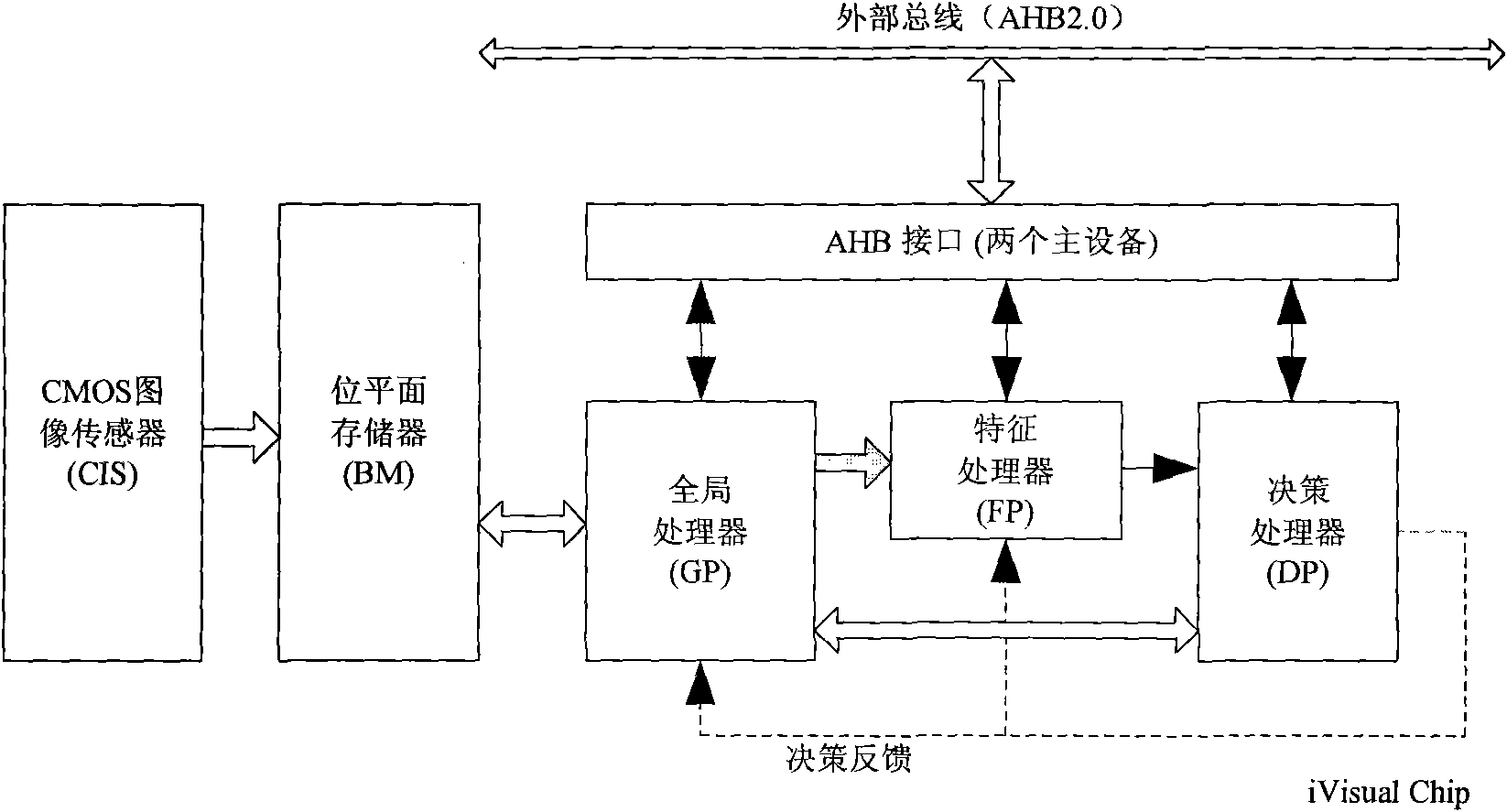

[0024] refer to Figure 4 , the visual processing chip architecture of the dual bus of the present invention mainly includes: a first bus, a second bus, a visual calculation and decision module connected on the first bus, a first memory connected on the first bus, a first memory connected on the second bus, A feature combination and pattern generation module on the bus, an image feature extraction module connected to the second bus, a second memory connected to the second bus, and a bridge circuit connected to the first bus and the second bus.

[0025] The image feature extraction module performs correction and filtering, feature map extraction, down-sampling and non-uniform sampling on video signals, and completes the underlying processing in visual processing. The feature combination and pattern generation module calculates and recombines ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More