Encapsulating structure and encapsulating method of chip

A chip packaging structure and packaging method technology, which is applied in the manufacturing of electrical components, electrical solid-state devices, semiconductor/solid-state devices, etc., can solve problems such as increasing resistance value, inability to align, and affecting chip performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

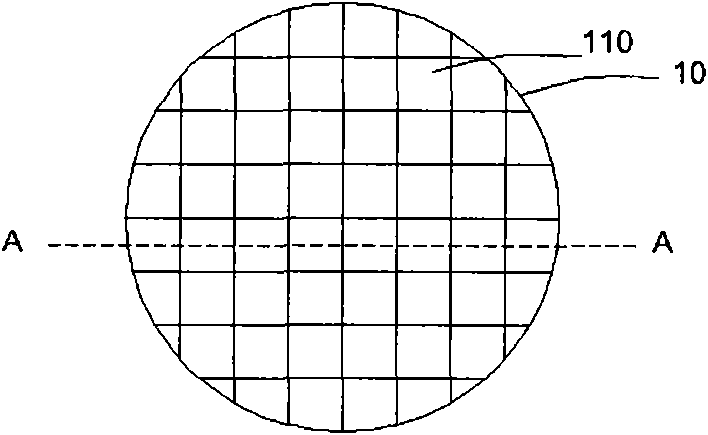

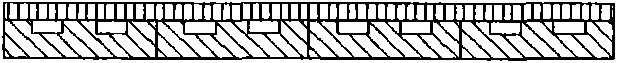

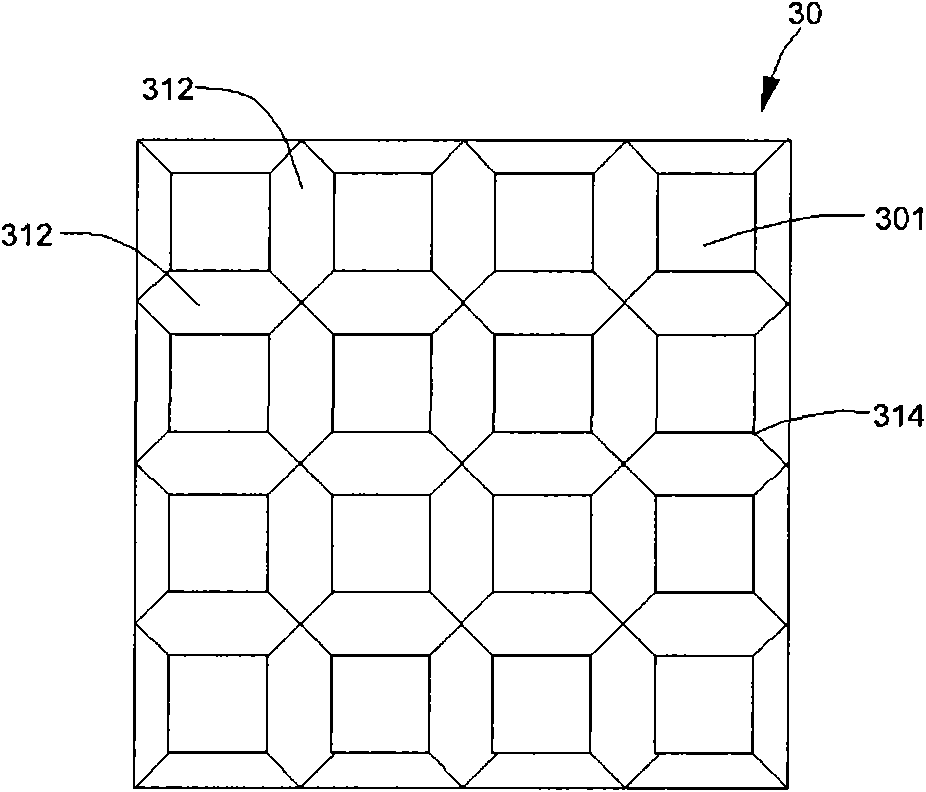

[0033]The direction of the present invention discussed here is a chip reconfiguration packaging method, in which multiple chips are reconfigured on another substrate and then packaged. In order to provide a thorough understanding of the present invention, detailed steps and components thereof will be set forth in the following description. Clearly, the practice of the invention is not limited to the specific details of the manner in which chips are stacked that are familiar to those skilled in the art. On the other hand, the well-known chip formation method and detailed steps of chip thinning and other back-end processes are not described in detail to avoid unnecessary limitations of the present invention. However, for the preferred embodiments of the present invention, it will be described in detail as follows, but in addition to these detailed descriptions, the present invention can also be widely implemented in other embodiments, and the scope of the present invention is no...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More