Clock data recovery circuit, method and test device utilizing them

A clock data recovery and testing device technology, applied in electronic circuit testing, measuring devices, synchronization devices, etc., can solve problems such as inability to obtain phase information correctly, inability to estimate the amount of serial data jitter, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Hereinafter, the present invention will be described based on preferred embodiments with reference to the drawings. The same or equivalent structural elements, components, and processes shown in the drawings are denoted by the same symbols, and overlapping descriptions are appropriately omitted. In addition, the embodiment is not an illustration to limit the invention, and all the features or combinations thereof described in the embodiment are not necessarily the essential content of the invention.

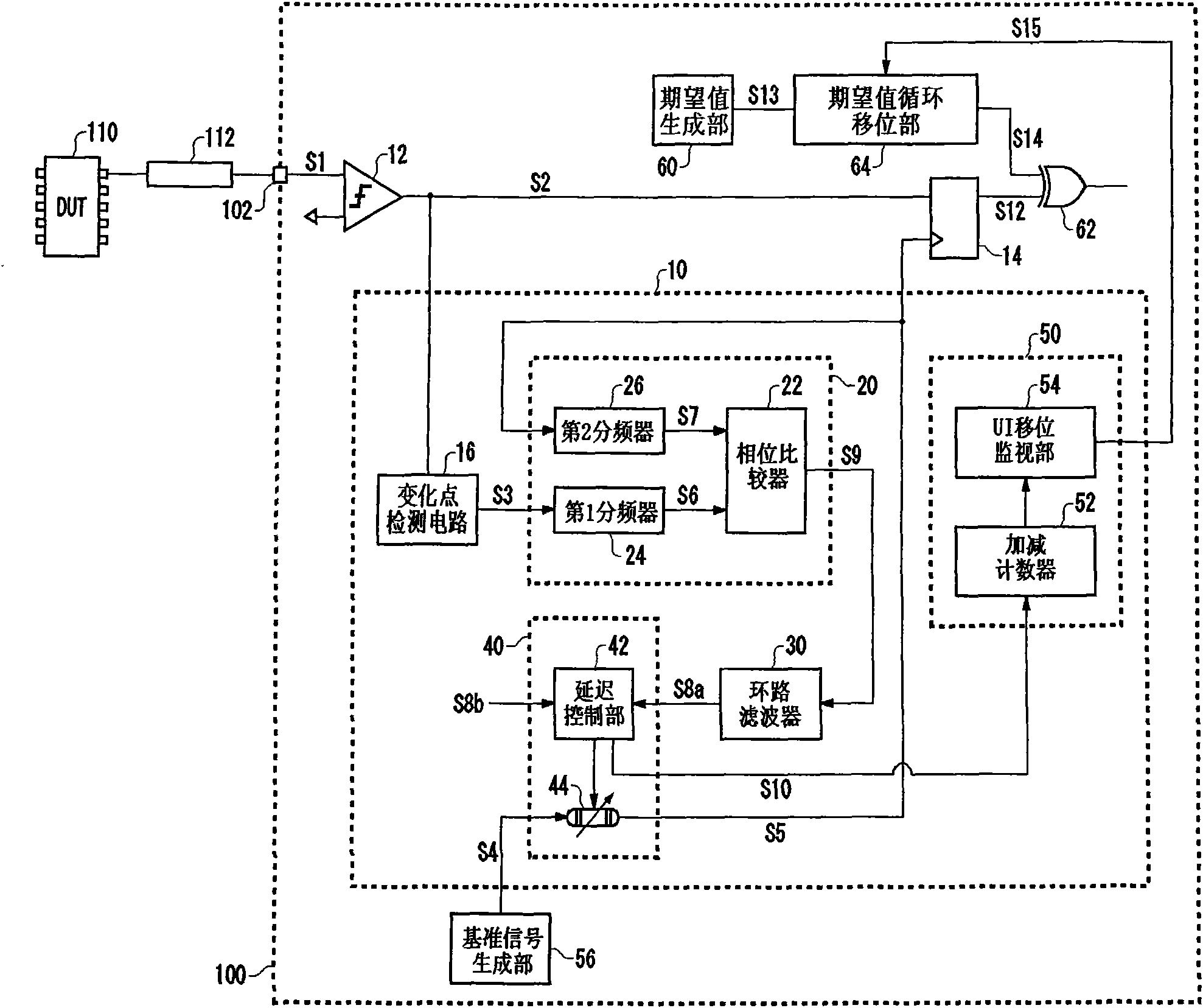

[0033] figure 1 It is a block diagram showing the configuration of a test device 100 using the clock data recovery circuit 10 according to the embodiment of the present invention. The test device 100 receives the serial data S1 output from the DUT 110 connected via the transmission line 112 , and checks the DUT 110 by comparing with the expected value data S13 .

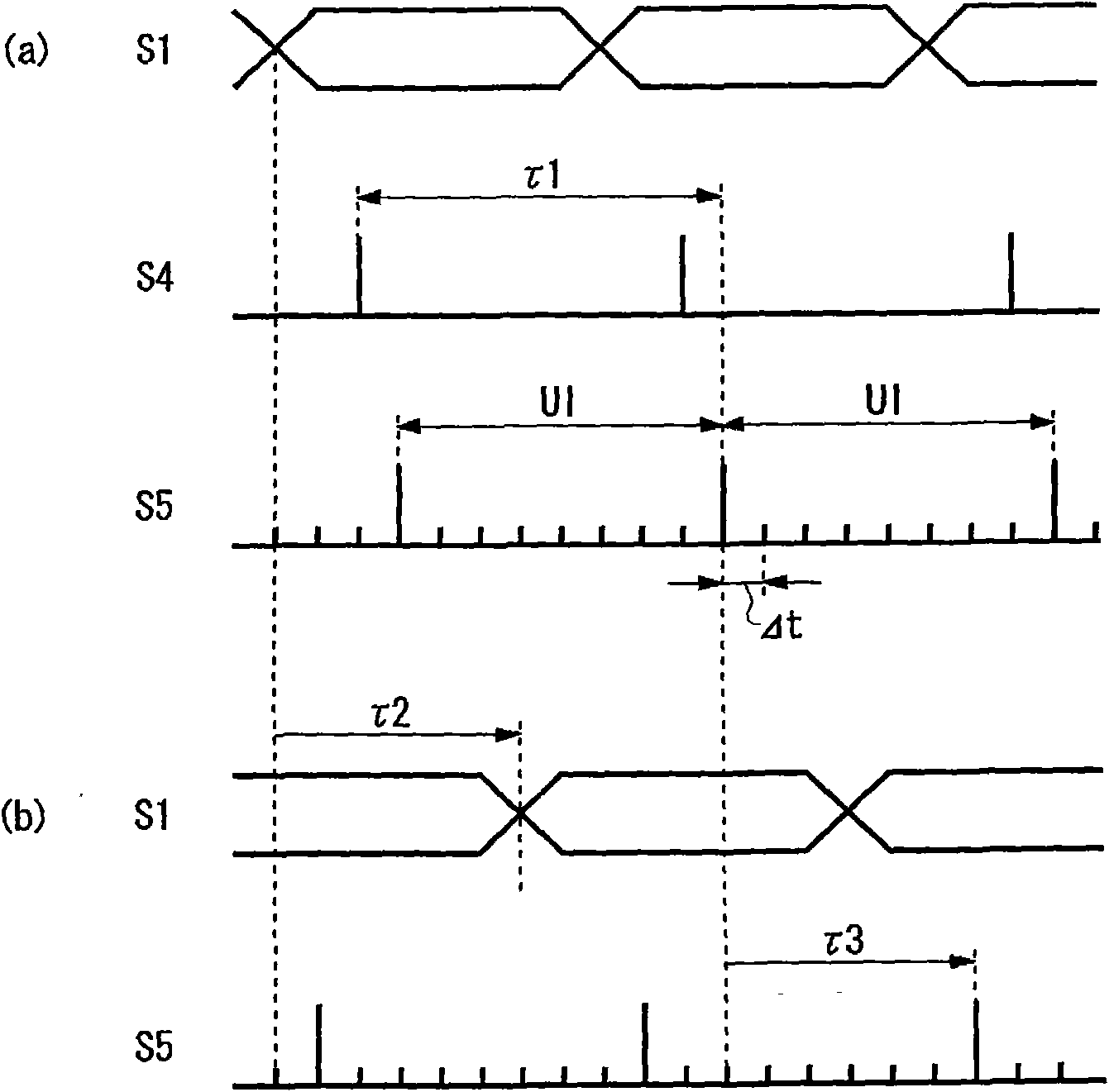

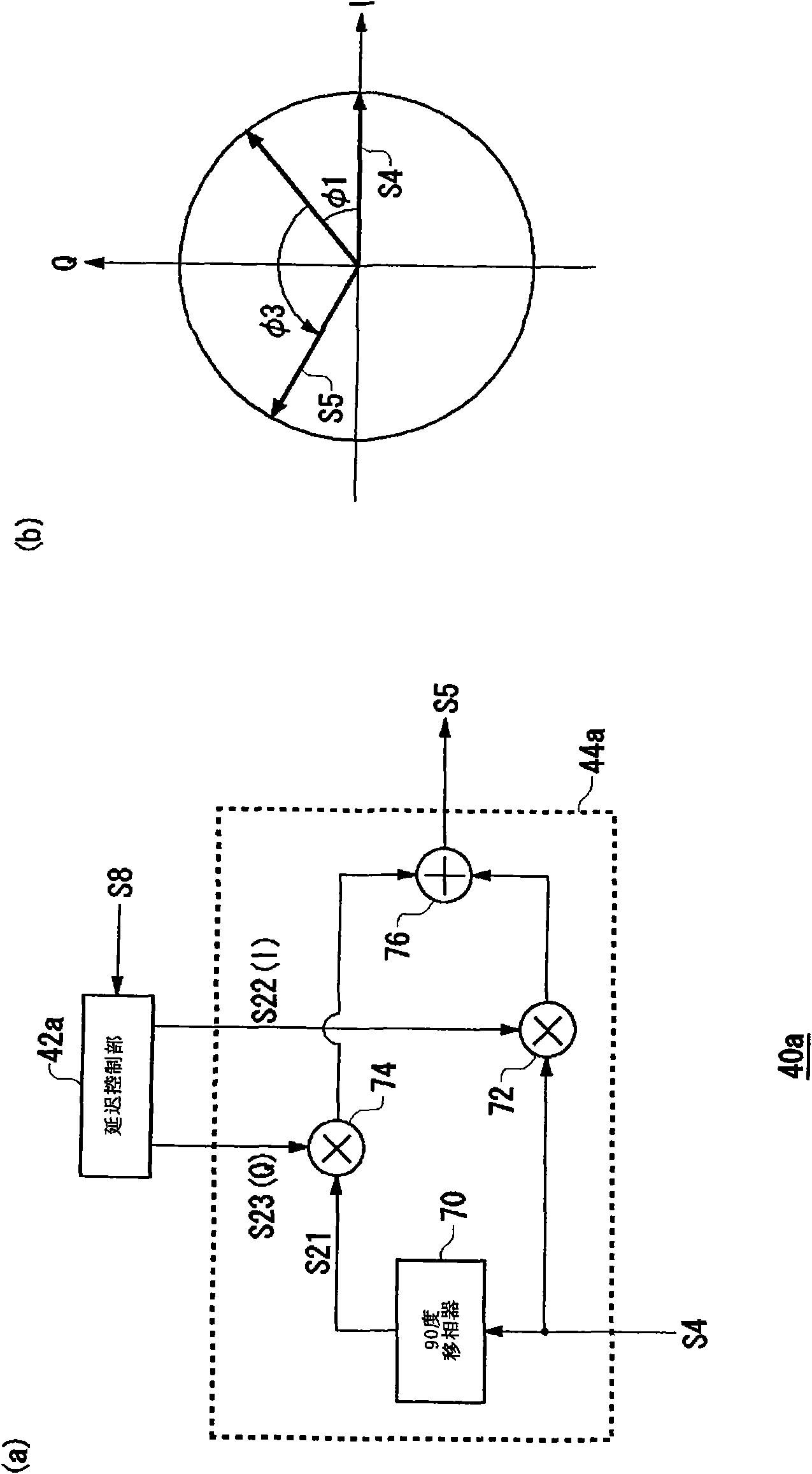

[0034] First, an outline of the overall configuration of the test device 100 will be described. The test de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More