Low power consumption folded interpolating analog-to-digital converter for sharing sub-converters

An analog-to-digital converter, folding and interpolation technology, applied in the direction of analog-to-digital converter, analog/digital conversion, code conversion, etc., can solve the problems of multiple hardware overhead and power consumption, and achieve power saving and hardware overhead saving , The effect of low circuit power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] Further describe the present invention below in conjunction with accompanying drawing.

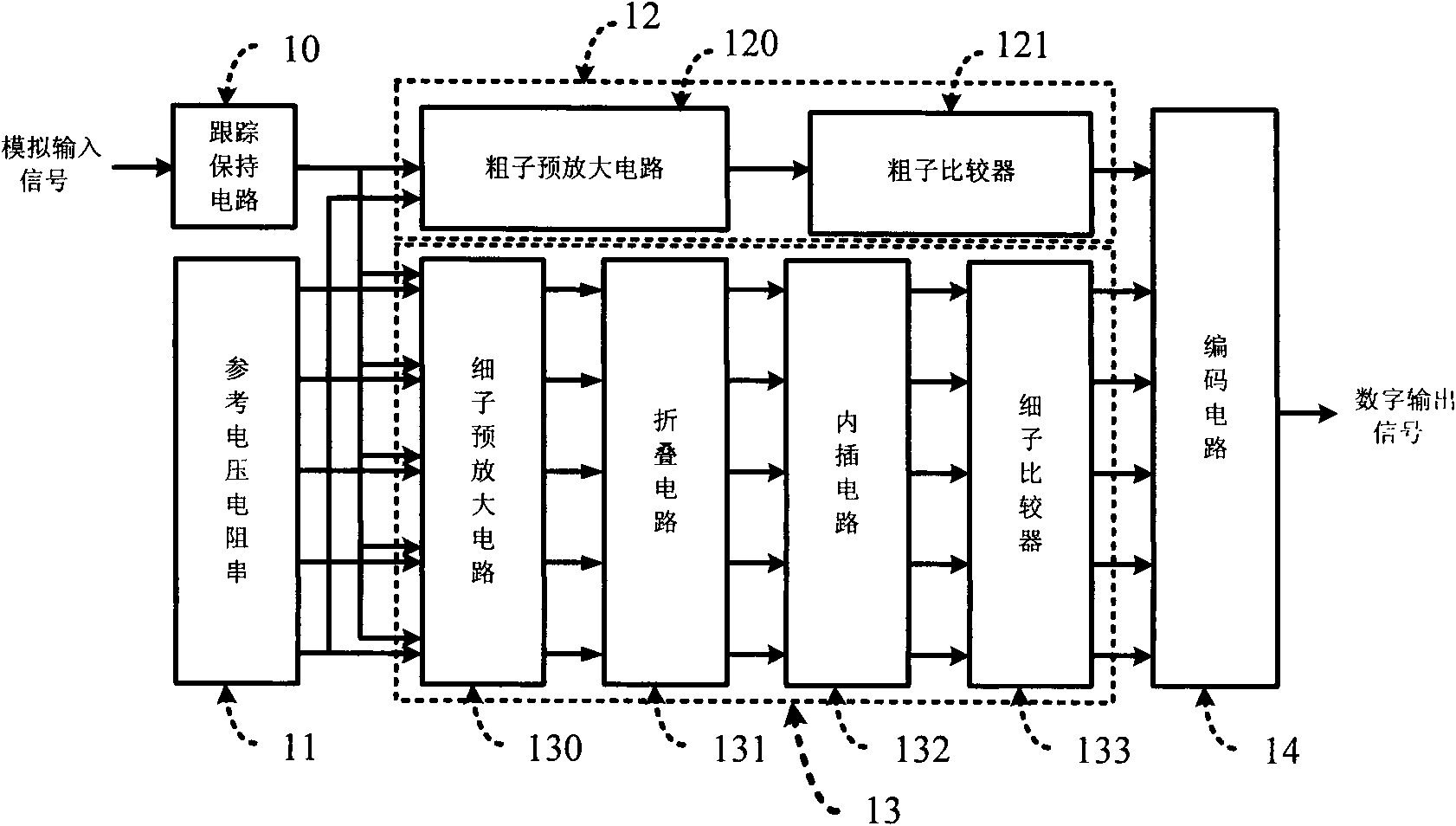

[0028] Figure 5 It shows the folded interpolation analog-to-digital converter shared by the sub-converters proposed by the present invention, which consists of a track and hold circuit 50, a reference voltage resistor string 51, a pre-amplification circuit 52, an N-level cascaded folding circuit 53, an interpolation circuit 54, a comparison device 55 and encoding circuit 56. Its working principle is:

[0029] (1) The analog input signal passes through the track and hold circuit 50 to obtain a hold signal.

[0030] (2) The reference level produced by the holding signal and the reference voltage resistor string 51 is used as the input signal of the pre-amplification circuit 52, and the output of the pre-amplification circuit is a differential amplification signal between the holding signal and the reference level, and the output of the pre-amplification circuit The signal is the i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More