Mixed numerical system summator

An adder and mixed number technology, which is applied to calculations using number system representations, calculations using non-contact manufacturing equipment, etc., to achieve the effects of simple processing flow, low power consumption, and simple unit structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to understand the present invention more clearly, the present invention will be further described in detail below in conjunction with the accompanying drawings.

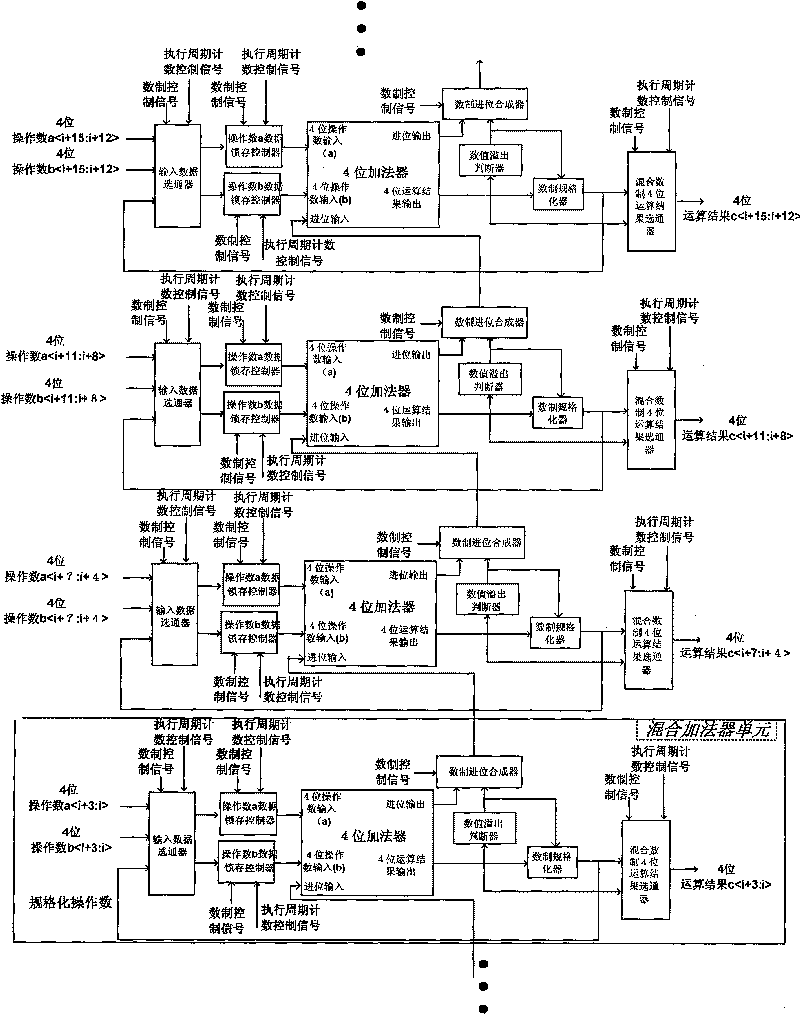

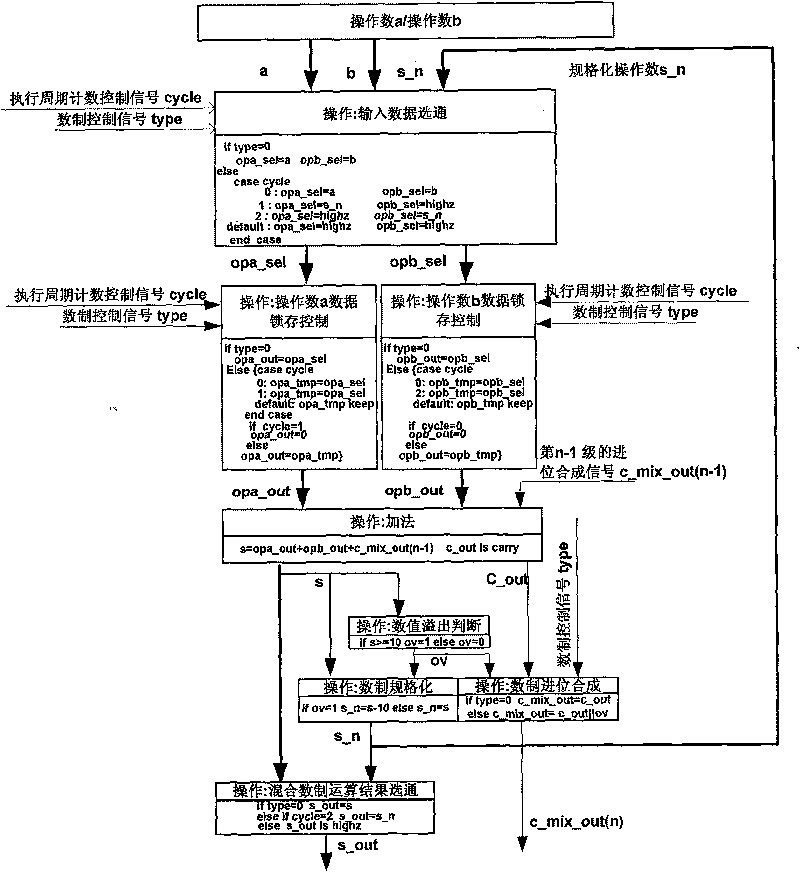

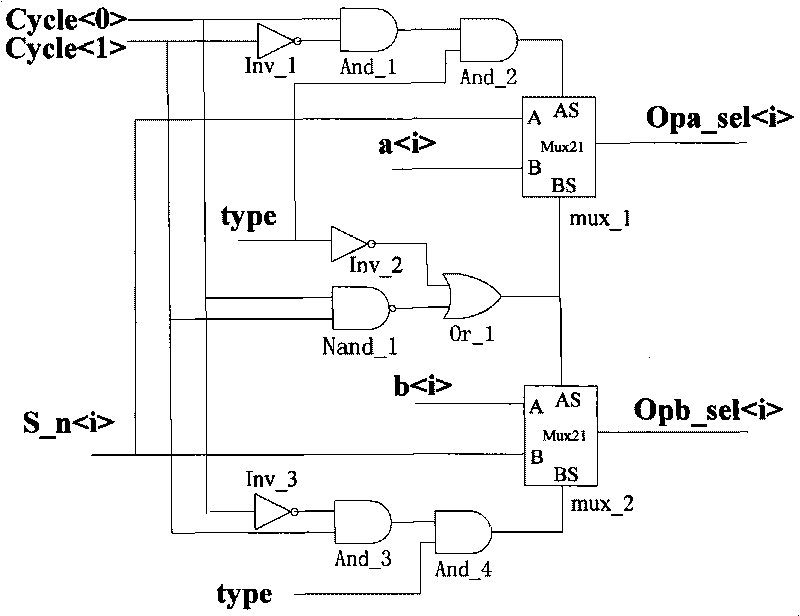

[0030] Such as figure 1 As shown, the mixed number system adder is mainly composed of a mixed adder unit, and realizes a mixed adder of n (n=4i, wherein i=1, 2, 3, 4, 5...) bits, It needs to be composed of n / 4 mixed adder units, and the carry method adopts the wave carry from low to high, that is, the output of the digital carry synthesizer of the low-order mixed adder unit is connected to the 4-bit addition of the adjacent high-order mixed adder unit The carry input terminal in the register. A mixed adder unit can realize the addition operation of a group of 4-bit binary numbers and the operation of decimal numbers represented by a group of 4-bit BCD codes. A hybrid adder unit consists of an input data strobe, an operand a data latch controller, an operand b data latch controller, a 4-bit adder, a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More