Shared memory architecture-based multiprocessor communication device and method thereof

A shared memory, multi-processor technology, applied in the direction of electrical digital data processing, computers, digital computer parts, etc., can solve the problems that cannot meet the needs of airborne computers, and achieve the effect of a wide range of applications

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0047] A multiprocessor communication device based on a shared memory structure, including a first CPU and a second CPU, a section of specific memory space on the first CPU is mapped to the PCI address space of the second CPU, to realize the shared memory access.

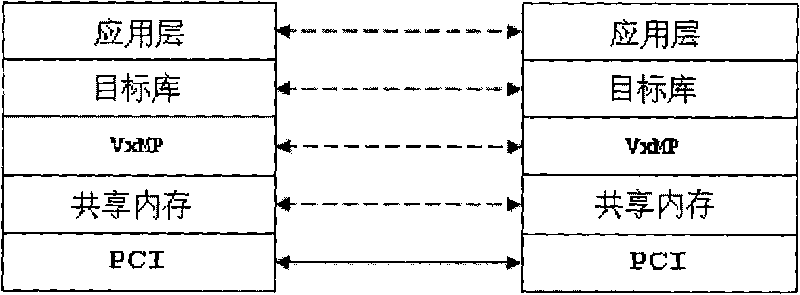

[0048] The shared object communication between two CPUs is as follows: figure 1 Shown:

[0049] Each CPU includes application layer (Application), object library (Object Library), VxMP, shared memory (Shared Memory), and PCI bus.

[0050]The multiprocessor communication device based on the shared memory structure provided by the present invention can be used as a realization principle prototype of shared memory objects among distributed multi-tasks independent of the hardware platform. All calls based on this component are standard objects in the VxWorks operating system, and the underlying hardware distribution structure is completely transparent to the upper application. At the same time, this component also vi...

Embodiment 2

[0081] A multiprocessor communication method based on a shared memory structure, adopting the multiprocessor communication device based on the shared memory structure of the above-mentioned embodiment 1, comprising:

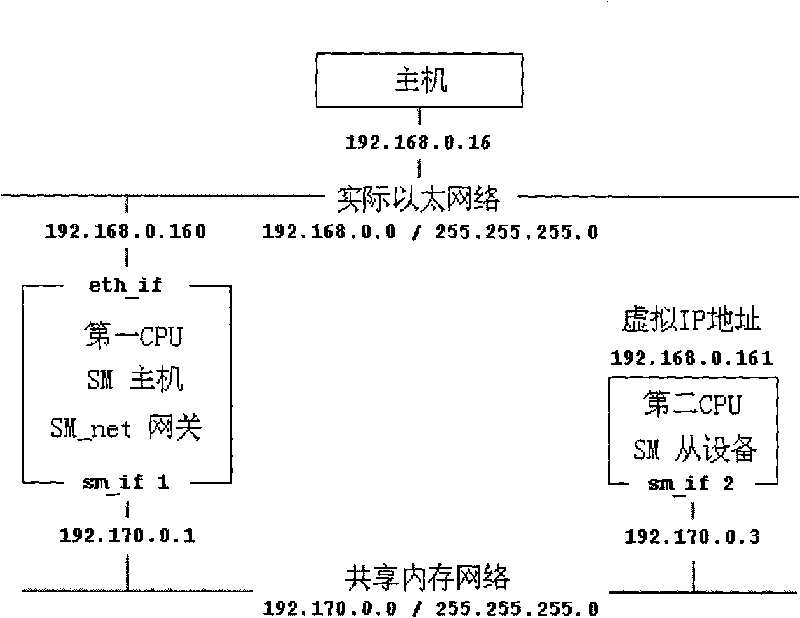

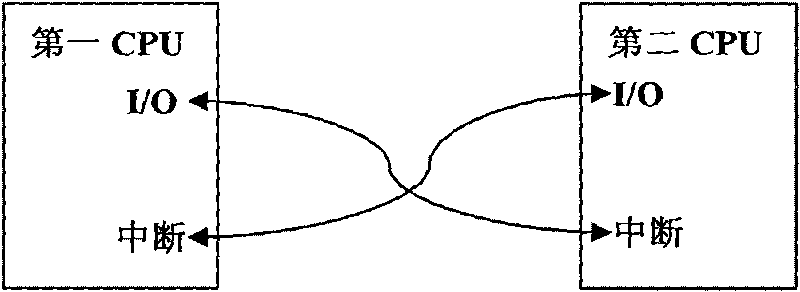

[0082] The first CPU and the second CPU, a section of memory space on the first CPU is mapped to the PCI address space of the second CPU to form a linear shared memory space that can be accessed by both the first CPU and the second CPU; shared The memory space is provided with an address space for transmitting Ethernet packets between the first CPU and the second CPU and an address space for shared objects between multiple tasks on the first CPU and the second CPU; the first CPU uses The shared local memory address space is linearly mapped to the PCI bus address space; the second CPU linearly maps the shared address space on the PCI bus to the local memory address space of the first CPU, and the first CPU and The second CPUs access data from each other through li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More