Encapsulation structure for wafer backside

A technology of packaging structure and crystal back, which is applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problem of increasing the process cost of depositing silicon dioxide layer, and achieve the effect of promoting gettering effect, saving process cost and preventing automatic doping Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

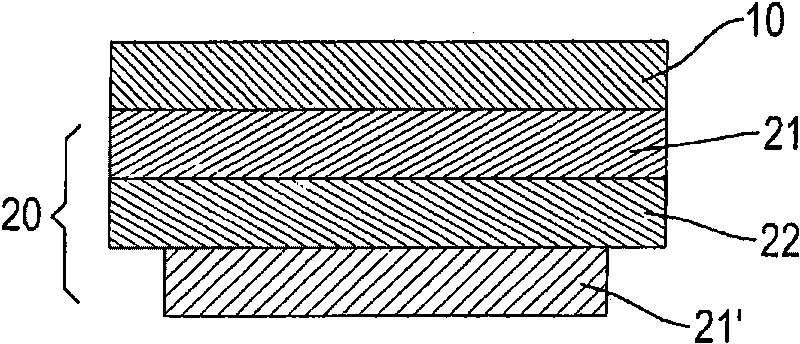

[0043] Please see figure 1 Shown is the first embodiment of the packaging structure of the crystal back of the present invention, which includes:

[0044] A semiconductor substrate 10, which can be silicon, germanium or other semiconductors, the bottom of which can first undergo backside damage (BSD), which uses mechanical force to damage the crystal back to achieve the effect of removing impurities. For the method, reference may be made to US Patent No. 5,006,475, US Patent No. 5,066,359 and China Taiwan Publication No. 200820332 "Silicon Wafer with High Gettering Capability and High Flatness and Manufacturing Method thereof".

[0045] A multi-layer structure layer 20, which comprises two layers of silicon dioxide layers 21, 21' and a polysilicon layer 22 arranged between said silicon dioxide layers 21, 21', wherein a silicon dioxide layer 21 is directly arranged At the bottom of the semiconductor substrate 10, the polysilicon layer 22 is disposed on a surface of the silicon...

no. 2 example

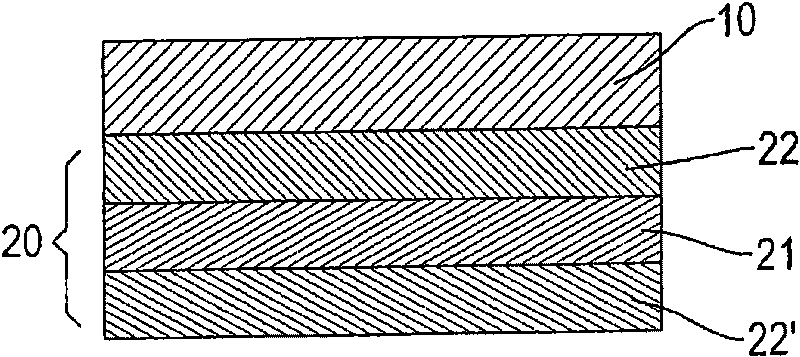

[0047] Please see figure 2 Shown is the second embodiment of the packaging structure of the crystal back of the present invention, which includes:

[0048] A semiconductor substrate 10, which can be silicon, germanium or other semiconductors, the bottom of which can first undergo backside damage (BSD), which uses mechanical force to damage the crystal back to achieve the effect of removing impurities. For the method, reference may be made to US Patent No. 5,006,475 and Taiwan Patent Publication No. 200820332 "Silicon Wafer with High Gettering Capability and High Flatness and Manufacturing Method thereof".

[0049] A multi-layer structure layer 20 includes two layers of polysilicon layers 22, 22' and a silicon dioxide layer 21 disposed between the polysilicon layers 22, 22', wherein a polysilicon layer 22 is directly disposed on the semiconductor substrate 10 At the bottom, the silicon dioxide layer 21 is disposed on a surface of the polysilicon layer 22 different from the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More