On-chip antenna structure in integrated circuit and manufacturing method thereof

A technology of an on-chip antenna and a manufacturing method, which is applied in the direction of a loop antenna with a ferromagnetic material core, a circuit, and a radiating element structure, etc. Due to the large size of the antenna, the effects of wide process adaptability, reduced size, and increased impedance bandwidth are achieved.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] In order to make the technical features of the present invention more comprehensible, specific embodiments are given below in conjunction with the accompanying drawings to further describe the present invention.

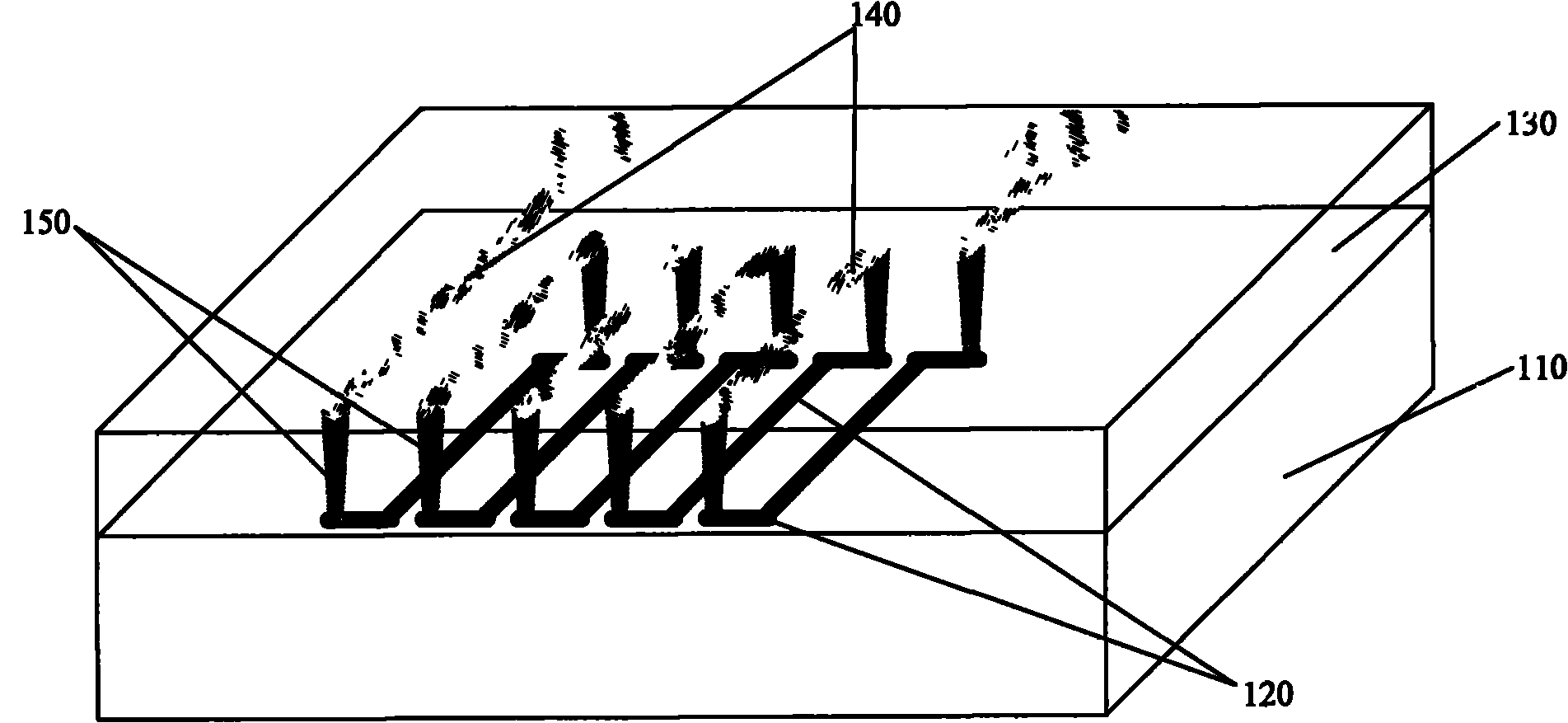

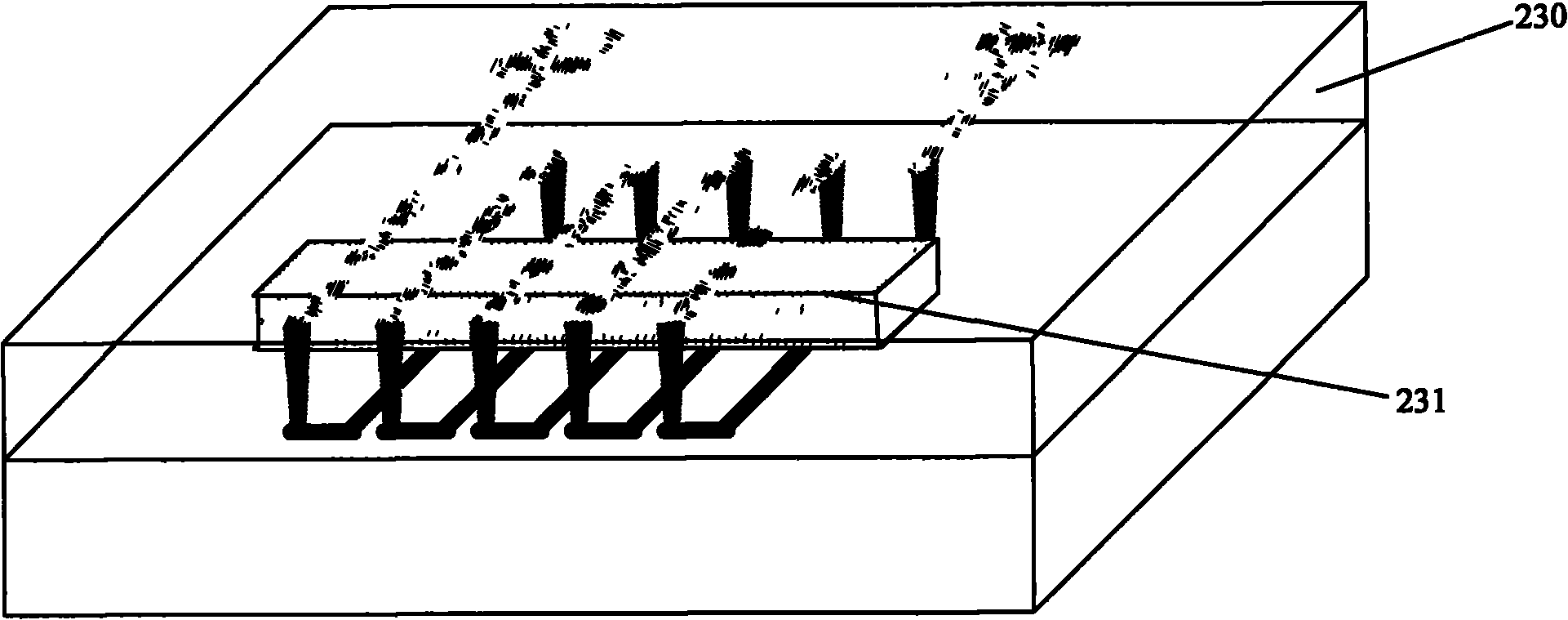

[0039] See figure 1 , shows a schematic structural diagram of an on-chip antenna in an integrated circuit provided by an embodiment of the present invention.

[0040] The on-chip antenna includes: a semiconductor substrate 110; a first metal wire layer 120 disposed on the semiconductor substrate 110; a dielectric layer 130 disposed on the first metal wire layer 120; a second metal wire layer 140 , disposed on the dielectric layer 130 ; an interlayer connection 150 disposed in the dielectric layer 130 to connect the first metal wire layer 120 and the second metal wire layer 140 . The on-chip antenna adopts a double-layer metal interconnection layer combination structure, which not only increases the radiation volume of the on-chip antenna, but also reduces the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More