Main device for Ethernet system and relevant clock synchronization method thereof

A network system and clock synchronization technology, which is applied in transmission systems, synchronization devices, digital transmission systems, etc., can solve the problems of unable to adjust the clock phase of transmitted data, clock drift, unable to synchronize clocks, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

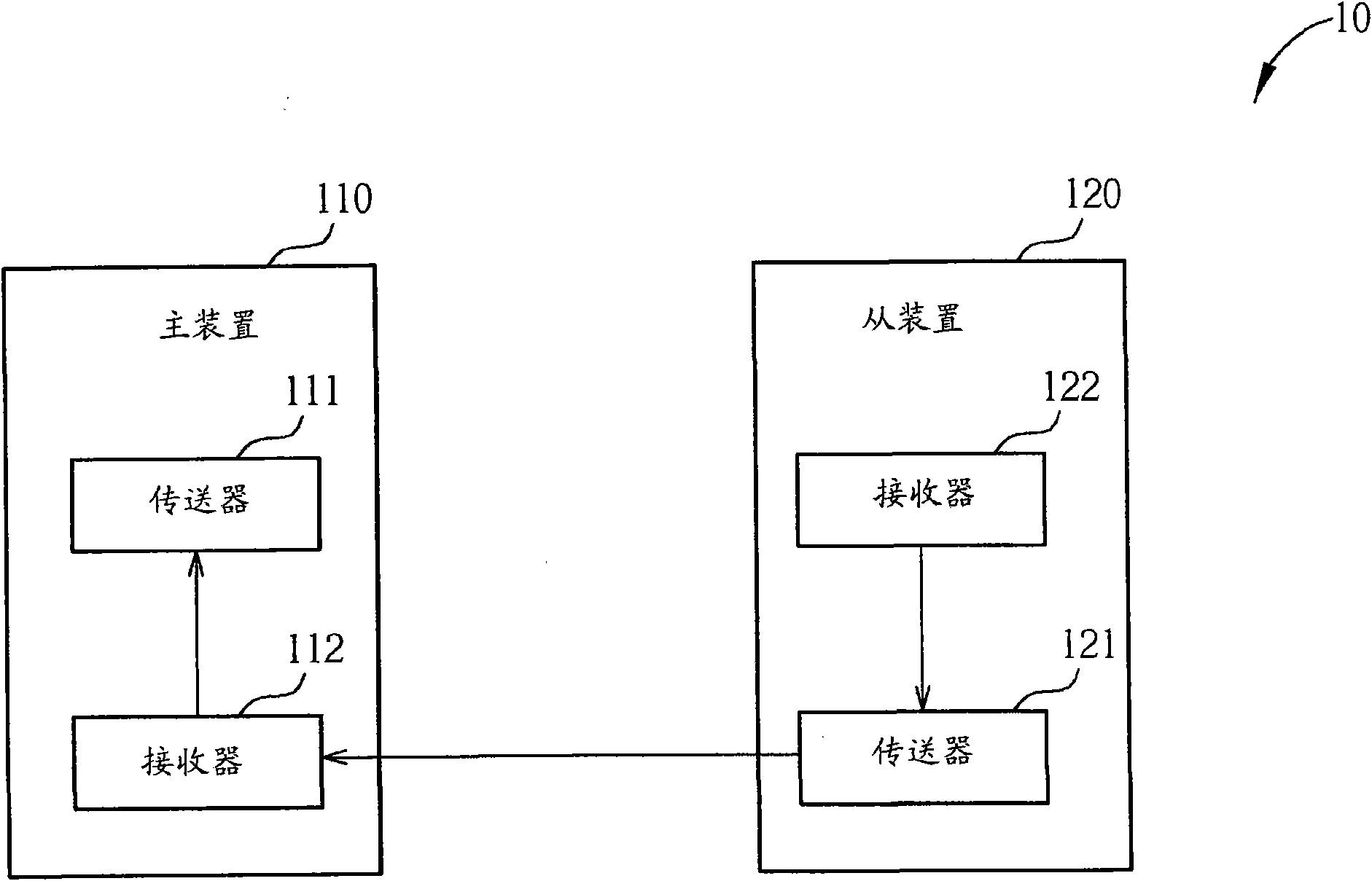

[0044] Please refer to figure 1 , figure 1 It is a schematic diagram of implementing an Ethernet system 10 according to the present invention. The Ethernet system 10 is a Gigabit Ethernet network operating under an asymmetric mechanism. The Ethernet system 10 includes a master device 110 and a slave device 120 . The master device 110 includes a transmitter 111 for transmitting signals, and a receiver 112 for receiving signals from the slave device 120 . The slave device 120 includes a transmitter 121 for transmitting signals to the receiver 112 of the master device 110, and a receiver 122 for receiving signals. When the master device 110 and the slave device perform data transmission, the clock synchronization relationship between the two must be maintained so that the phase state of the receiver at the time of sampling is optimal. That is to say, the clock phases between the master device and the slave device must be the same or maintain a fixed phase difference.

[0045...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More