Chaotic signal generating circuit

A chaotic signal and generating circuit technology, applied in electrical components, secure communication devices, digital transmission systems, etc., can solve problems such as algorithm accuracy and capacity bottlenecks of logic units, large discrete electronic components, and difficulties in circuit design and debugging. , to achieve the effects of easy expansion, strong circuit versatility, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

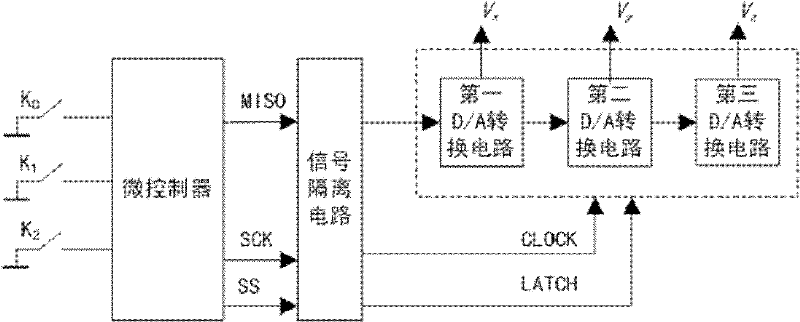

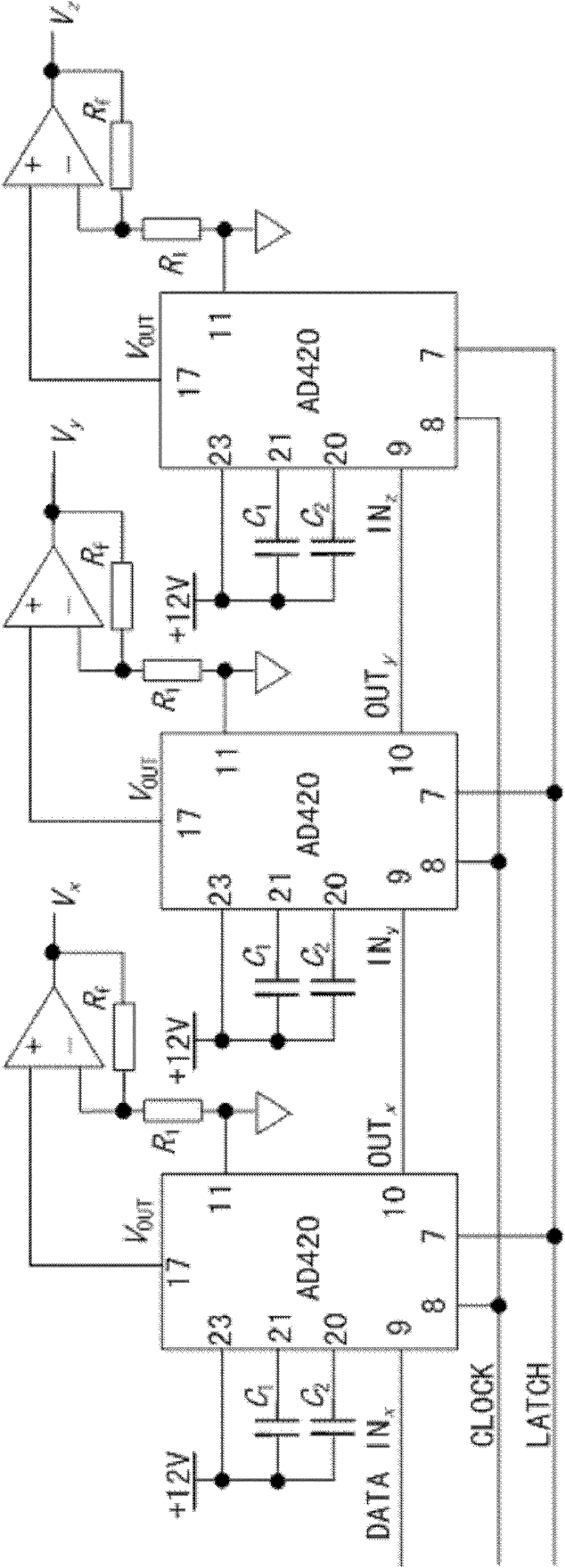

[0021] The chaotic signal generation circuit of this embodiment includes: a microcontroller, a signal isolation circuit, a first D / A conversion circuit, a second D / A conversion circuit and a third D / A conversion circuit.

[0022] Each D / A conversion circuit includes a 16-bit shift register and a 16-bit DAC register, and the shift registers in each D / A conversion circuit are connected in series to form a 48-bit shift register; The serial digital signal MISO output by the SPI interface is sent to the serial data input terminal DATA IN of the first D / A conversion circuit through the signal isolation circuit x The clock signal SCK and the latch control signal SS output by the SPI interface are respectively sent to the clock input terminal CLOCK and the latch control signal input terminal LATCH of each D / A conversion circuit through the signal isolation circuit, so as to realize serial synchronous communication. The SPI interface is a serial peripheral interface.

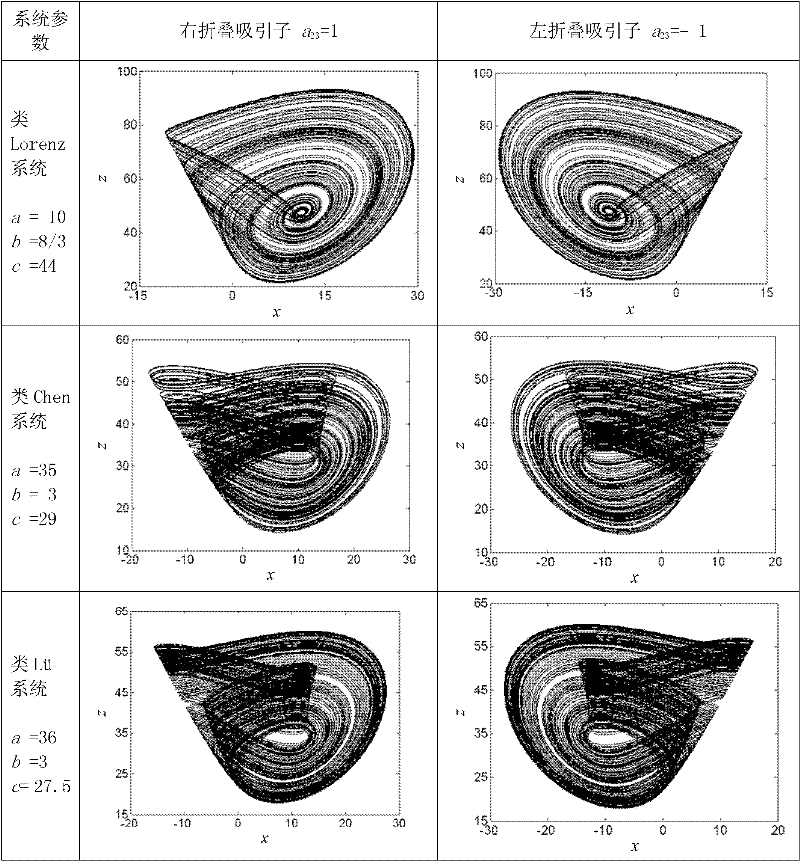

[0023] The math...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More