VLSI (Very Large Scale Integration) structure design method for parallel flowing motion compensating filter

A technology of motion compensation and structural design, applied in the field of video decoding, can solve the problems of large amount of calculation, high time occupied by motion compensation, time-consuming data reading, etc., to reduce access, reduce data bandwidth, and improve efficiency and speed. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

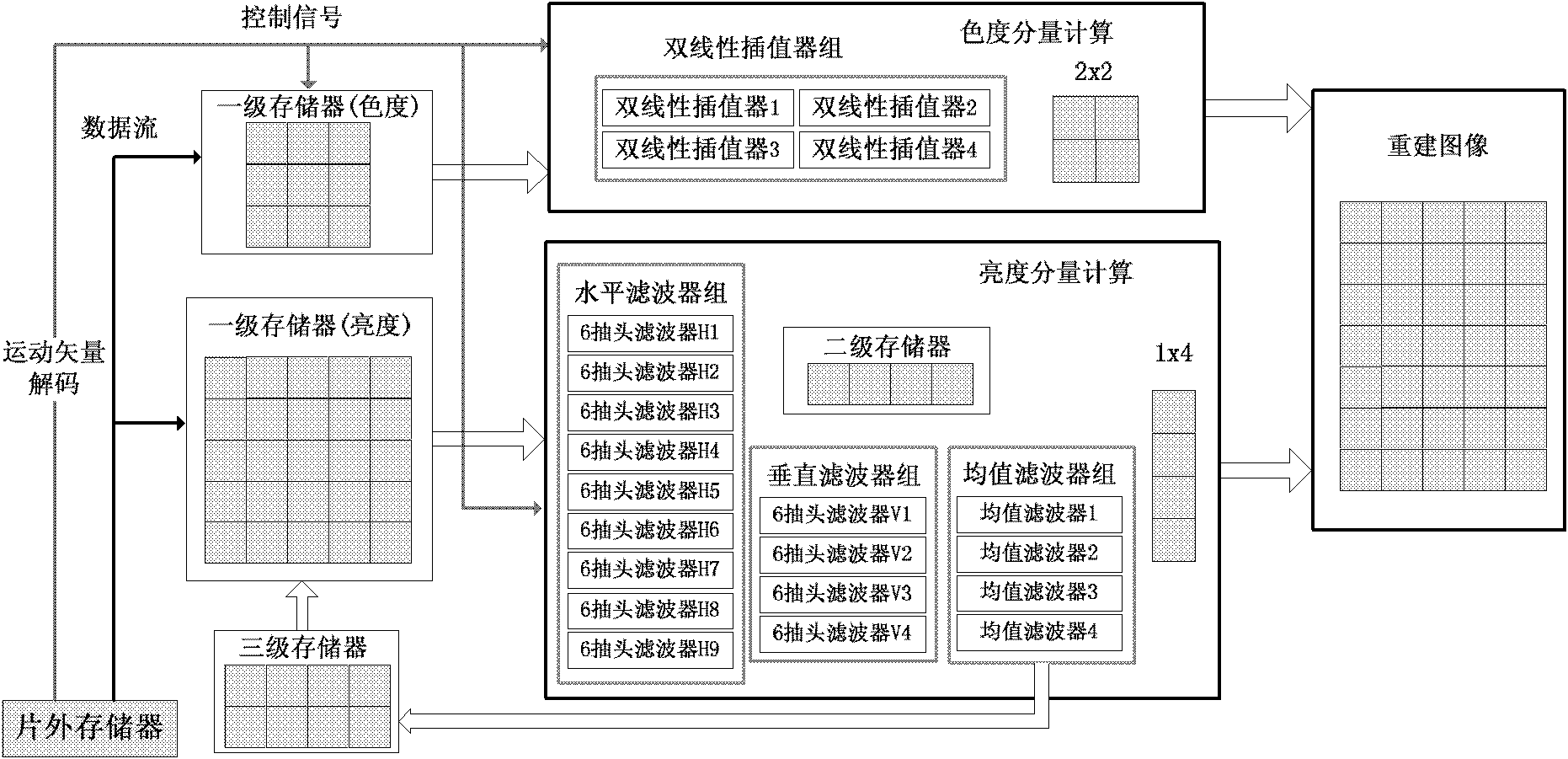

[0020] figure 1 Shown is the overall architecture design of the motion compensation module. As can be seen in the figure, this module can be roughly divided into three parts. The following are introduced separately.

[0021] The first part is the module input and output interface. Among them, the input interface is an off-chip memory, from which information such as reference frame pixel data, motion vector and block division type is read. The output interface is to write the reconstructed current frame data into the external memory, which contains the values of two components of brightness and chrominance.

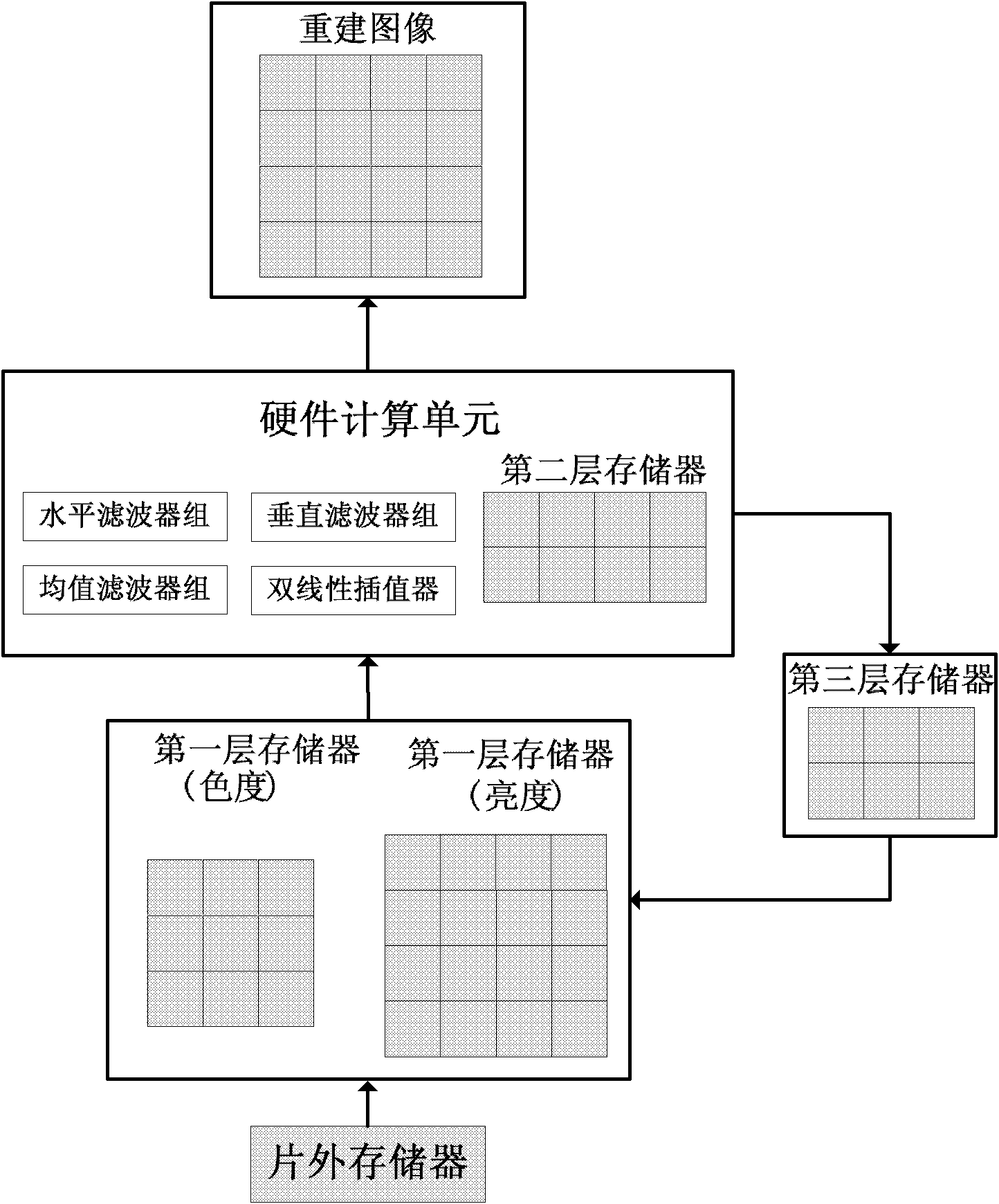

[0022] The second part is the hierarchical on-chip memory, which is used to store the required data read from the external memory. In order to reduce the read bandwidth and improve the data multiplexing rate, at the same time, in order to realize the self-adaptive variable size block processing, this paper adopts a three-layer on-chip buffer structure, including the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More