Method for wafer test and probe card for the same

A technology of wafer testing and probe card, which is applied to the components of electrical measuring instruments, semiconductor/solid-state device testing/measurement, electrical measurement, etc., which can solve the problem of thermal deformation of probe card, deterioration of probe card alignment accuracy and Flatness, unreliable test results and other issues, to achieve the effect of reducing the number of tests and effectively improving the test

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach

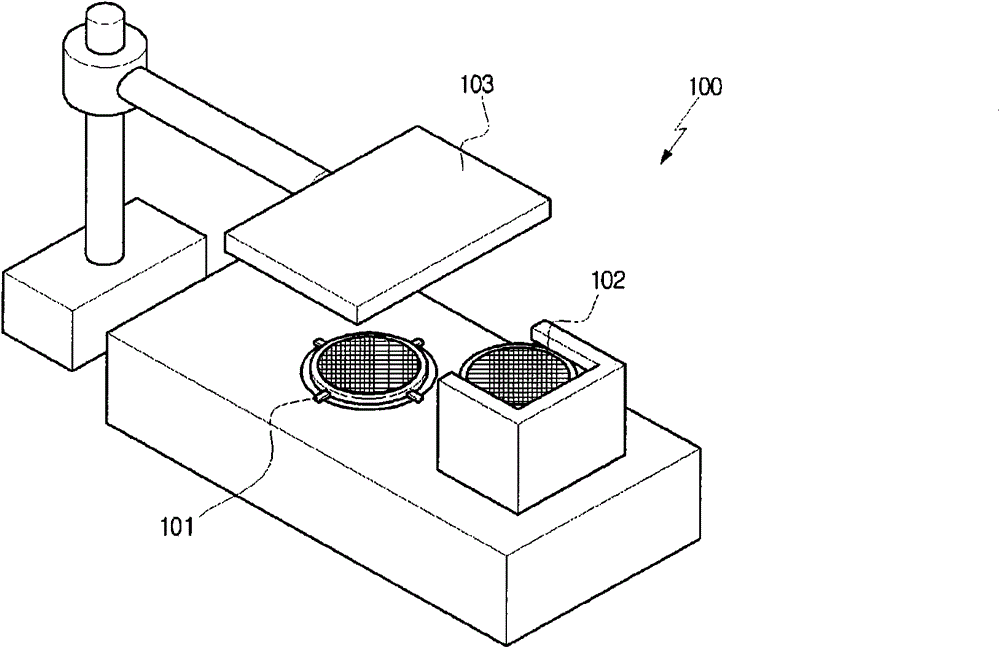

[0044] Hereinafter, a method of testing a wafer according to an embodiment and a probe card used for the method will be described in detail with reference to the accompanying drawings.

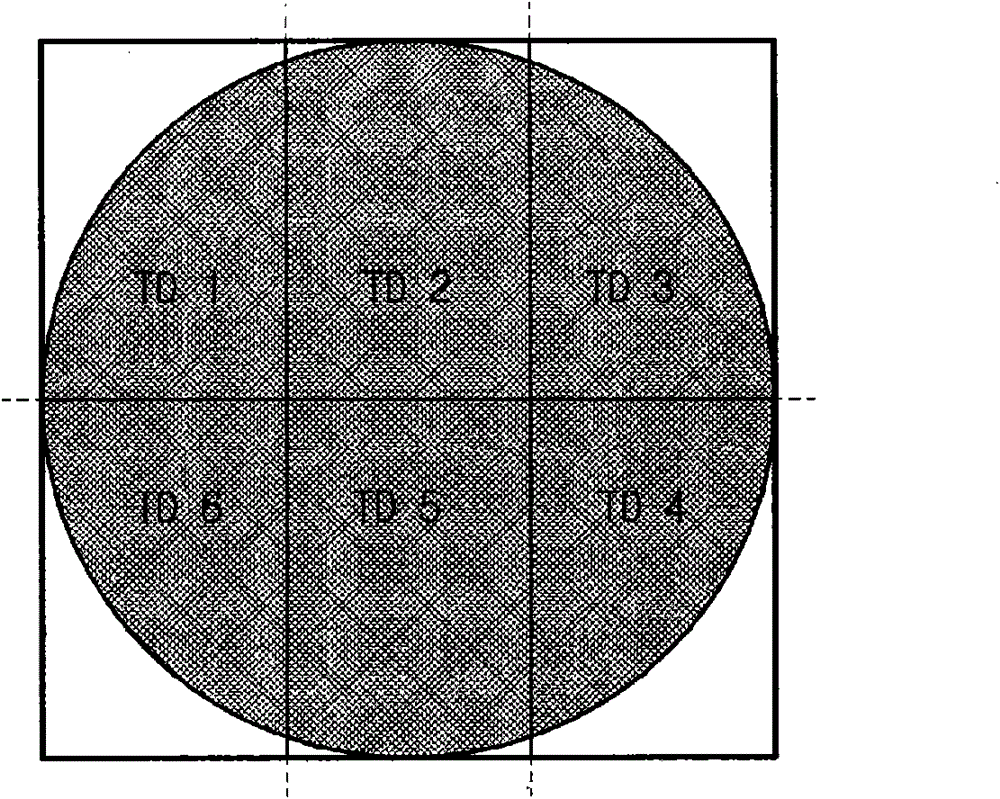

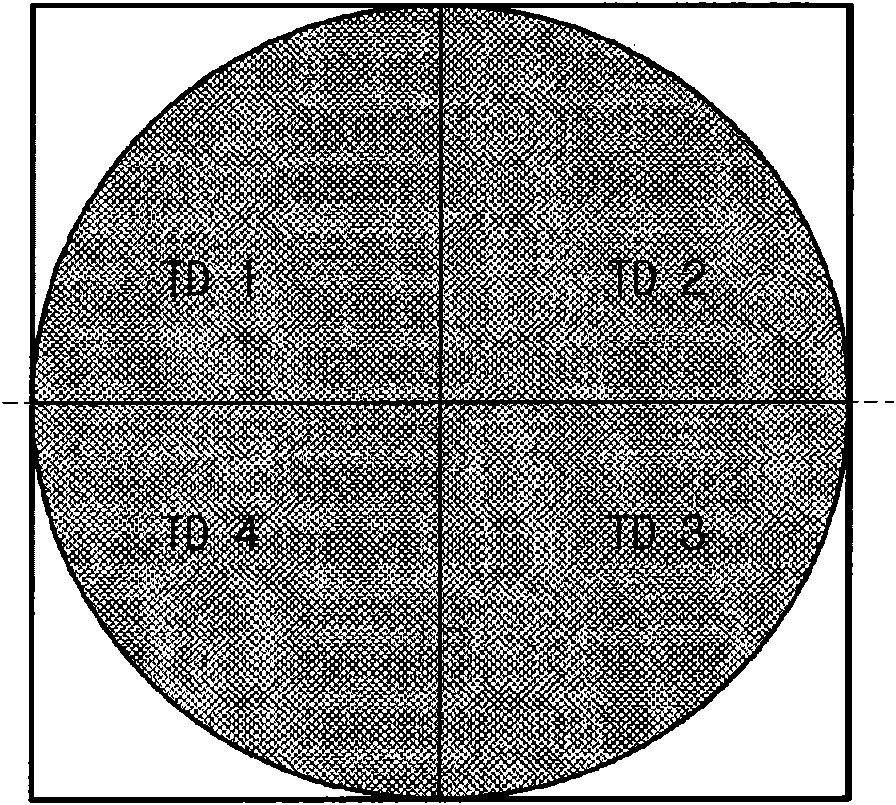

[0045] In order to implement the wafer testing method disclosed herein, firstly, the concept of repeating unit is applied to the semiconductor chips of the wafer to be tested. A plurality of semiconductor chips are arranged on the wafer. A semiconductor chip is defined as a group of repeating units and the repeating unit is defined as a plurality of groups of N adjacent semiconductor chips. N is a natural number not less than 2, for example, N is a natural number between 2 and 50. For example, in Figure 4 Among them, the semiconductor chip C of the wafer 600 can be defined as a set of repeating units 610 composed of four semiconductor chips C. At this point, adjacent repeating units can share some chips. For example, when a first repeating unit and a second repeating unit are defined on a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com