High-speed asynchronous data acquisition system

An asynchronous data and acquisition system technology, applied in the field of data communication, can solve the problem that PLL accuracy cannot be guaranteed, achieve the effect of improving reliability and adaptability, and increasing data acquisition speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

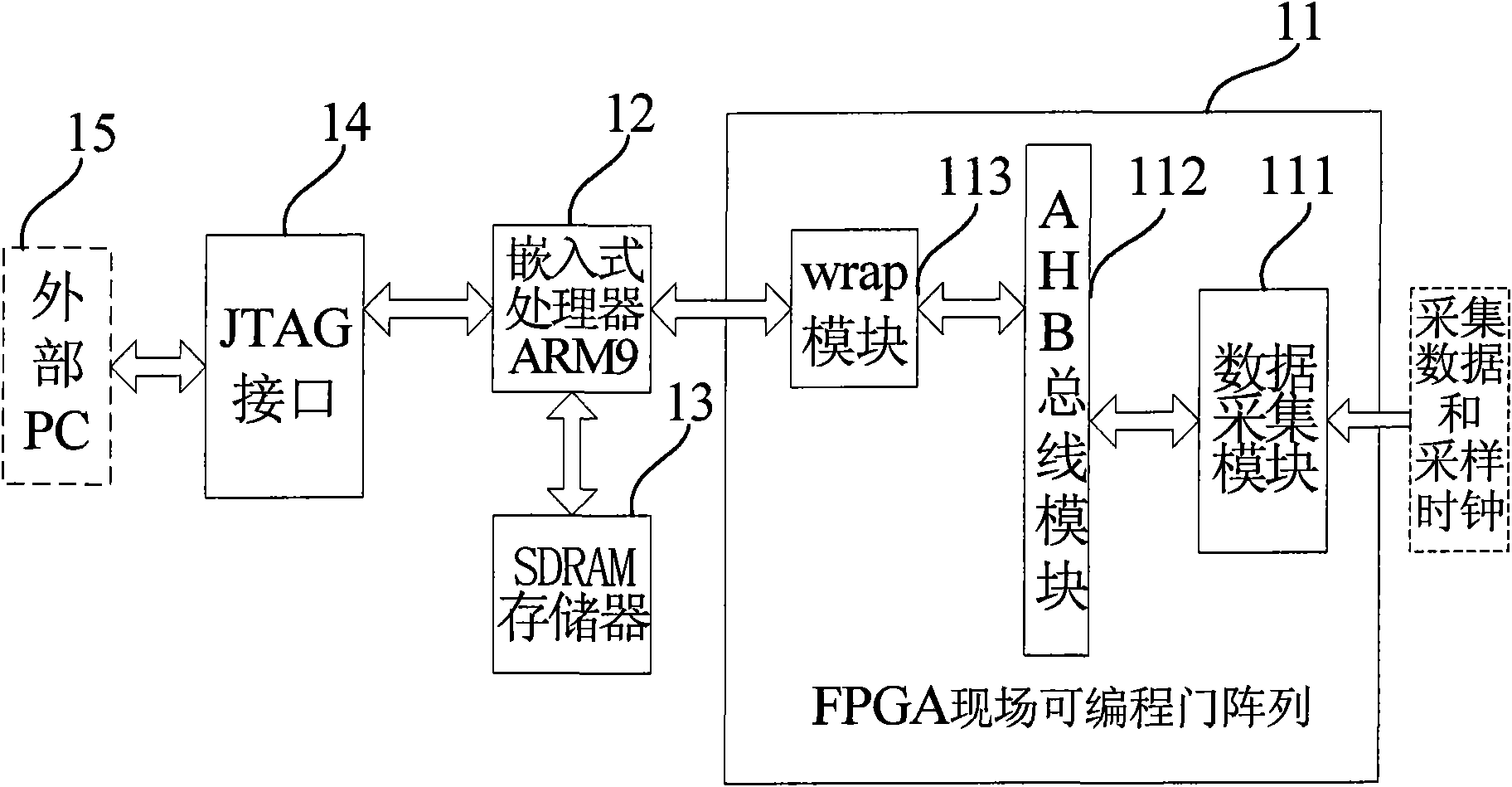

[0045] The configuration of the high-speed asynchronous data acquisition system based on AHB bus of the present invention is: the embedded processor core is the SUMSUNG S3C2410A of ARM920T; The model is EP2C70672C8 of Altera's Cyclone II series; the high-speed asynchronous data transmission instructions based on the AHB bus are issued by the ARM9 processor as the master module, and processed and responded by the data acquisition module as the slave module. The basic main structure of the AHB bus also includes multiplexers from the master module to the slave module and from the module to the master module, as well as decoders, arbitrators, virtual slave modules, and virtual master modules.

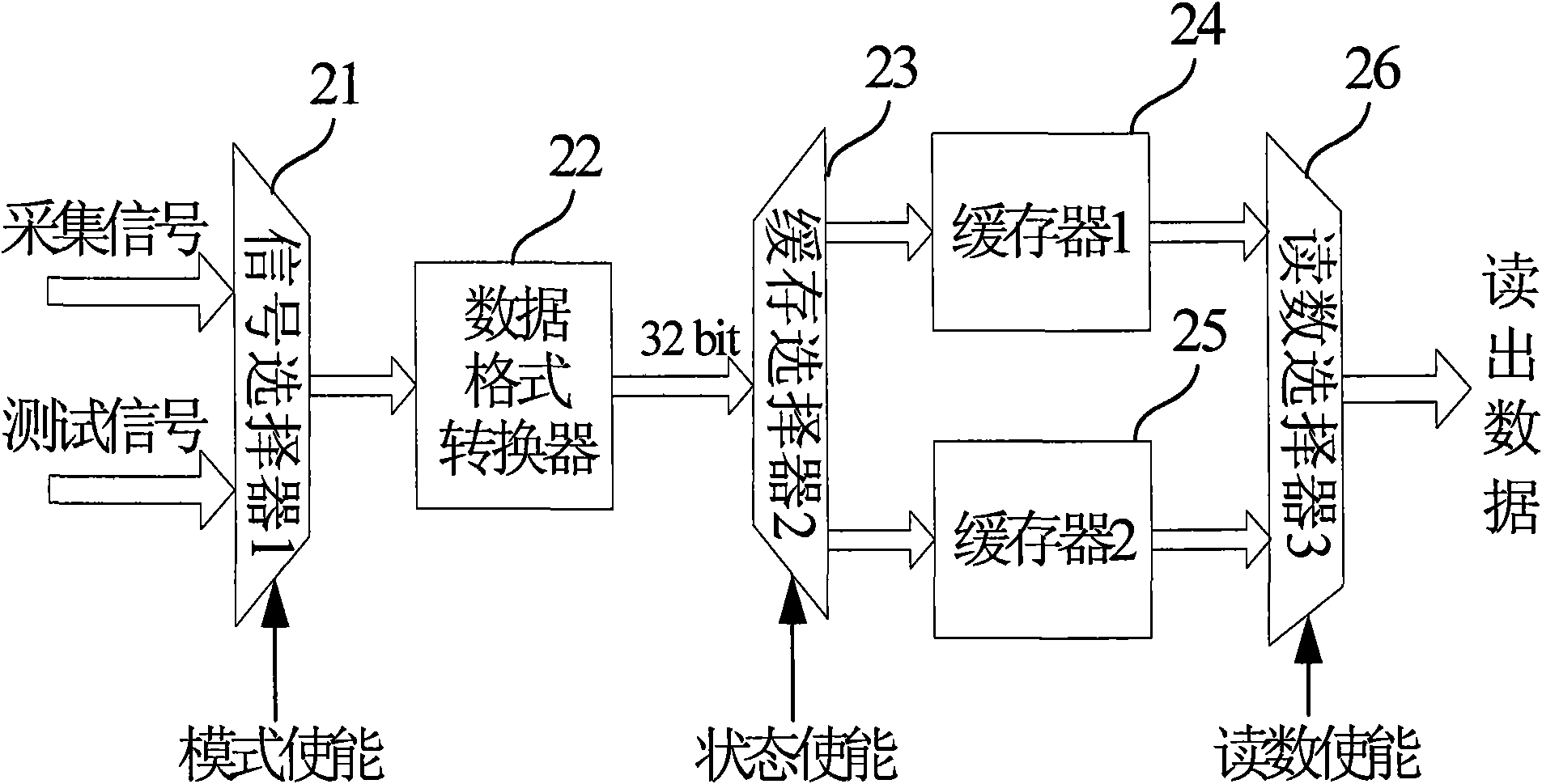

[0046] figure 2 It is a block diagram of the data acquisition and DA conversion module of the present invention. The data acquisition and DA conversion module is composed of a selector 21 , an AD converter 22 , a buffer selector 23 , buffers 24 and 25 , and a selector 26 . The selector 2...

no. 2 example

[0067] The high-speed data acquisition system of the present invention is applied to the GPS receiving system, and the intermediate frequency signal frequency of its collection is 16.368MHz, and the sampling frequency is 16.368MHz or 26MHz, and the AHB bus clock uses the clock of ARM9 internal PLL frequency multiplication, up to 200MHz. When the collected data width is 2bit, the sampling frequency can be up to 100M.

no. 3 example

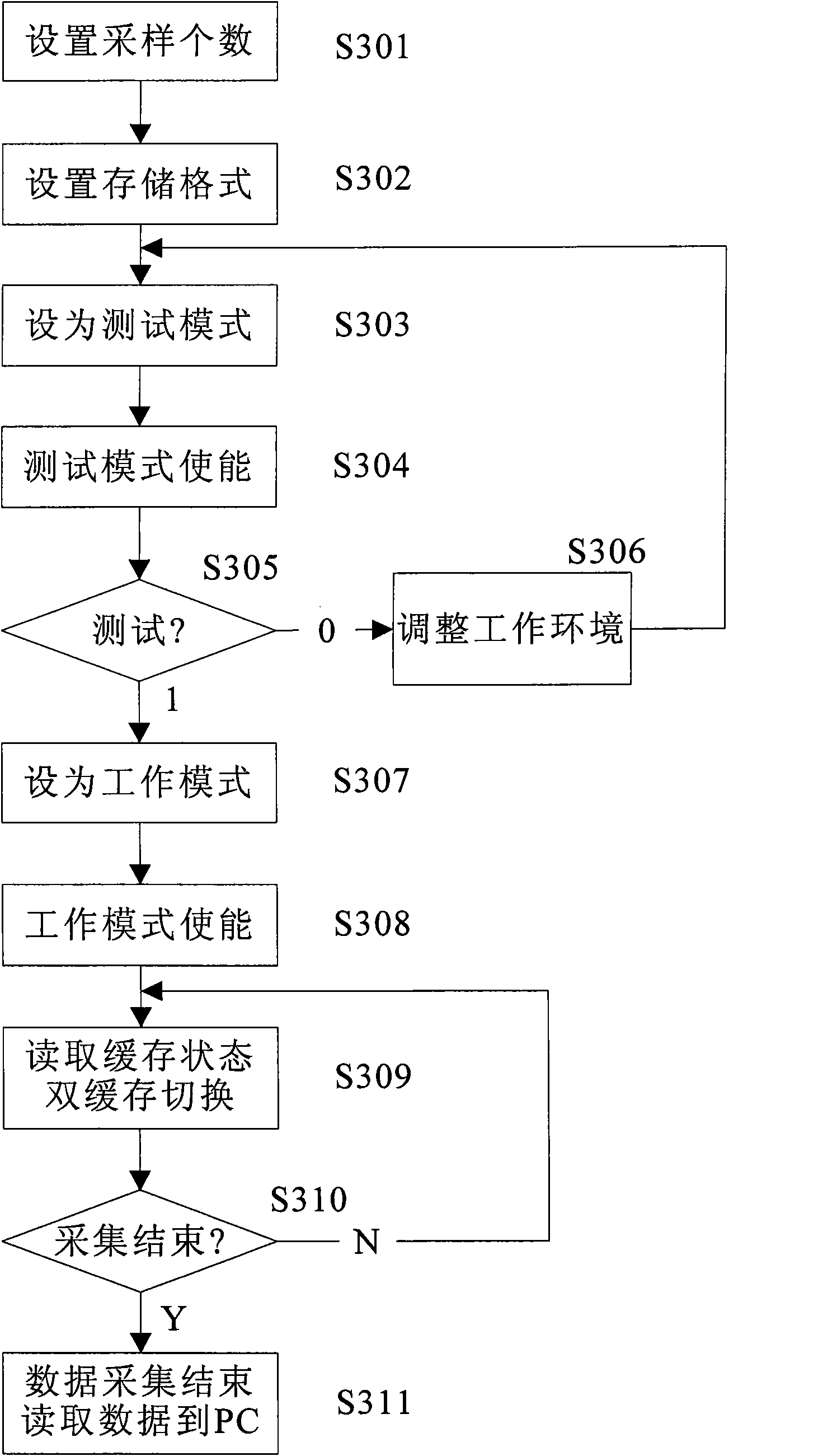

[0069] In the high-speed data acquisition system of the present invention, a self-test mode is added. When the use environment changes, the self-test mode can be used to judge whether the system is working normally. Once an abnormality occurs, the configuration can be manually adjusted to adapt to the environment. If necessary, keep the working mode of the system normal.

[0070] The self-test signal in the self-test mode is generated locally, and the self-test signal is sent to the data acquisition module, and the output fixed data is stored in SDRAM. Therefore, it is only necessary to check the data in SDRAM to detect whether the system is working normally.

[0071] In the data acquisition system of the present invention, the model selected by the FPGA chip is the EP2C70672C8 of the Cyclone II series of Altera Company; the S3C2410A of Samsung Corporation is selected by the ARM9, and the ARM920T is used as the core; the HY57V5616 of Hyundai is selected by the SDRAM chip.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More