CMOSFETs structure for controlling threshold voltage of device and manufacturing method thereof

一种阈值电压、制造方法的技术,应用在半导体/固态器件制造、半导体器件、电路等方向,达到控制阈值电压、增强界面偶极子的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

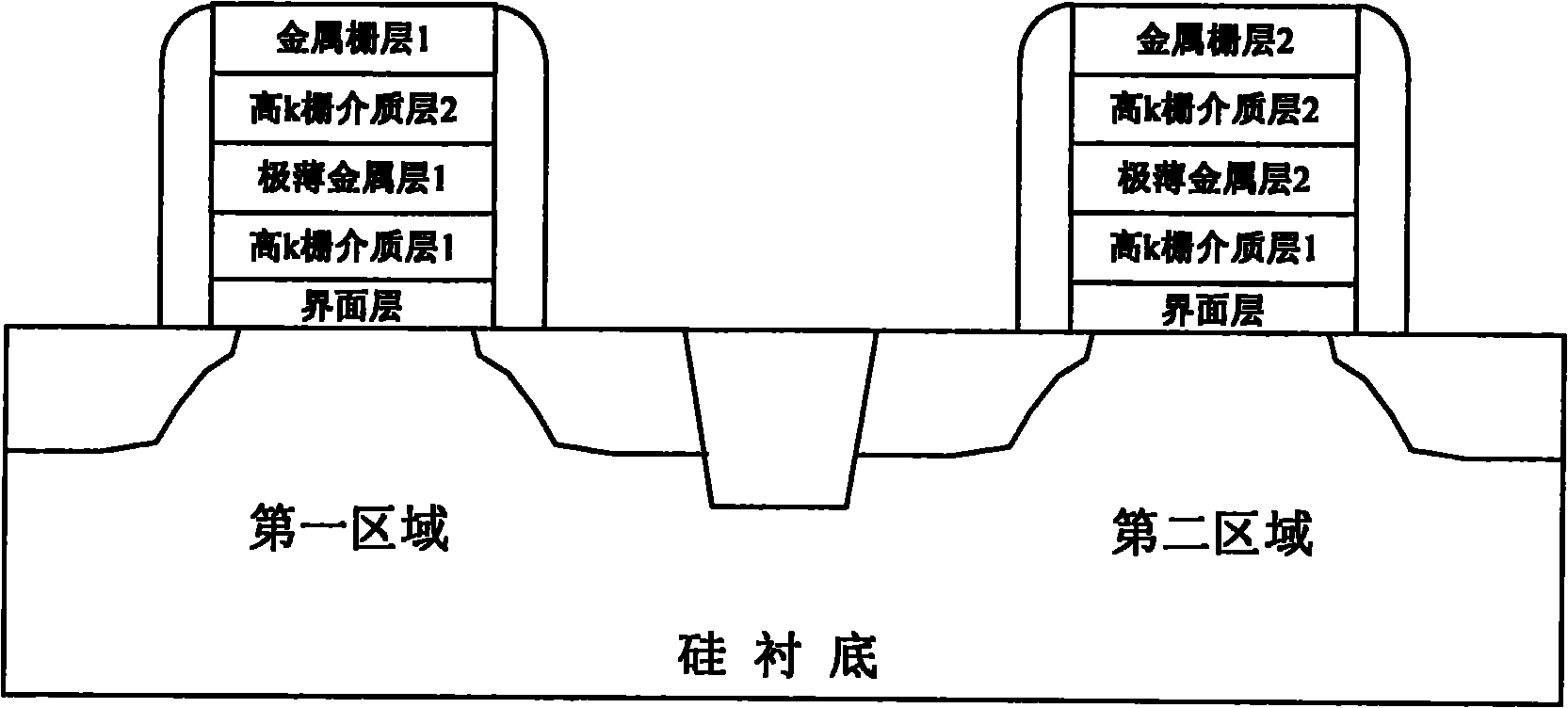

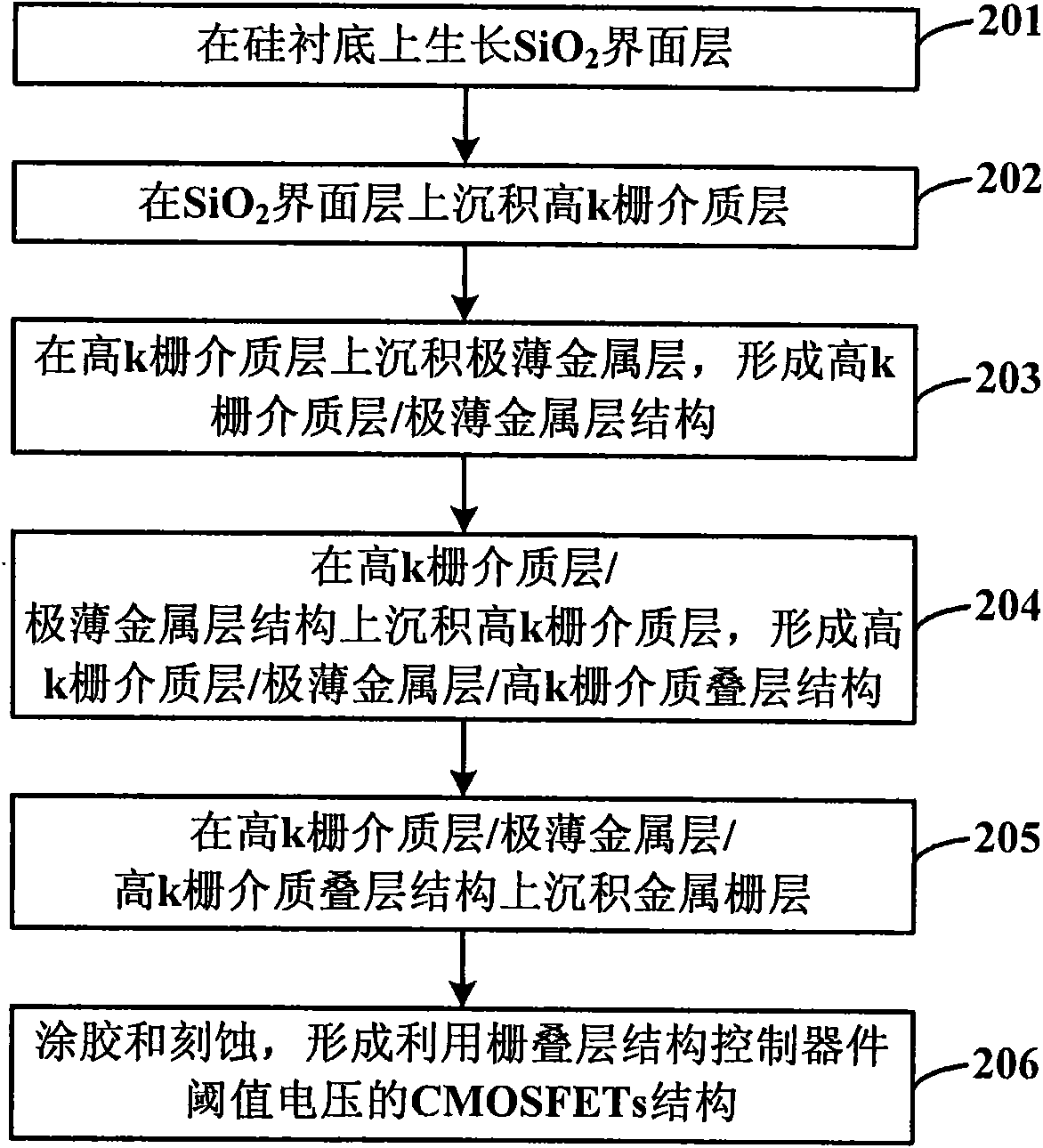

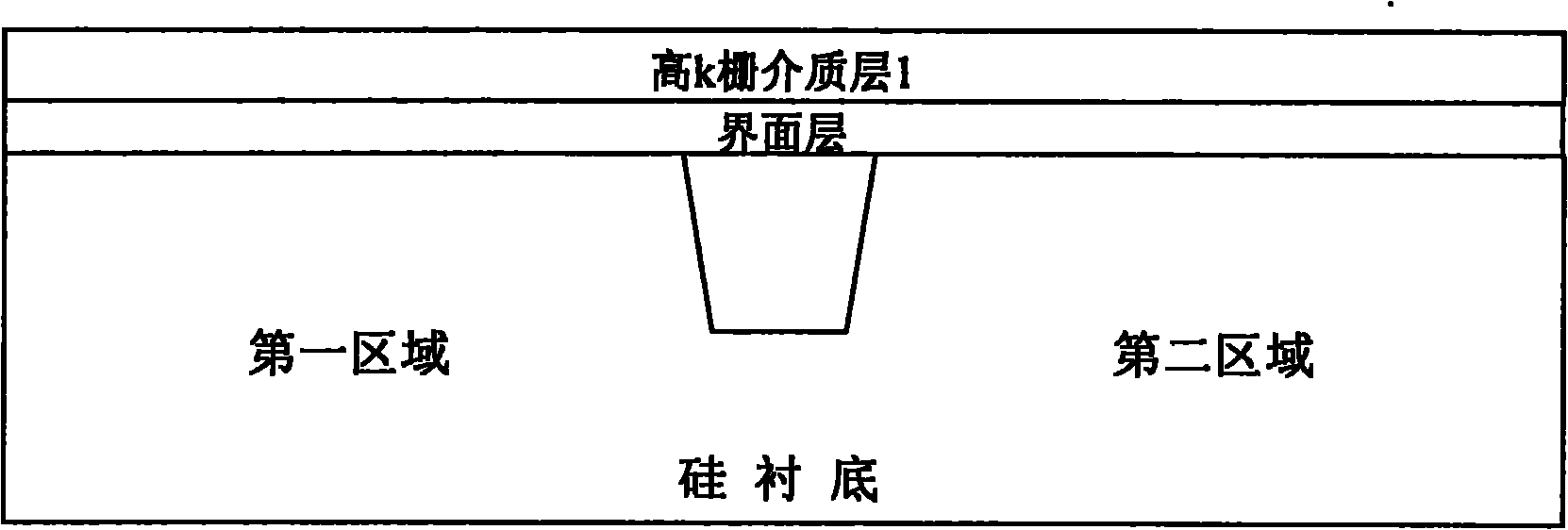

[0041] The CMOSFETs structure and its manufacturing method which utilize gate stack structure to control device threshold voltage provided by the present invention are to respectively deposit an extremely thin metal layer inside the high-k gate dielectric layer in the NMOS and PMOS device regions, and utilize the extremely thin metal layer The positive or negative charge formed inside the high-k gate dielectric layer adjusts the flat-band voltage of the device, thereby controlling the threshold voltage of the device. By adopting this process, not only the high-k gate dielectric and SiO2 in CMOS devices can be enhanced 2 The interface dipole between the interface layers can also control the type and quantity of fixed charg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More