Formation method of semiconductor structure

A technology in the direction of semiconductors and extensions, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of difficult channels and poor channel control ability of the gate structure, and achieve large removal process window, Ease of removal, effect of improving density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] It can be known from the background art that the semiconductor structure formed at present still has the problem of poor electrical performance. Now combined with a method for forming a semiconductor structure, the reasons for the poor electrical performance of the semiconductor structure are analyzed.

[0013] refer to Figure 1 to Figure 13 , a schematic diagram of the structure corresponding to each step in a method for forming a semiconductor structure is shown.

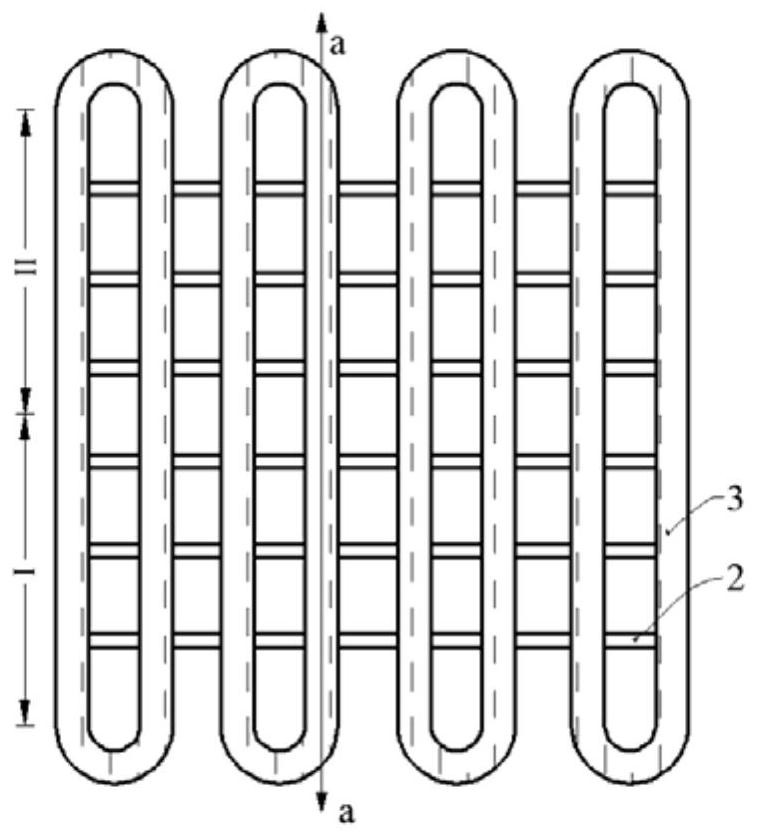

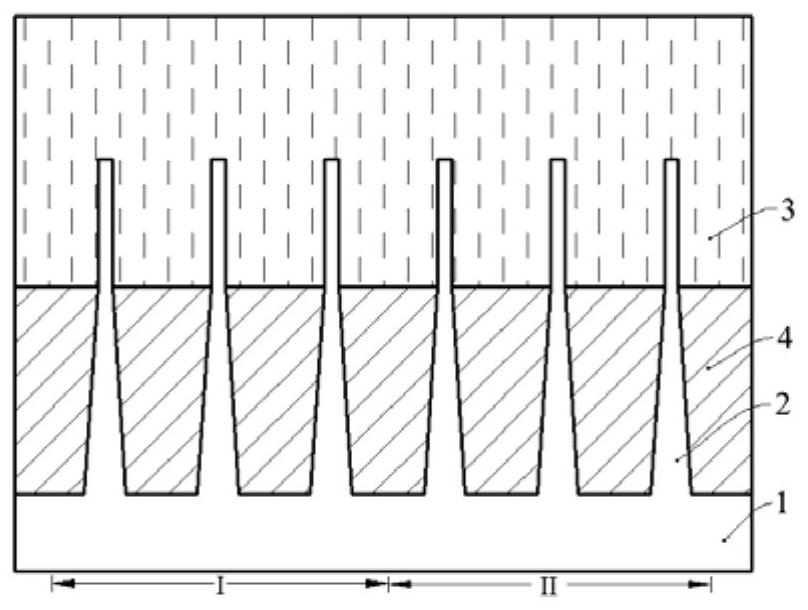

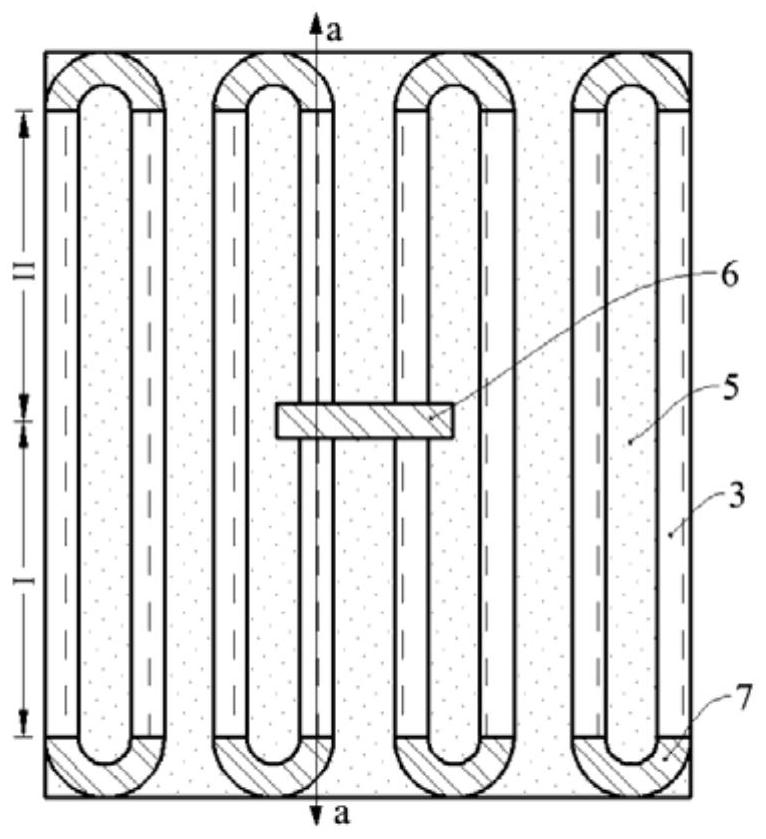

[0014] like figure 1 and figure 2 shown, figure 1 for a top view, figure 2 for figure 1 The cross-sectional view at aa, a base is provided, the base includes a substrate 1, a fin 2 separated from the substrate 1, an isolation layer 4 located on the fin 2 exposed on the substrate 1, and located on the The dummy gate structure 3 on the isolation layer 4 and across the fin portion 2 and the source and drain doped layers (not shown in the figure) in the fin portion 2 on both sides of the dummy gate s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More