Semiconductor packaging structure and manufacture process thereof

A technology of manufacturing process and packaging structure, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as substrate packaging colloid surface pollution, protective glue residue, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

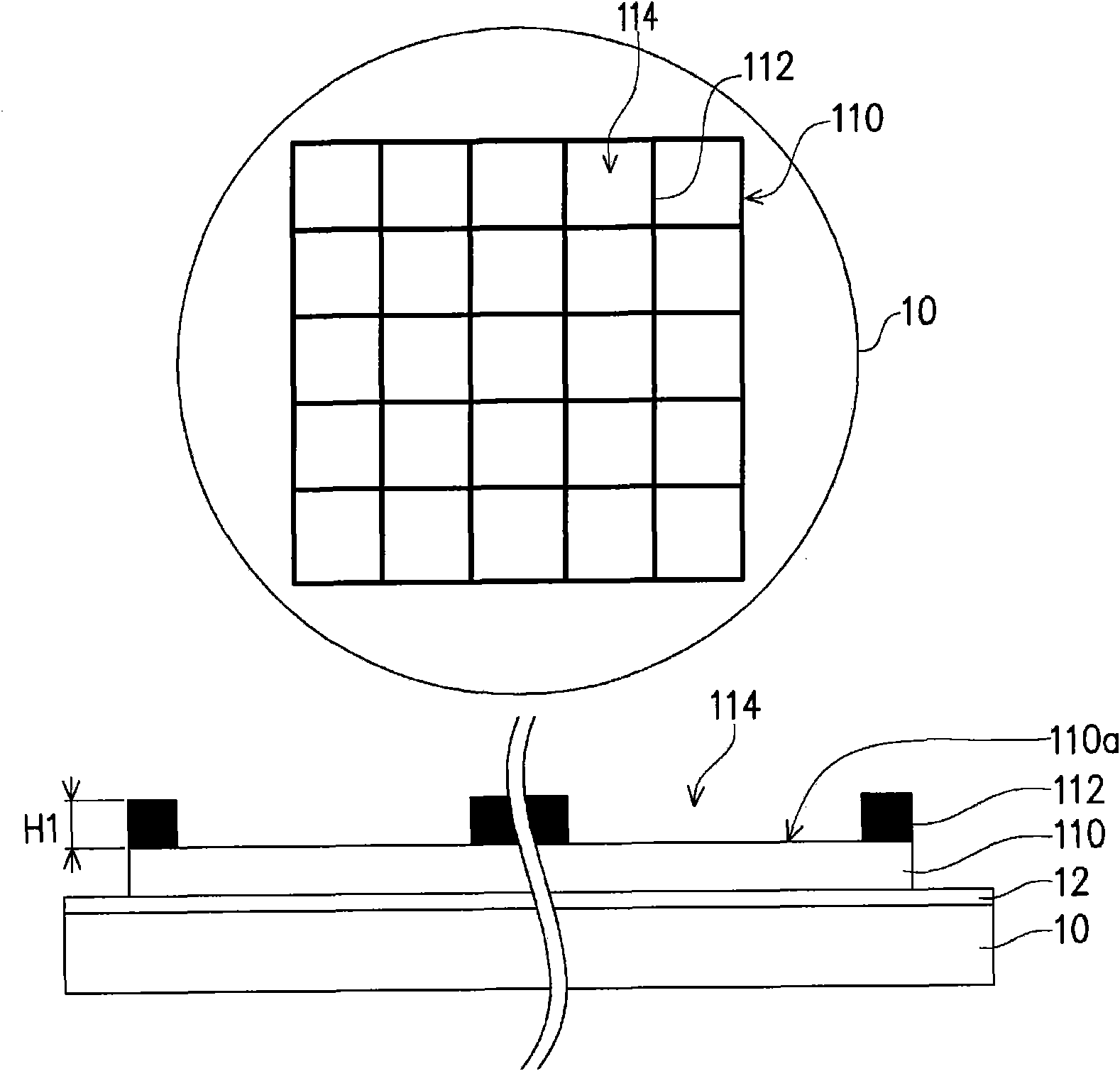

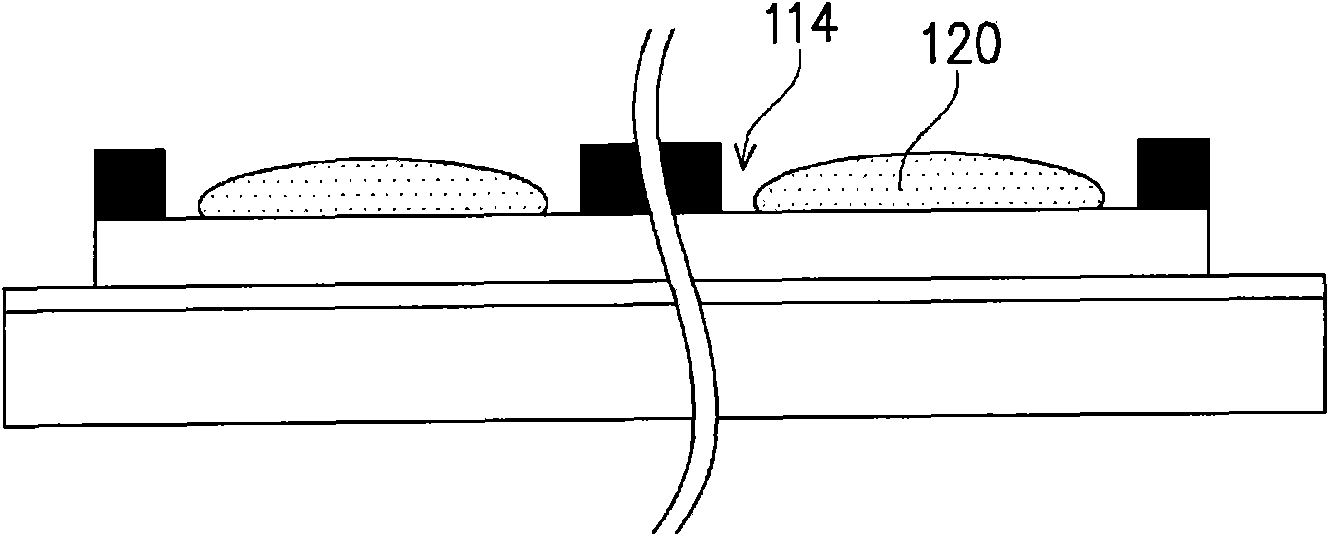

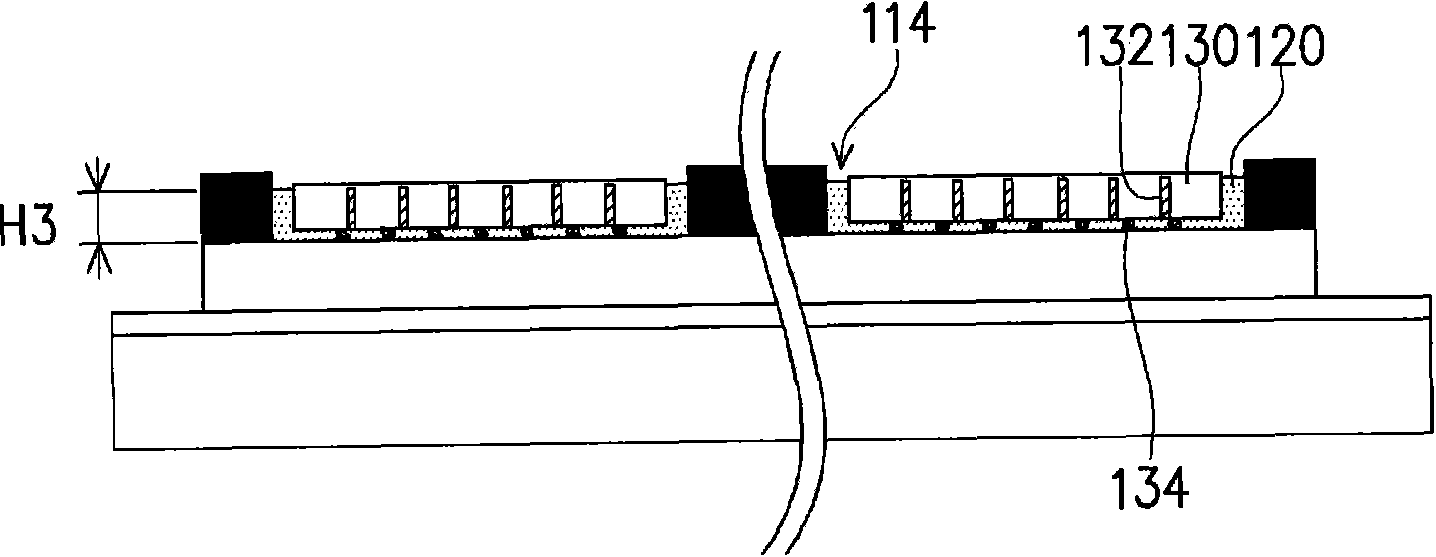

[0061] The present invention sets a grid wall with sufficient thickness on the packaging motherboard, wherein the grid wall can be integrated into the existing substrate manufacturing process, for example, the solder mask layer on the mounting surface of the packaging motherboard is thickened to form The grid wall, and the thickness of the grid wall is preferably controlled to be greater than the thickness of the thinned underlying chip. After the lower chip is bonded to the package motherboard and filled with primer, the package motherboard will be fully coated with a cladding layer to facilitate subsequent grinding steps. Since the thickness of the grid wall is greater than the thickness of the thinned lower chip, when the lower chip is ground to the end of the TSV, the cladding layer that was originally located above the grid wall and the lower chip is already in the grinding process. The middle layer is completely removed, so there will be no residual coating layer and its...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com