Array substrate and manufacturing method thereof

The technology of an array substrate and a manufacturing method, which is applied in the field of liquid crystal display testing, can solve problems such as the reduction of the signal-to-noise ratio of the test signal, the impact on the detection rate of short-circuit defects, the speed of equipment testing, and receiving interference, etc., so as to improve the signal-to-noise ratio of the detection signal, Effect of improving defect detection rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

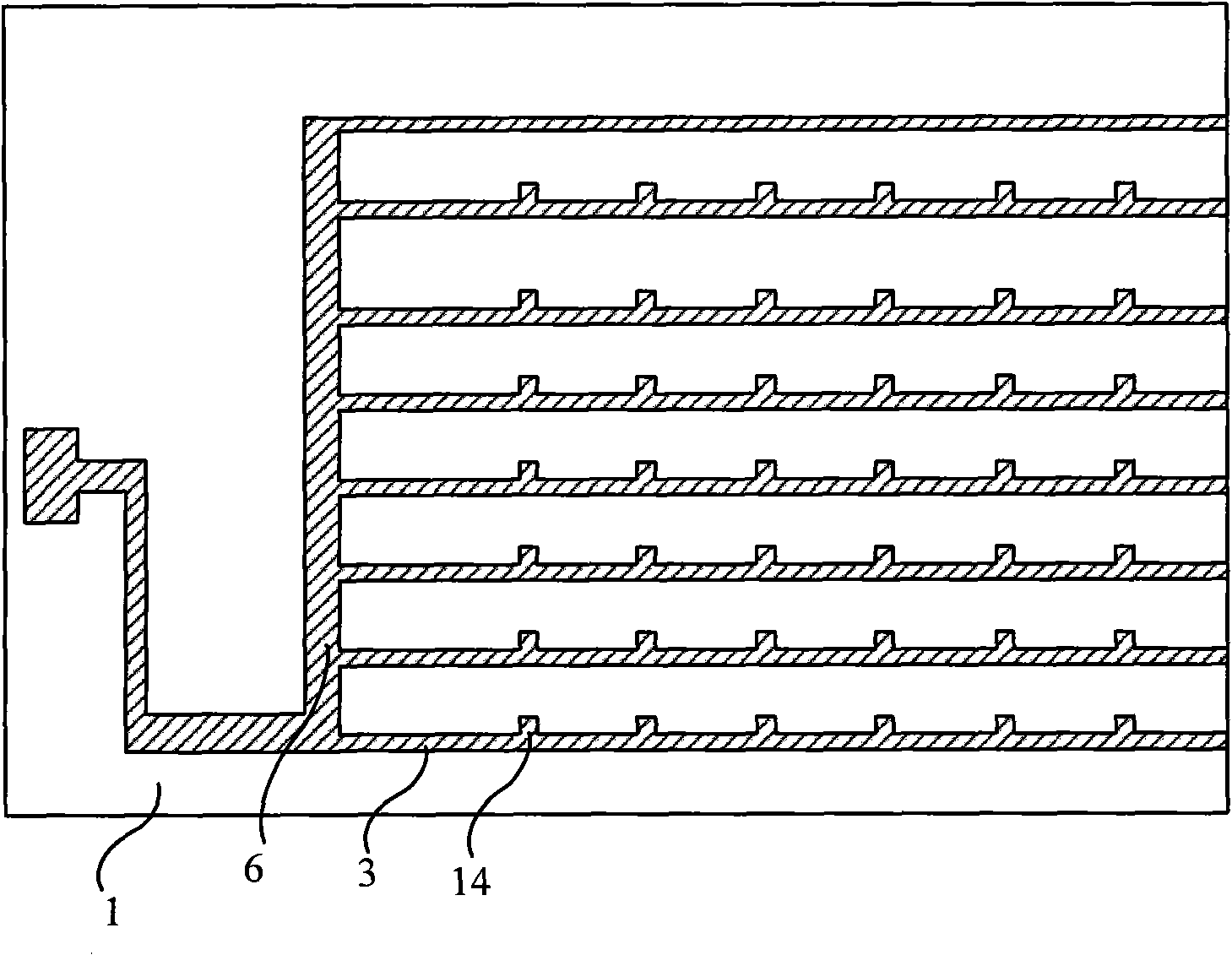

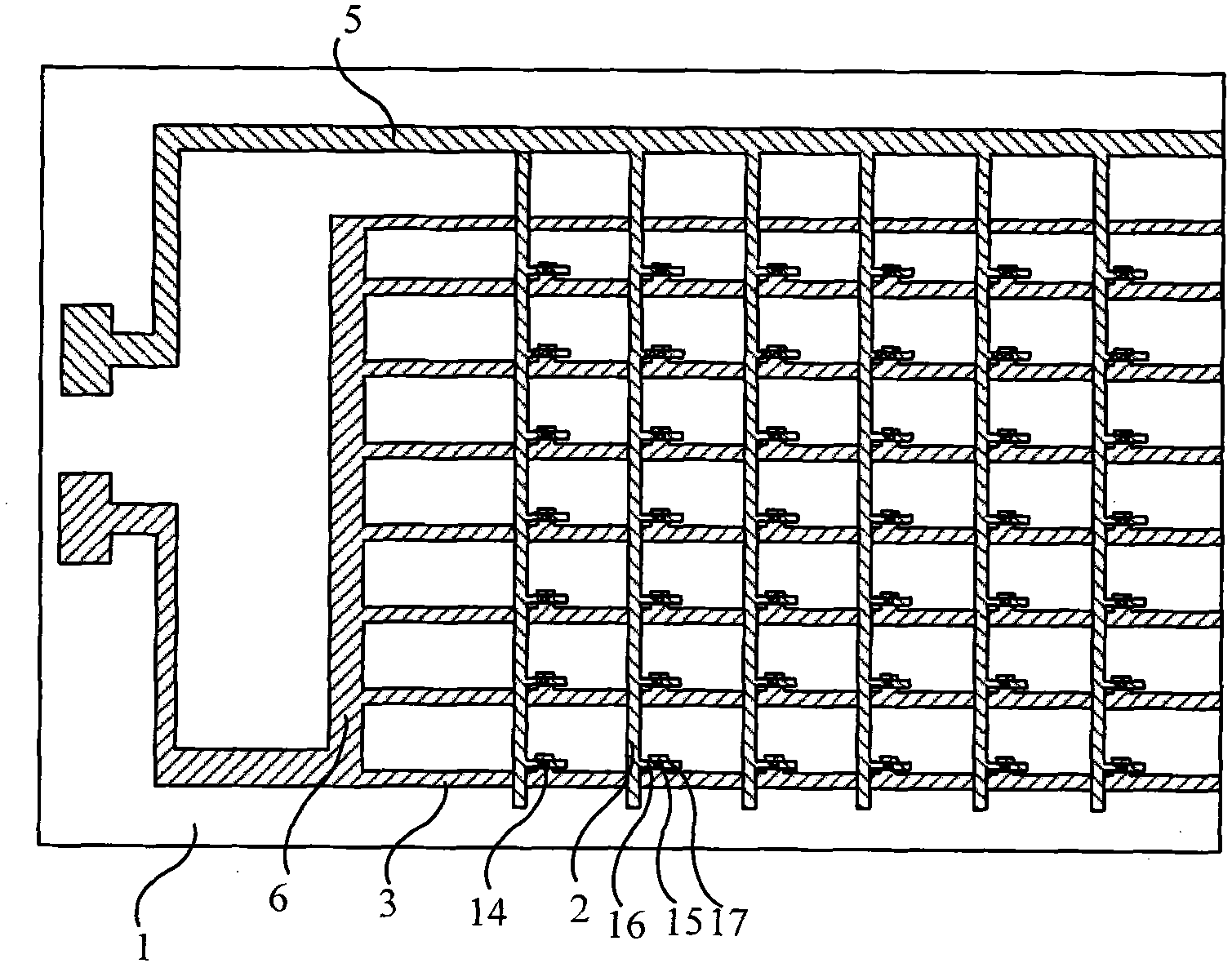

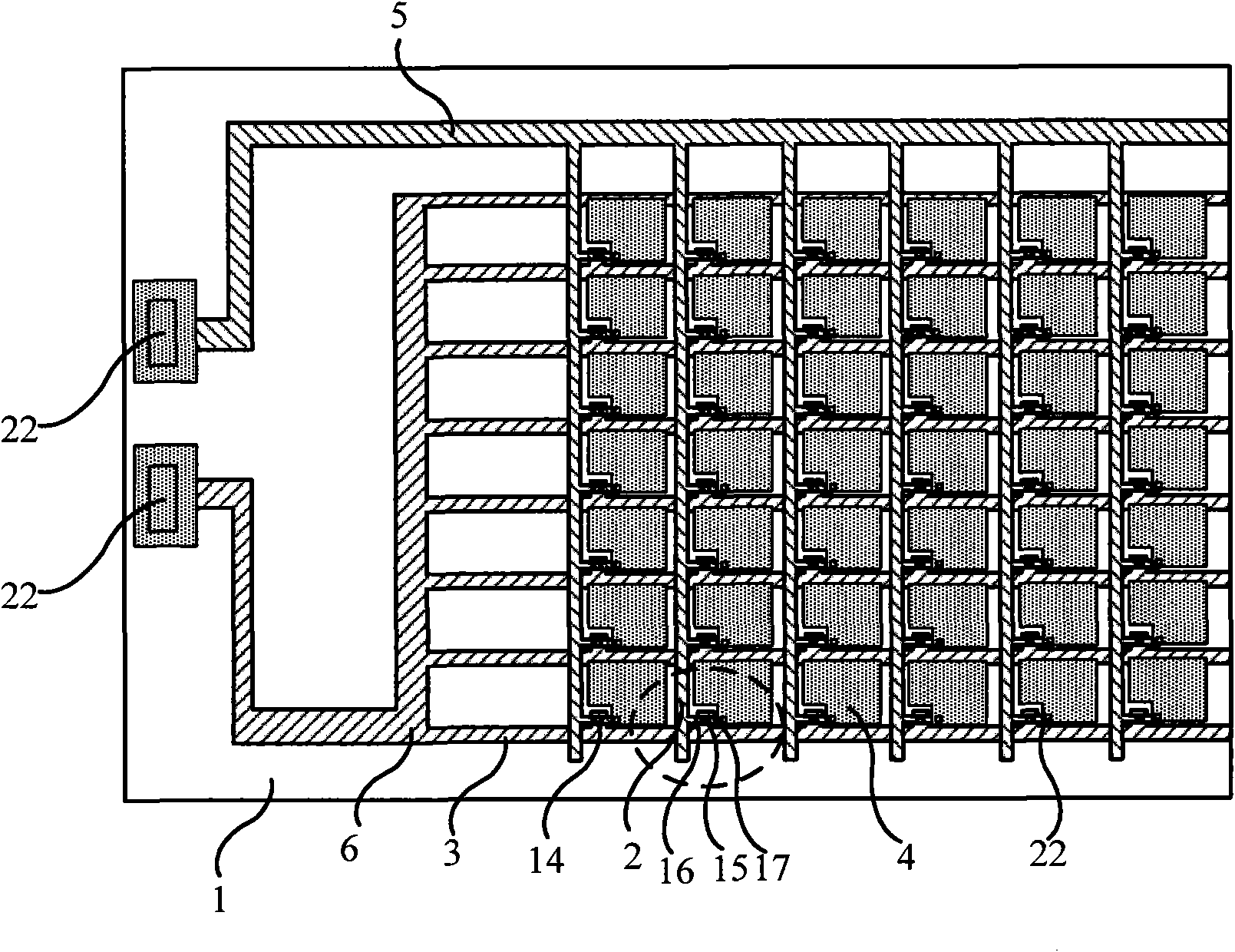

[0037] Figure 5It is a partial top view structural schematic diagram of the array substrate provided by Embodiment 1 of the present invention. The array substrate of this embodiment includes a base substrate 1 , and the base substrate 1 is mostly a glass substrate. A plurality of data lines 2 and gate scan lines 3 intersecting horizontally and vertically are formed on the base substrate 1, surrounding pixel units arranged in a matrix. A TFT switch and a pixel electrode 4 are formed in each pixel unit. In a TFT-LCD, the TFT switch in each pixel unit specifically includes a gate electrode 14 , an active layer 15 , a source electrode 16 and a drain electrode 17 . The gate electrode 14 is connected to the gate scanning line 3 , the source electrode 16 is connected to the data line 2 , and the drain electrode 17 is connected to the pixel electrode 4 . The source electrode 16 and the drain electrode 17 are stacked on the gate electrode 14 through the active layer 15 . The source...

Embodiment 2

[0050] Figure 8 It is a partial top view structural schematic diagram of the array substrate provided by Embodiment 2 of the present invention. The difference between the array substrate in this embodiment and the first embodiment is that: the data connection line 5 and the pixel electrode 4 are formed in the same layer, and are spaced apart from each other, and the data connection line 5 and each data line 2 pass through the data pass in the first insulating layer. The holes 7 are connected; the gate connection lines 6 are formed in the same layer as the pixel electrodes 4 and are spaced apart from each other, and the gate connection lines 6 and each gate scanning line 3 are connected through gate via holes 8 in the second insulating layer.

[0051] Specifically, when the data connection line 5 and the pixel electrode 4 are formed in the same layer, the first insulating layer only includes the passivation layer, and the data via hole 7 includes the second data via hole penet...

Embodiment 3

[0054] Figure 9 The partial top view structure schematic diagram of the array substrate provided by the third embodiment of the present invention, the difference between this embodiment and the first embodiment is that the data connection line 5 and the data line 2 are formed on the same layer, and are spaced apart from each other, as shown in Figure 11 Shown is the pattern of the layer where the data line 2 and the data connection line 5 are located. Such as Figure 9 As shown, the data connection line 5 is connected to each data line 2 through the data via hole 7 in the first insulating layer. Such as Figure 10 Shown is the pattern of the layer where the gate scanning line 3 and the gate connecting line 6 are located. The gate connecting line 6 and the gate scanning line 3 are formed in the same layer and are spaced apart from each other. Such as Figure 9 As shown, the gate connecting line 6 is connected to each gate scanning line 3 through the gate via hole 8 in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More