ESD protection device in CMOS integrated circuit

An ESD protection and integrated circuit technology, which is applied in circuit devices, emergency protection circuit devices, emergency protection circuit devices for limiting overcurrent/overvoltage, etc., can solve problems such as weakening of ESD protection capability and reduction of parasitic resistance of devices

Inactive Publication Date: 2011-03-30

李佳音

View PDF0 Cites 0 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

The dielectric strength of silicon dioxide is approximately 8×106V / cm, so the breakdown voltage of a gate oxide with a thickness of 10nm is about 8V. Although the breakdown voltage is more than double the power supply voltage of 3.3V, various Static electricity caused by various factors generally has a peak voltage far exceeding 8V; The resistance is reduced, and the ESD protection ability is greatly weakened

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment Construction

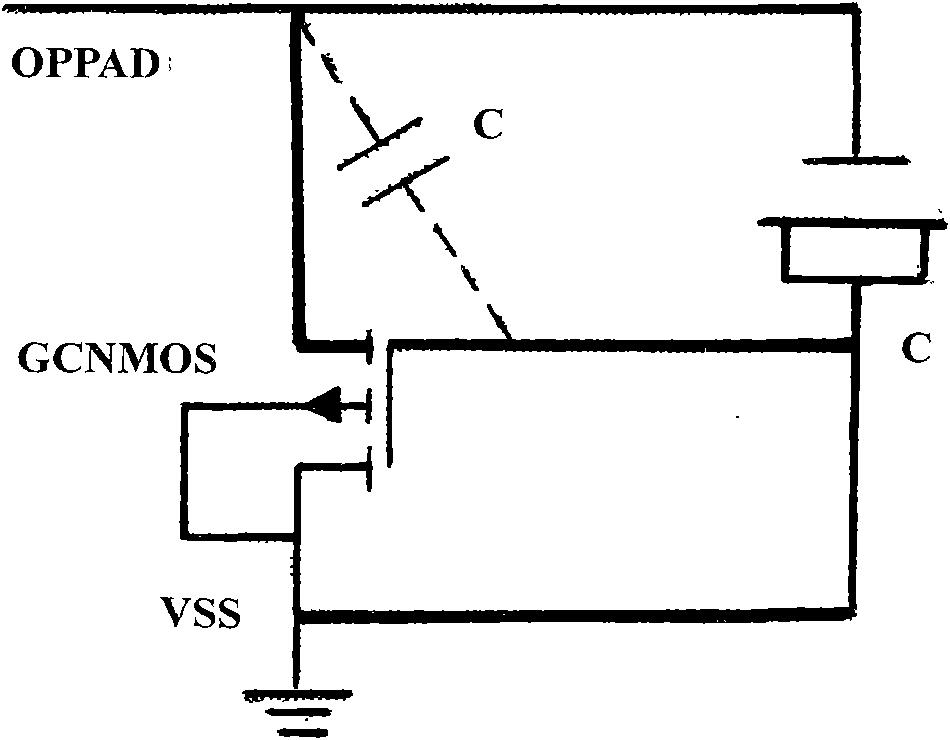

[0008] The gate of the present invention needs to be grounded through resistance Rg, so that GCNMOS is closed when CMOSIC is working, and -NMOS is connected into capacitive Cc in addition to strengthen the capacitive coupling effect; when there is positive ESD voltage to occur on the input PAD, a part The positive voltage of the positive voltage will be coupled to the gate of GCNMOs through Cd and Cc, and the gate voltage will be discharged to the ground through Rg. The size of Rg will affect the holding time of the gate voltage. GCNMOS conducts uniformly to improve its ESD protection. ability.

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

The invention discloses an electronic static discharge (ESD) protection device in a complementary metal oxide semiconductor (CMOS) integrated circuit, belongs to the field of analog circuits, and relates to an ESD protection system in the CMOS integrated circuit. The invention aims to provide the novel ESD protection system in the CMOS integrated circuit. A grid is grounded through a resistor Rg so that a grid coupling negative-channel metal oxide semiconductor (GCNMOS) is shut down when a complementary metal oxide semiconductor integrated circuit (CMOSIC) works, and the other negative-channel metal oxide semiconductor (NMOS) is connected as a capacitive Cc to reinforce the capacitive coupling effect; and when a positive ESD voltage occurs on an input PAD, a part of positive voltage is coupled to the grid of the GCNMOS through the Cd and the Cc, the grid voltage is discharged to the ground through the Rg, the size of the Rg affects the holding time of the grid voltage, and the GCNMOS is uniformly conducted so as to promote the ESD protection capability.

Description

Technical field: [0001] The invention belongs to the field of analog circuits, and relates to an ESD protection system in a CMOS integrated circuit. Background technique: [0002] Static electricity is ubiquitous in the process of chip manufacturing, packaging, testing and use. The accumulated static charge is released in nanoseconds to microseconds with a current of several amperes or tens of amperes. The instantaneous power is as high as hundreds of kilowatts, and the discharge energy It can reach millijoules, and the destruction intensity of the chip is extremely high. Therefore, the design of the electrostatic protection module in chip design is directly related to the functional stability of the chip, which is extremely important. With the development of the process, the feature size of the device is gradually reduced, and the gate oxide is also proportionally reduced. The dielectric strength of silicon dioxide is approximately 8×106V / cm, so the breakdown voltage of a...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): H02H9/04

Inventor 李佳音

Owner 李佳音