TFT (Thin Film Transistor) array structure and manufacturing method thereof

A technology of an array structure and a manufacturing method, applied in the field of TFT array structure and its manufacturing, can solve the problems of poor capacitor storage capacity and small storage capacitor capacitance value, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

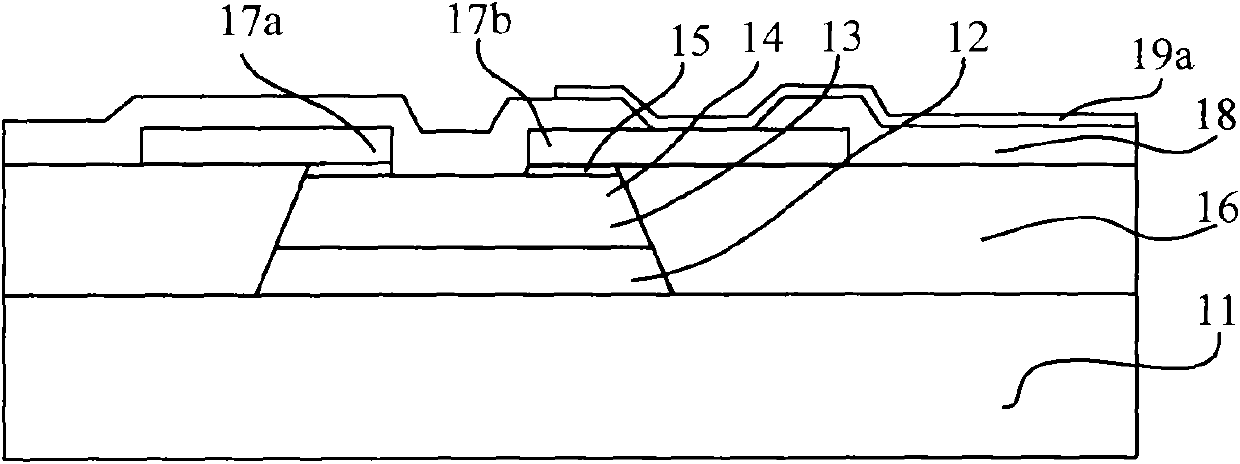

[0099] In one embodiment of the present invention, a kind of manufacturing method of TFT array structure is provided, such as Image 6 shown, including steps:

[0100] S101, providing a substrate, the substrate has a first region and a second region;

[0101] S102, sequentially forming a gate electrode metal layer, a gate electrode insulating layer, a semiconductor layer and an ohmic contact layer on the substrate;

[0102] S103, using a mask plate to define a photoresist pattern;

[0103] S104, using the photoresist pattern as a mask, removing the ohmic contact layer, semiconductor layer, gate electrode insulating layer, and gate electrode metal layer on areas other than the first area and the second area, and exposing the the substrate;

[0104] S105, forming a first insulating layer on a region of the substrate other than the first region and the second region;

[0105] S106, forming a source-drain electrode metal layer on the first insulating layer and the ohmic contac...

no. 2 example

[0165] In one embodiment of the present invention, a kind of manufacturing method of TFT array structure is provided, such as Figure 21 shown, including steps:

[0166] S201, providing a substrate, the substrate has a first region and a second region;

[0167] S202, sequentially forming a gate electrode metal layer, a gate electrode insulating layer, a semiconductor layer and an ohmic contact layer on the substrate;

[0168] S203, using a half-gray mask to define a photoresist pattern;

[0169] S204, using the photoresist pattern as a mask, removing part of the ohmic contact layer, semiconductor layer, gate electrode insulating layer, and gate electrode metal layer; leaving the ohmic contact layer, semiconductor layer, and gate electrode on the first region an insulating layer and a gate electrode metal layer; leaving the gate electrode insulating layer and the gate electrode metal layer on the second region;

[0170] S205, forming a first insulating layer on the periphery...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More