Non-CMP preparation technology applicable to back grid technology

A technology of preparation process and gate-last process, which is applied in the field of planarization preparation process suitable for gate-last process without CMP, can solve the problems of difficult control, high cost of CMP planarization process, expensive equipment, etc., and achieve the effect of low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

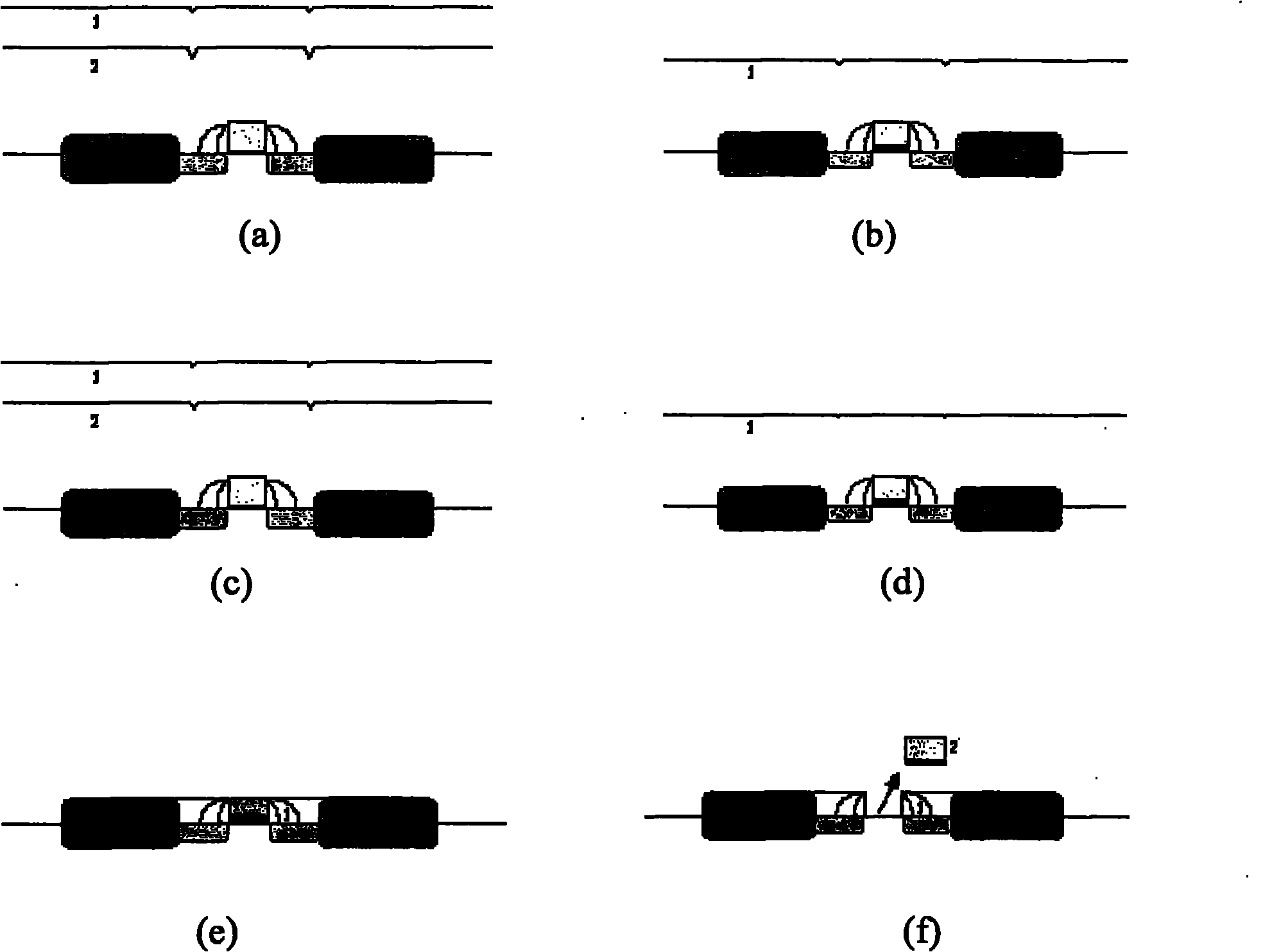

[0024] see figure 1 , the planarization process flow of the present invention is as follows:

[0025] It should be noted that figure 1 middle:

[0026] (a) Spin-coating primary photoresist: 1 is primary photoresist; 2 is dielectric (LTO+Si 3 N 4 );

[0027] (b) After one photoresist back-etching, photoresist / LTO rate difference back-etching and deglue: 1 is the remaining medium (LTO+Si 3 N 4 );

[0028] (c) Spin-coating secondary photoresist: 1 is the secondary photoresist, 2 is the remaining medium (LTO+Si 3 N 4 );

[0029] (d) After two times of photoresist back etching, photoresist / LTO equal speed back etching and deglue: 1 is the remaining medium (LTO+Si 3 N 4 );

[0030] (e) Etch LTO to expose the dummy gate: 1 is the remaining dielectric (LTO+Si 3 N 4 );

[0031] (f) Remove the dummy gate: 1 is the remaining dielectric (LTO+Si 3 N 4 ), 2 is a false gate.

[0032] The above process flow is the main steps of the present invention, on the basis of which, t...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap