Groove metal-oxide semiconductor field effect transistor and manufacture method thereof

An oxide semiconductor and field effect transistor technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as large leakage current, achieve high breakdown voltage, low gate leakage charge, and save production costs. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0068] The present invention will be described in detail below with reference to the drawings, in which preferred embodiments of the present invention are shown. The present invention can, but be embodied in different ways, but should not be limited to the embodiments described herein. For example, the description here refers more to N-channel trench MOSFETs, but it is obvious that other devices are also possible.

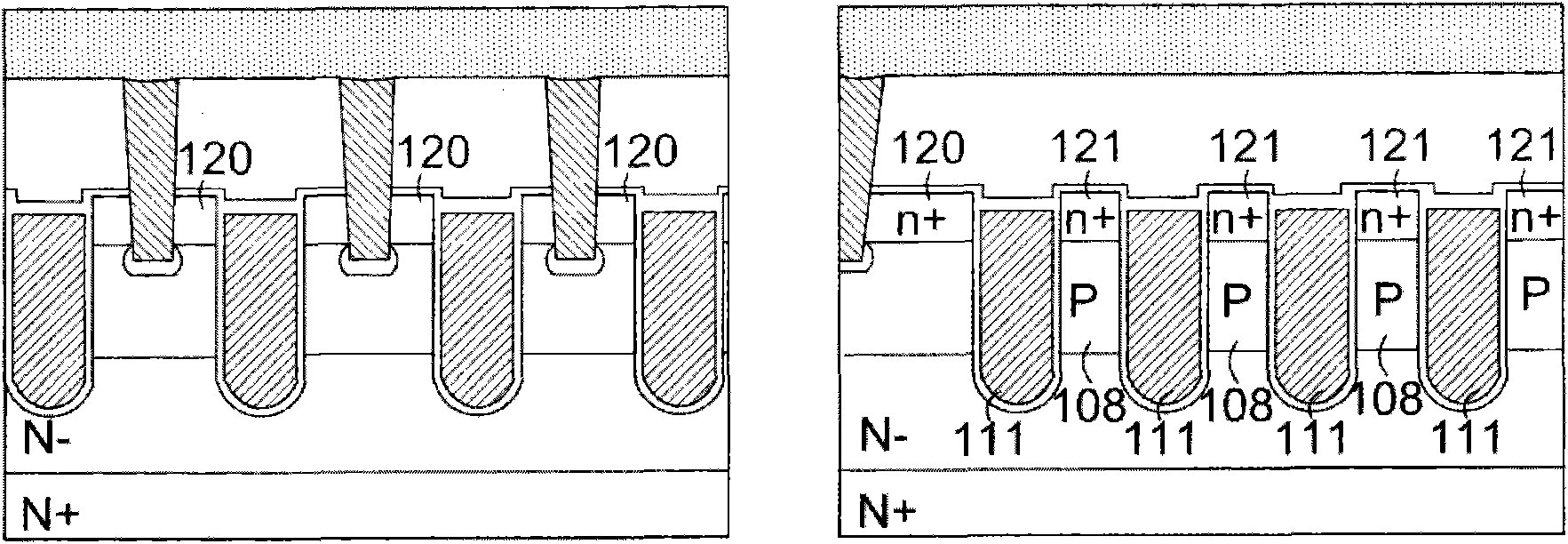

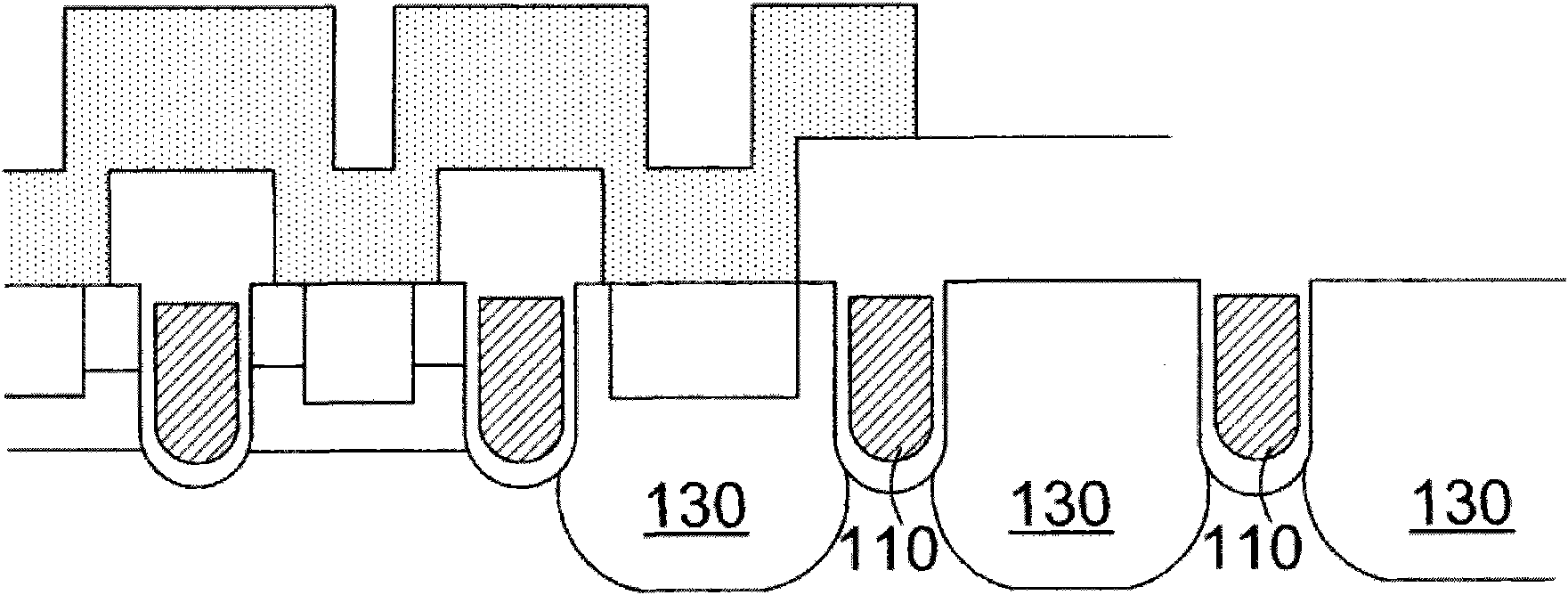

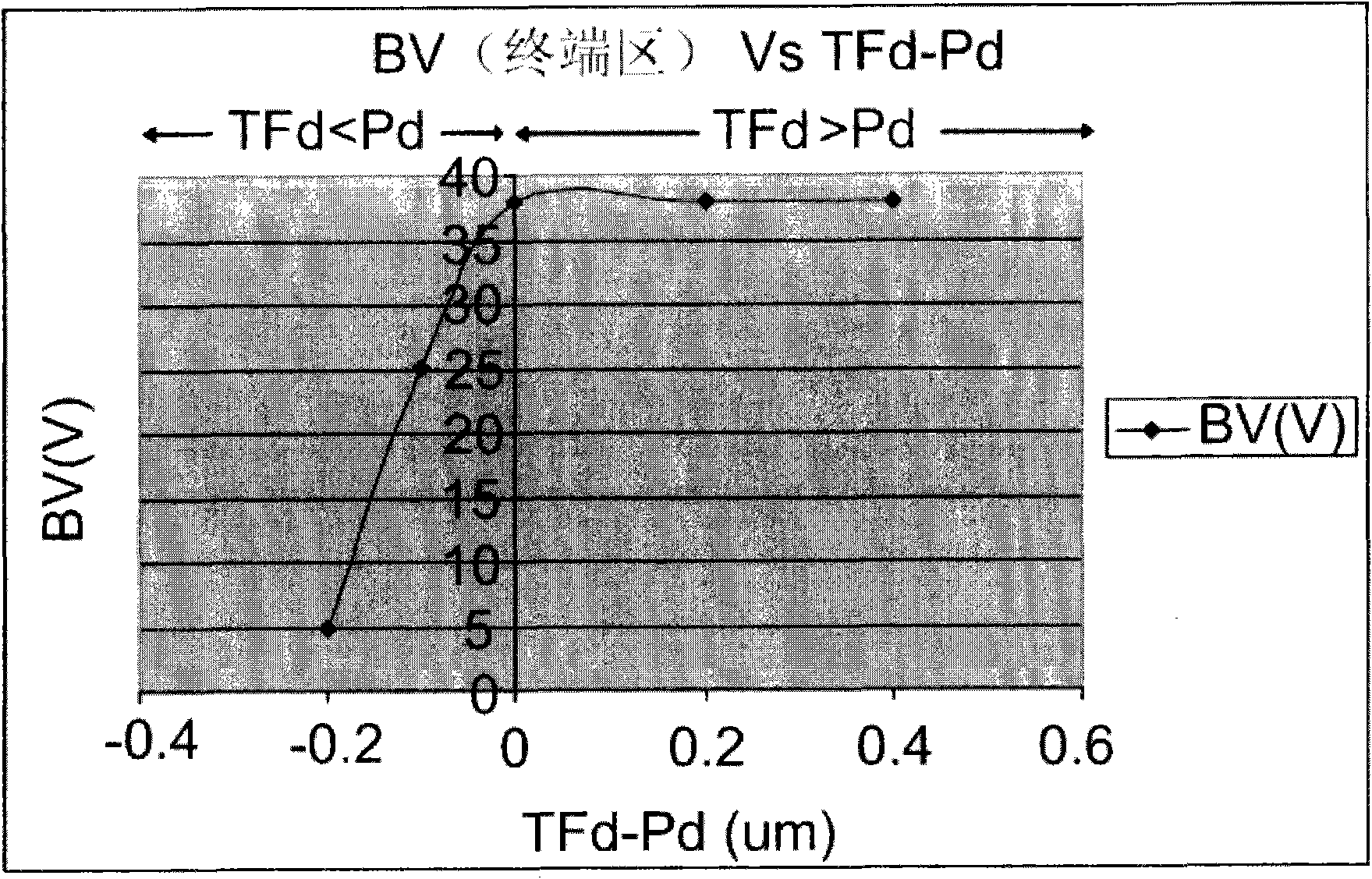

[0069] Reference image 3 As shown in a preferred embodiment of the present invention, the N-type epitaxial layer 202 is formed on the N+ substrate 200, and a drain metal 290 is deposited on the lower surface of the N+ substrate 200. In the N-type epitaxial layer 202, there are a plurality of first trench gates 210 located in the active area, at least one wider second trench gate 212 for gate connection, and at least three second trench gates located in the terminal area. Three trench gate 211. The inner surfaces of the first trench gate 210, the second trench gate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More