Forming method of dual damascene structure

A technology of dry etching and silicon oxide, which is applied in the fields of electrical components, semiconductor/solid-state device manufacturing, circuits, etc. It can solve the problems of inability to control the depth of trench etching, affecting the depth of trenches, and affecting the depth of through holes, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0059] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0060] figure 2 For the flow chart of the formation method of a kind of double damascene structure provided by the present invention, as figure 2 As shown, the method includes:

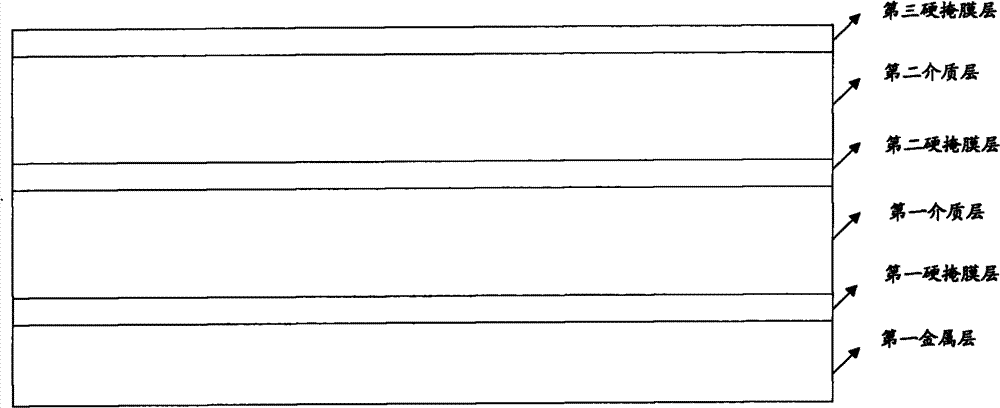

[0061] In step 201, a first hard mask layer and a first dielectric layer are sequentially deposited on the metal layer, and the first dielectric layer is etched to form via holes.

[0062] Step 202 , coating a bottom anti-reflective coating (BARC) and filling the via hole.

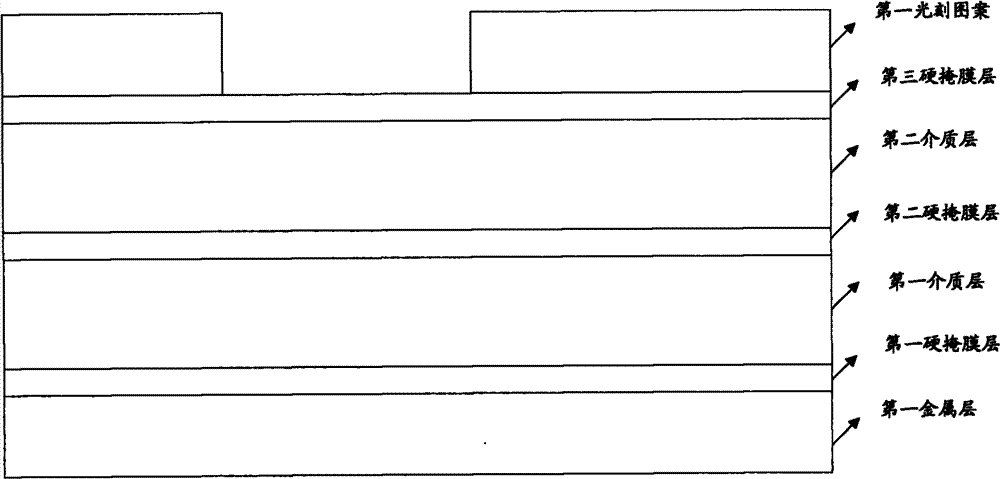

[0063] Step 203 , coating the first PR, exposing and developing the first PR to form a first photoresist pattern, wherein the width of the first PR in the first photoresist pattern is equal to the opening width of the trench.

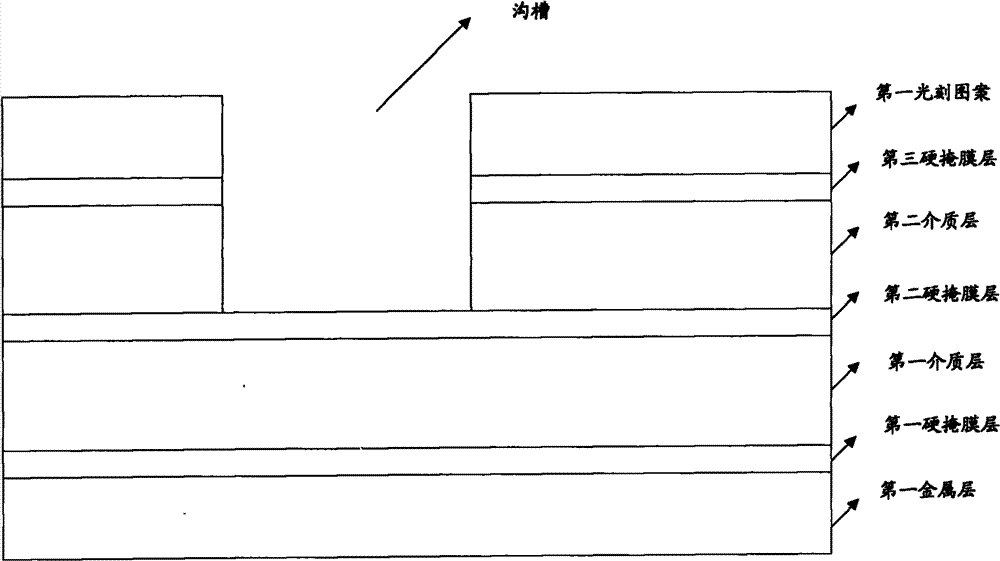

[0064] Step 204, deposit low-temperature chemical vapor deposition (CVD) si...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More