BSIM4 stress model applied to MOSFET electrical simulation

A stress model and simulation technology, applied in special data processing applications, electrical digital data processing, instruments, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The present invention will be further elaborated below in conjunction with the accompanying drawings and examples. The following examples do not limit the invention. Without departing from the spirit and scope of the inventive concept, changes and advantages that can be imagined by those skilled in the art are all included in the present invention.

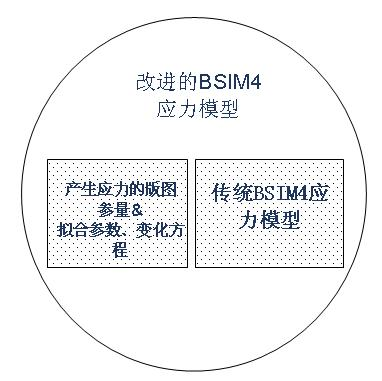

[0047] The present invention provides a BSIM4 stress model applied to MOSFET electrical simulation, which is a layout-related BSIM4 stress model of 22nm-130nm standard process MOSFET, which has clear physical meaning and high accuracy, and can be used for different layouts under certain bias conditions Parametric MOSFET electrical characteristics are simulated.

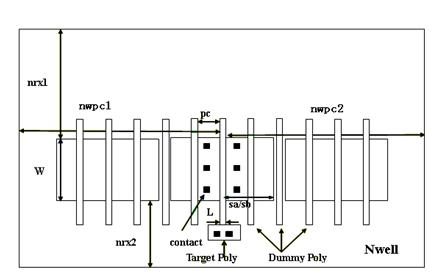

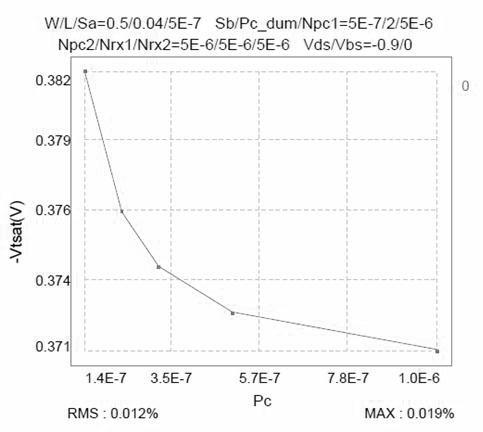

[0048] The following will further describe in detail how to apply the layout-related BSIM4 stress model of the 40nm standard process MOSFET of the present invention with examples.

[0049] Based on the standard BSIM4 model, the present invention introduces the st...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More