Manufacturing methods for dual damascene process and integrated circuit

A manufacturing method and process technology, applied in the field of integrated circuit manufacturing using the double damascene process manufacturing method, can solve the problem of oblique facets that cannot completely solve the thickness difference, cannot protect the top of both sides of the through hole, and reduce the thickness of the filling material and other problems, to achieve the effect of subtracting the spin-coating filling material and etching back process steps, improving the shape of the beveled facet, and improving the stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

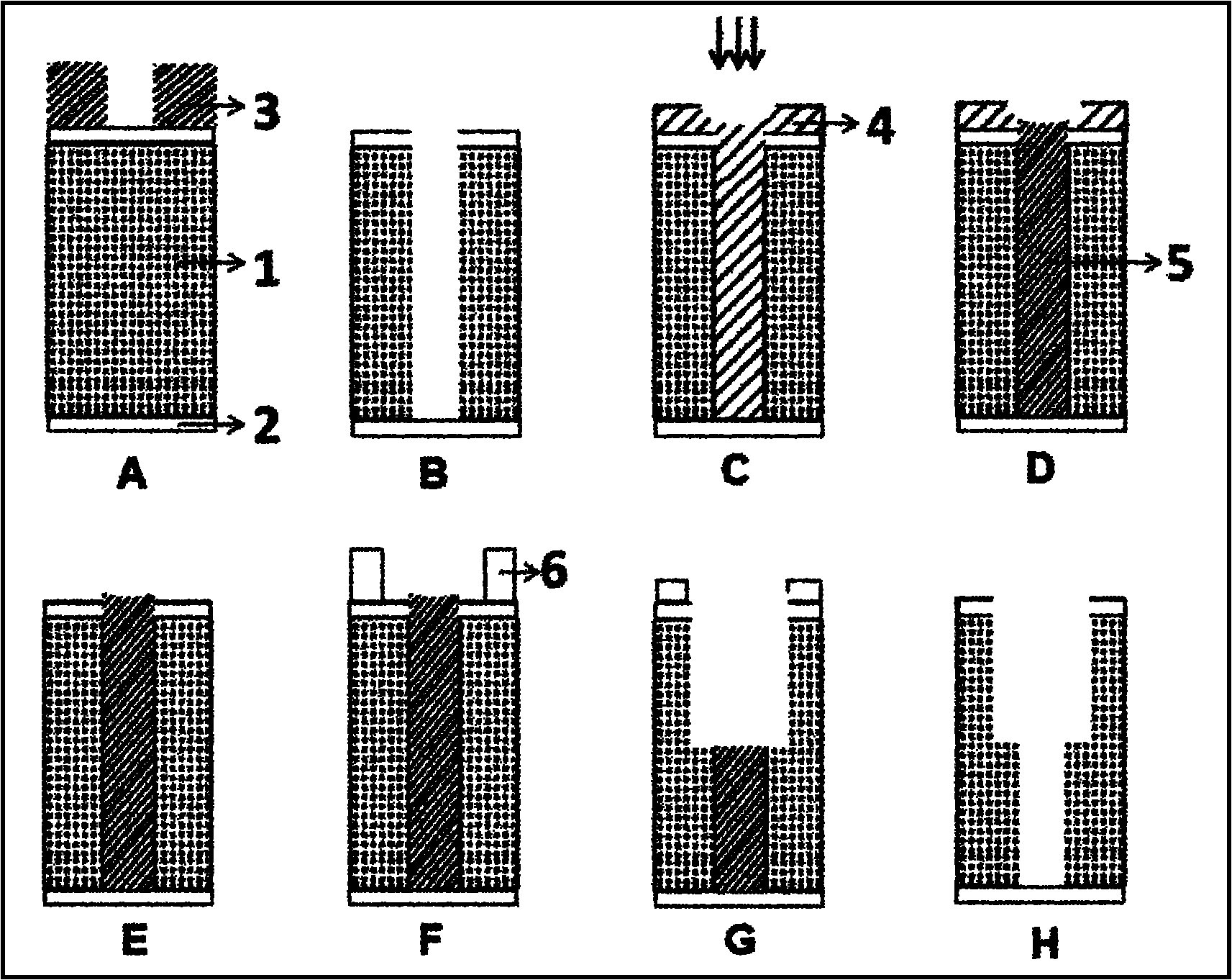

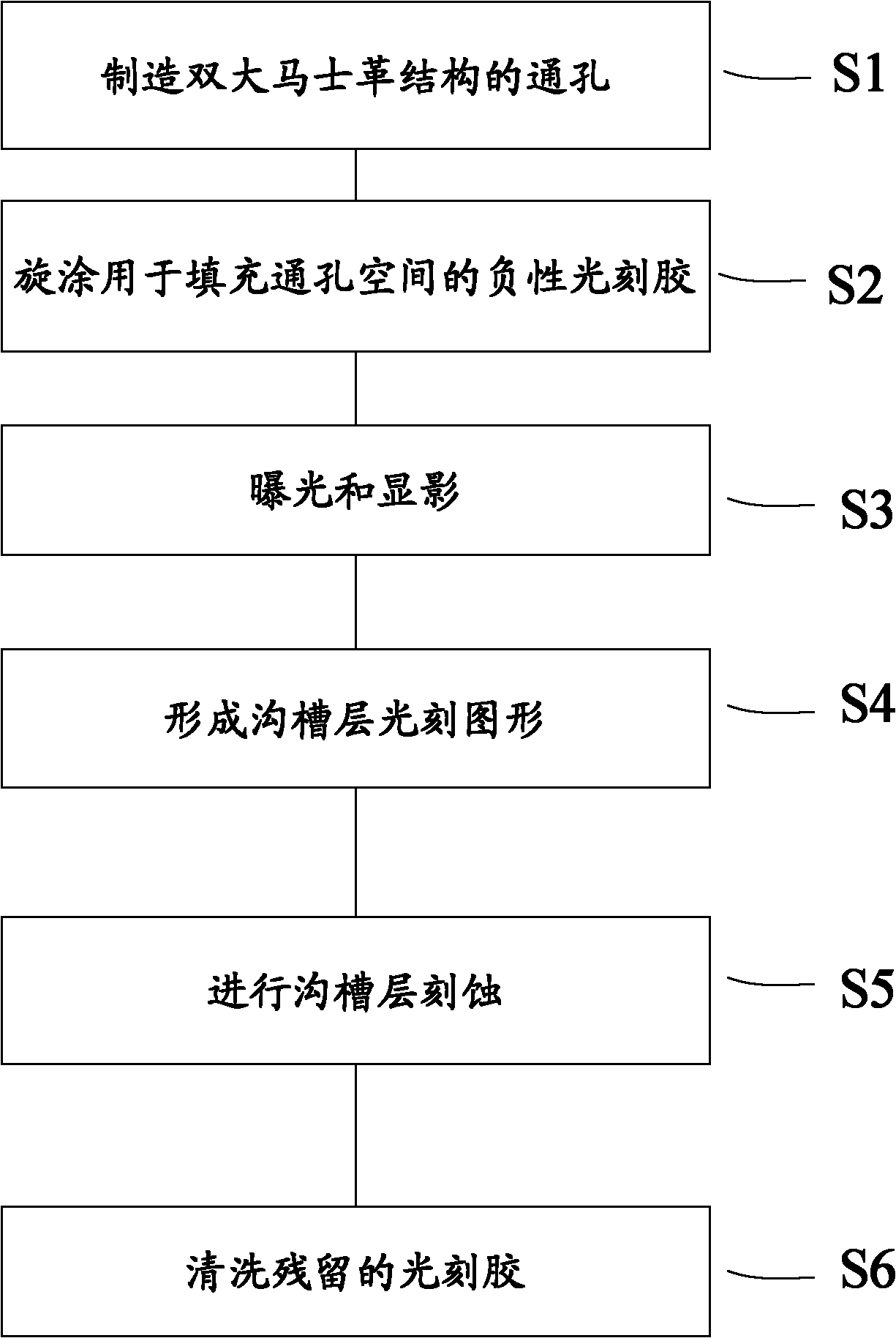

[0030] figure 2 is a schematic illustration of an embodiment of the invention; and image 3 It is a flowchart of an embodiment of the present invention. Therefore, we will now combine figure 2 and image 3 Preferred embodiments of the present invention will be described.

[0031] First, in image 3 In step S1, the via hole of the double damascene structure is fabricated. Specifically, see figure 2 A in and figure 2 In B, first make and complete the photolithography and etching of the via layer of the double damascene structure, including the dual damascene dielectric layer 1 and the bottom etch stop layer 2 and the photolithographic pattern 3 of the via layer. It can then be further stripped and cleaned. Those skilled in the art can...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More