Cell-based hierarchical optical proximity correction (OPC) method

A technology of optical proximity effect and correction method, which is applied in optics, original parts for photomechanical processing, microlithography exposure equipment, etc., can solve problems such as low chip production efficiency and cumbersome full-chip OPC correction methods, and achieve improved chip performance. Production efficiency, reduction of storage capacity, and reduction of production errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

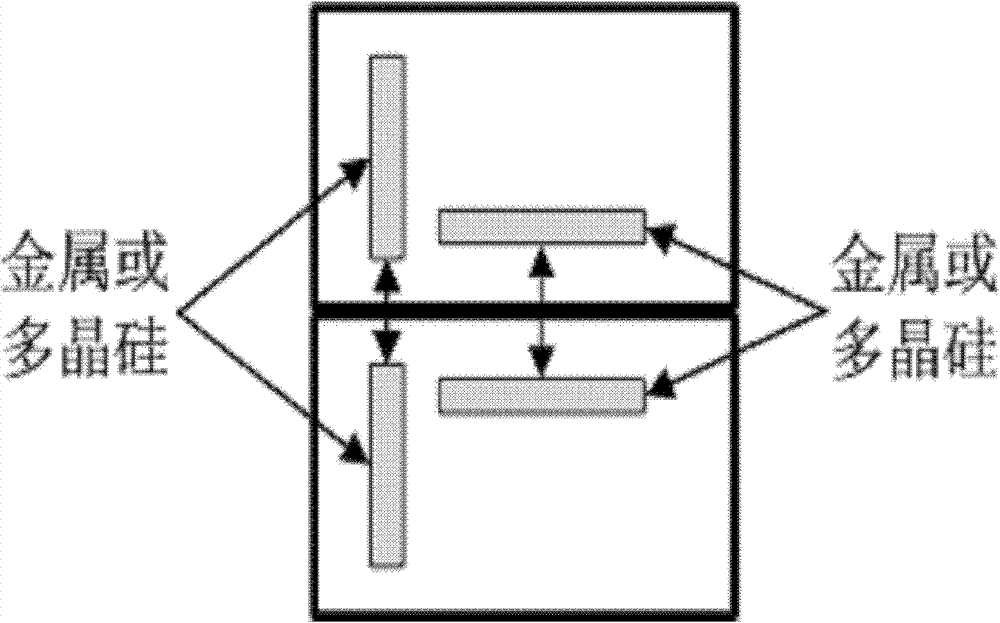

[0026] The hierarchical optical proximity effect correction method based on Cell provided by the present invention is to regularize the graphics of all standard cells, so that the height of the standard cells is equal, and the width is Wt, 2Wt. In this way, the layout is neatly spliced without gaps, reducing The uncertainty of the lithography environment caused by the splicing gap of the traditional standard cell is eliminated, and the adjacent environment of the standard cell library is predictable, which is beneficial to OPC. Perform OPC processing on the standard unit during the construction of the standard unit.

[0027] see figure 1 , although the height of the traditional standard cells is consistent, but their w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More