Packaging method possessing wafer dimension plaster

A technology of wafer size and packaging method, used in electrical components, circuits, semiconductor/solid-state device manufacturing, etc. Heat dissipation performance, effect of size reduction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

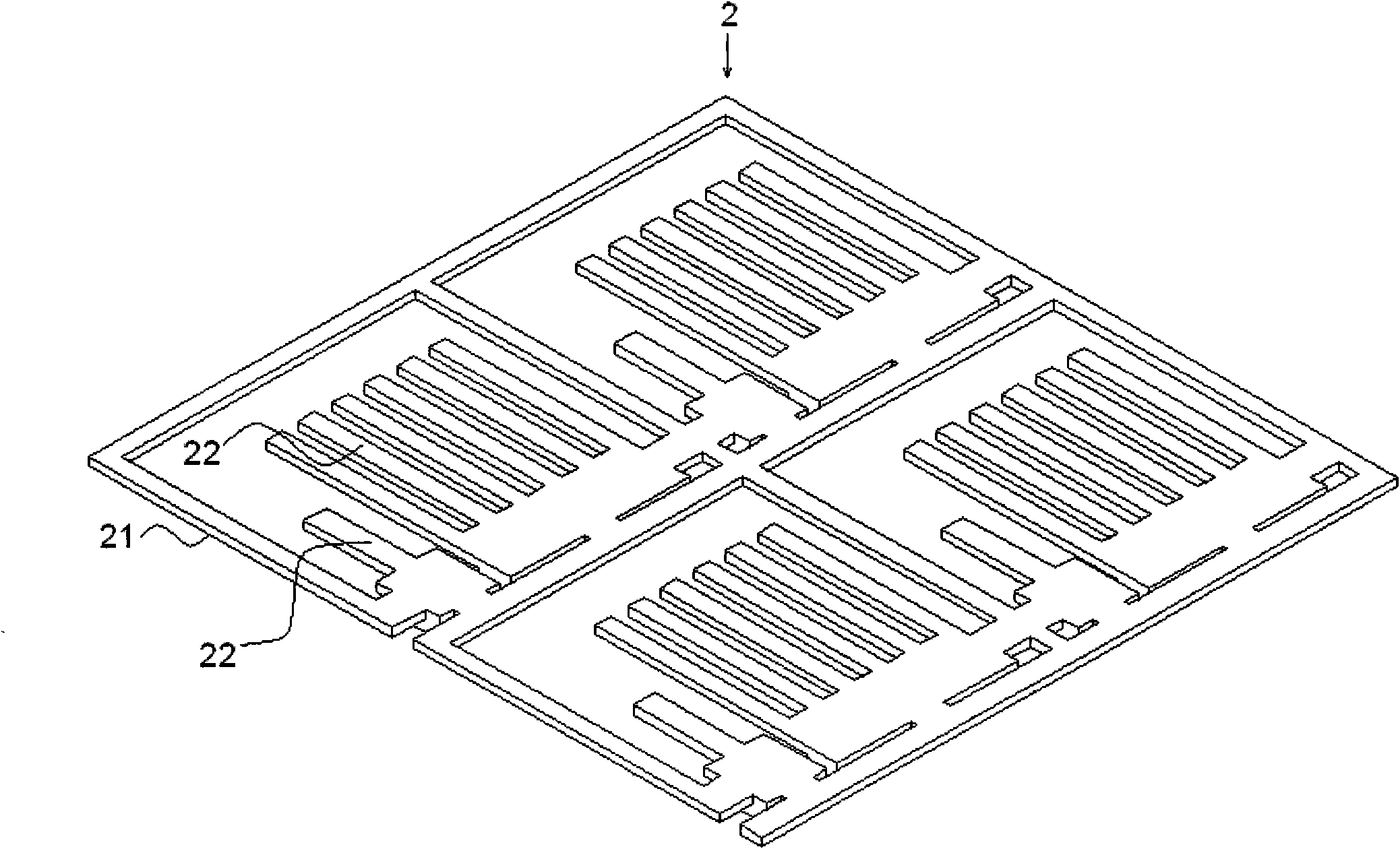

[0050] The present invention provides a package with wafer size patch, which includes a wafer 1 , a patch 2 and a plastic package 3 .

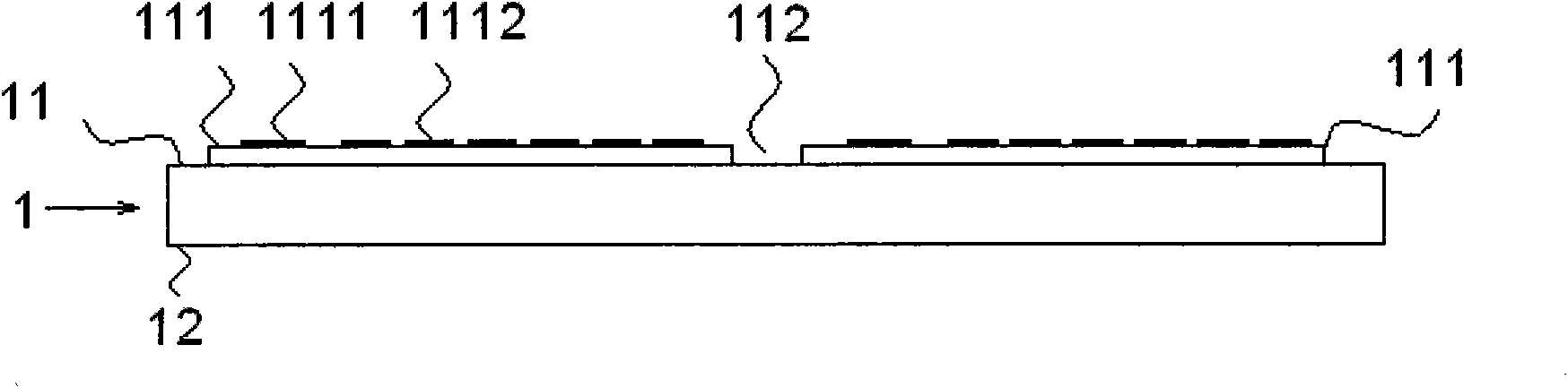

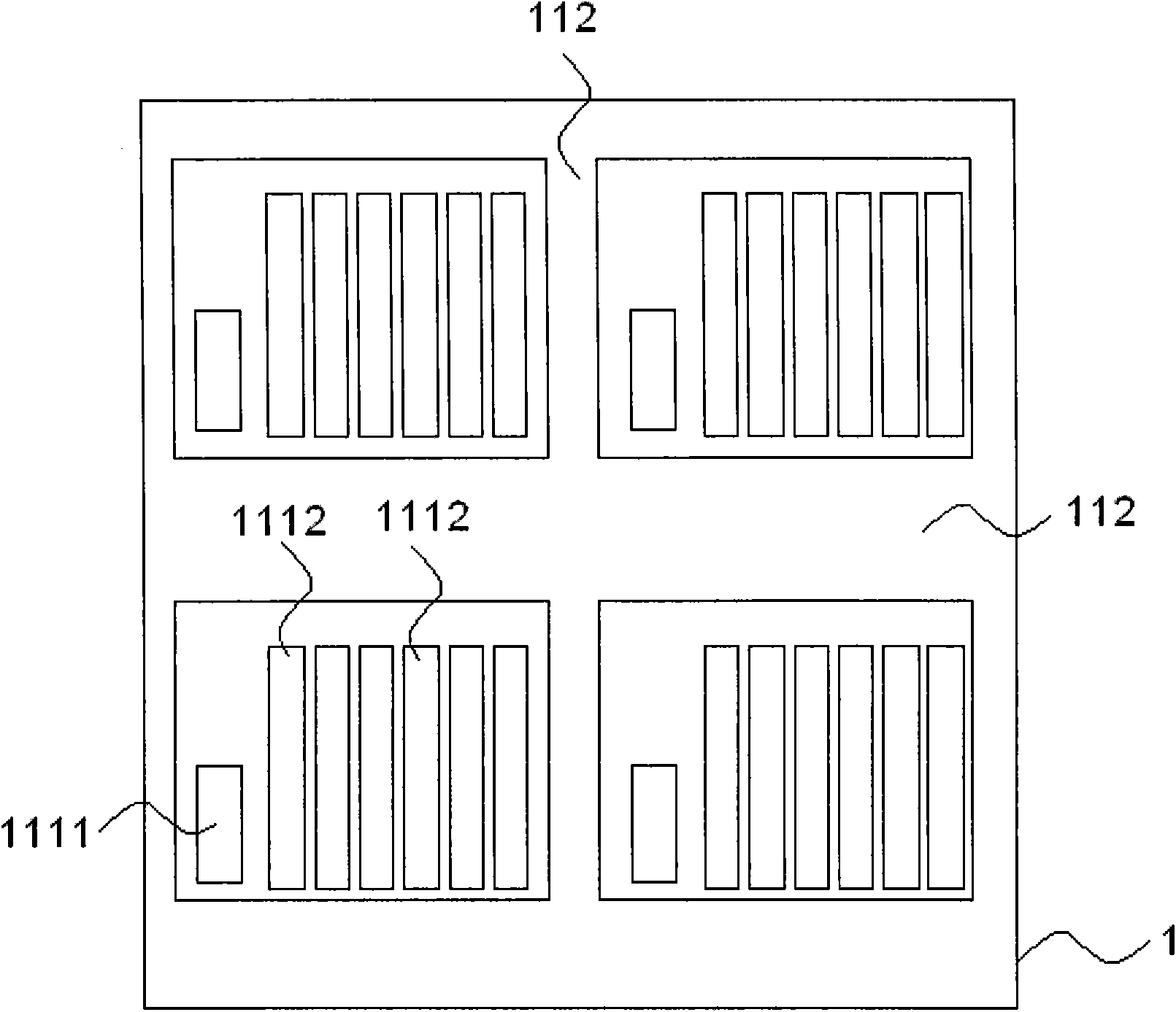

[0051] like Figure 1A ,1B Shown are a side view of the wafer and a front view of the top of the wafer, respectively, with wafer 1 having a wafer top 11 and a wafer bottom 12 . Several chips 111 are produced on the top of the wafer 11, and recessed areas 112 are arranged between the chips 111 on the top of the wafer 11, each chip 111 corresponds to a recessed area 112, and adjacent recessed areas can be separated , can also extend the connection. In a preferred embodiment, the groove area 112 divides the several chips 111 into chip units in both vertical and horizontal directions between the chips 111 . In another preferred embodiment, the recessed area 112 is only provided in one direction (not shown in the figure). The upper surface of each chip is provided with several chip top electrode contact areas 1111 and 1112 . When the area of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More