Multilayer printed wiring board and method for manufacturing multilayer printed wiring board

A multi-layer printing and manufacturing method technology, applied in the field of multi-layer printed circuit board and multi-layer printed circuit board manufacturing, can solve the problems of printed circuit board warpage and other problems, and achieve the effect of flat formation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

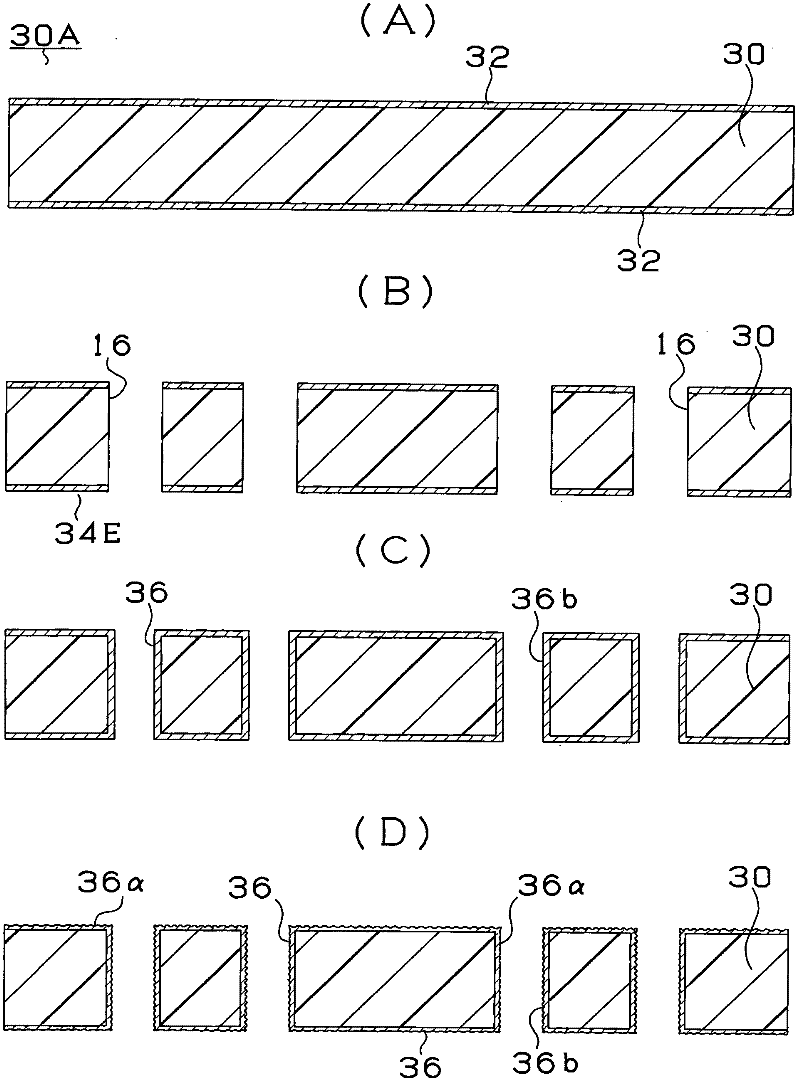

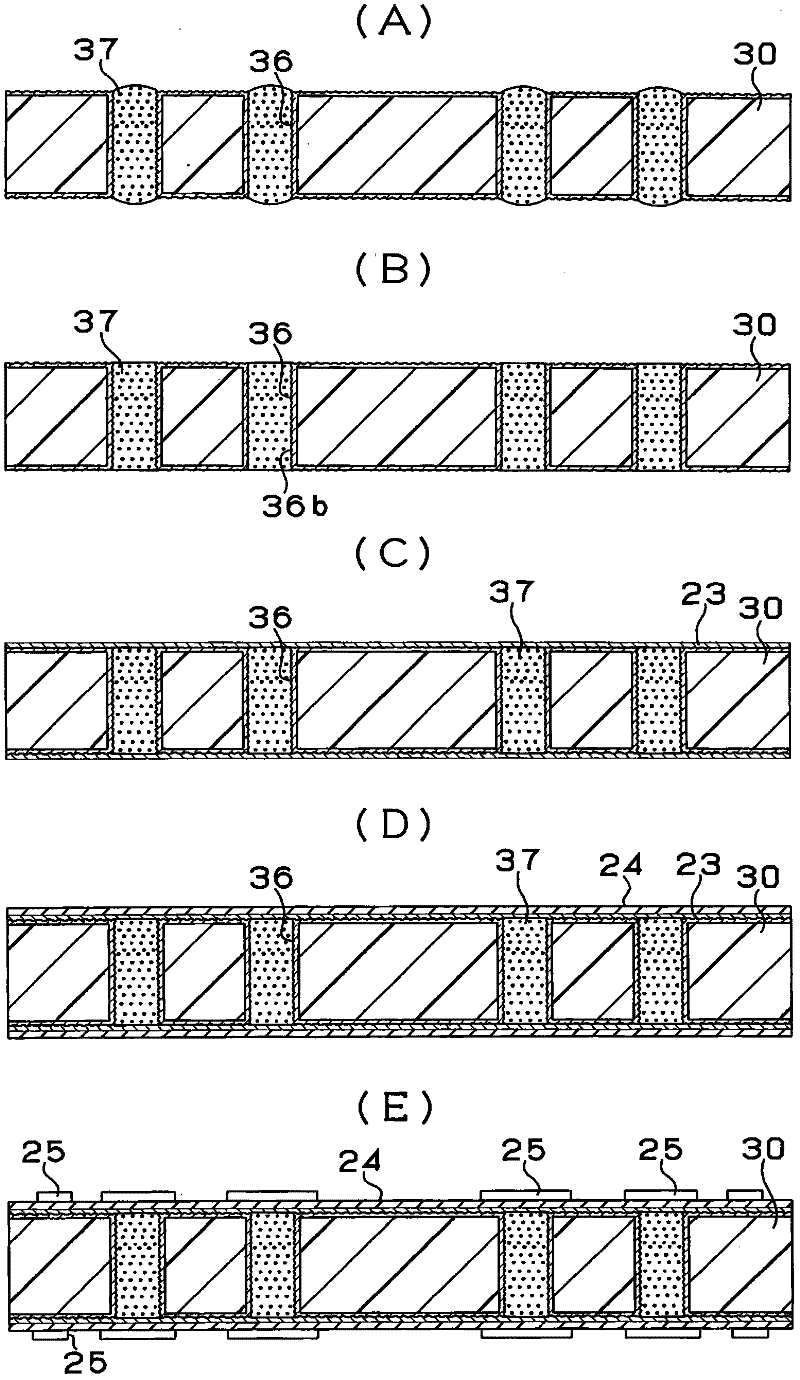

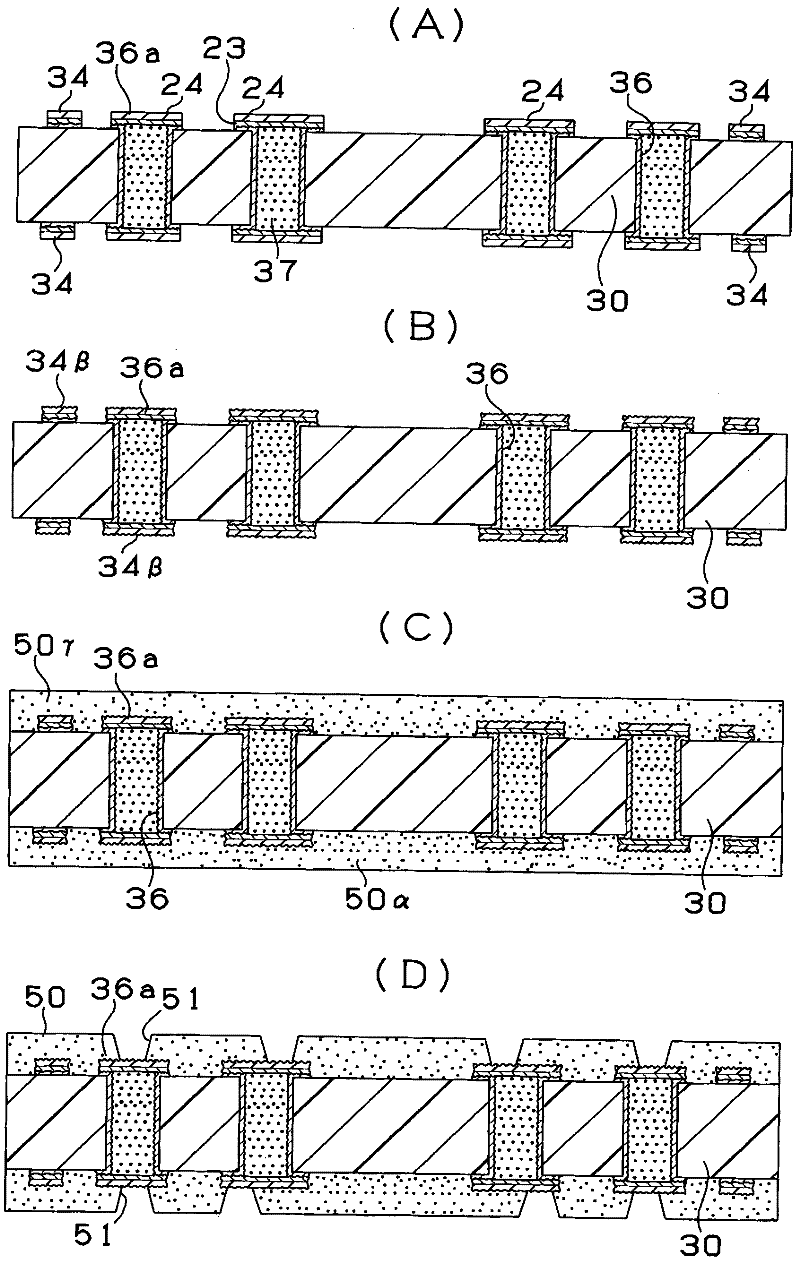

[0045] First, refer to Figure 1 to Figure 10 The structure of the multilayer printed wiring board 10 of the first embodiment of the present invention will be described. Figure 8 A sectional view showing the multilayer printed wiring board 10, Figure 9 expressed in Figure 8 The multilayer printed wiring board 10 is shown in a state where an IC chip 90 is mounted on a daughter board 94 . Figure 10 (B) means Figure 8 b-b cross-section in . Such as Figure 8 As shown, in the multilayer printed wiring board 10 , the conductive circuit 34 is formed on the surface of the core substrate 30 . The surface and the inside of the core substrate 30 are connected by through holes 36 . The via hole 36 is composed of a sidewall conductor layer 36b and a cover plating layer 36a constituting a via land, and the inside of the sidewall conductor layer 36b is filled with a resin filler 37 . Only copper may be filled without filling the resin filler. On the cover plating layer (via-hol...

no. 2 example

[0123] Next, refer to Figure 18 A method of manufacturing a multilayer printed wiring board according to a second embodiment of the present invention will be described.

[0124] In the first embodiment, the recesses for forming conductor circuits and the recesses for forming planar conductors were formed in the interlayer insulating layer by laser light. On the other hand, in the second embodiment, the concave portion for forming a conductive circuit and the concave portion for forming a planar conductor are formed by exposure and development.

[0125] refer to Figure 1 to Figure 5 In (B), the interlayer resin insulating layer 150 is formed in the same manner as in the first embodiment described above. The interlaminar resin insulating layer 150 is made of photosensitive resin (refer to Figure 18 (A)). After placing a mask with a pattern of a conductive circuit and a planar conductor on the interlayer resin insulating layer 150 for exposure, a development treatment is p...

no. 3 Embodiment

[0127] Next, refer to Figure 19 A method of manufacturing a multilayer printed wiring board according to a third embodiment of the present invention will be described.

[0128] In the first embodiment, the recesses for forming conductor circuits and the recesses for forming planar conductors were formed in the interlayer insulating layer by laser light. In contrast, in the third embodiment, the conductive circuit forming recesses and the planar conductor forming recesses were formed using a mold (imprint method).

[0129] refer to Figure 1 to Figure 5 In (B), the interlayer resin insulating layer 150 is formed in the same manner as in the first embodiment described above. And, the molding die 210 formed with patterns for forming conductor circuits, planar conductors, and via holes is positioned at a predetermined position (refer to Figure 19 (A)). The molding die 210 is crimped to the interlaminar resin insulating layer 150 (refer to Figure 19 (B)). Then, the molding...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| current density | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More