A metal wiring etching method

A technology of photoresist and photolithographic patterns, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of the increase of the value of the dielectric coefficient k, dielectric damage, etc., and achieve the reduction of the dielectric coefficient k increase, avoiding the effect of signal transmission speed and

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment 1

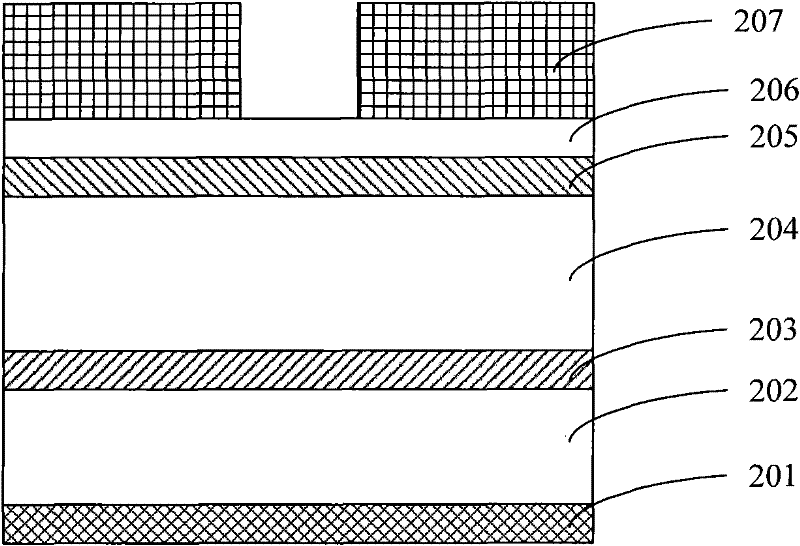

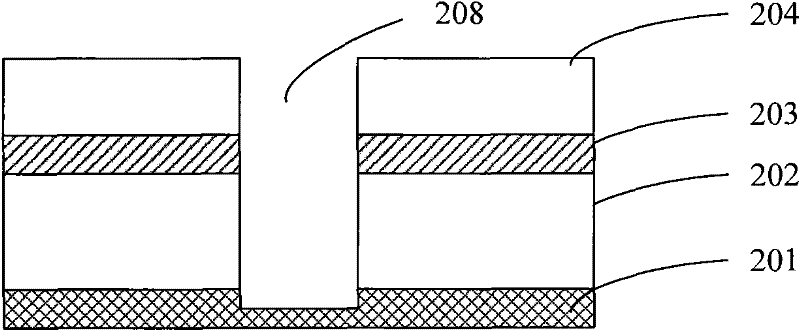

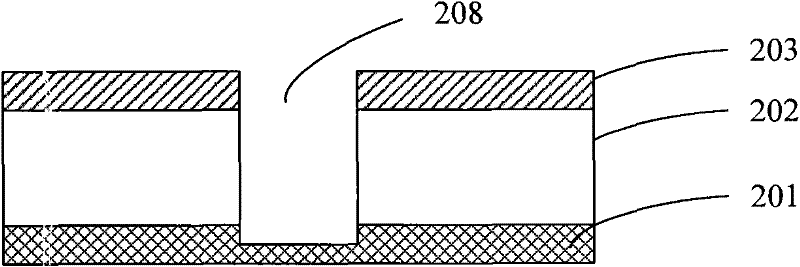

[0037] combined with Figure 3a-3e Details as figure 2 The metal wiring etching method of the present invention shown, its steps are as follows:

[0038] Step 301, Figure 3a It is a schematic cross-sectional structure diagram of step 301 of the metal wiring etching method in the present invention, as Figure 3a As shown, after coating the first photoresist (PR) 407 on the bottom anti-reflective coating (BARC) 406, the first photolithography is used to define the first photolithography pattern for defining the via hole (via);

[0039] In this step, the first photolithography specifically refers to exposing and developing the first PR407 coated on the BARC406 to form a first photolithography pattern. Wherein, the thickness range of coating the first PR407 is 1000 to 3000 angstroms, such as 1000 angstroms, 1500 angstroms and 3000 angstroms; the first photolithography pattern is used to define the opening width of the via holes in the subsequent steps. Figure 3a In the lowe...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More