High-speed data acquisition card implemented on basis of hardware

A technology of high-speed data acquisition and hardware implementation, which is applied in the field of data acquisition cards, can solve problems such as poor positioning accuracy, lack of real-time processing, and unsuitability for real-time detection, and achieve strong anti-interference ability, high acquisition accuracy, and good application value and market value effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

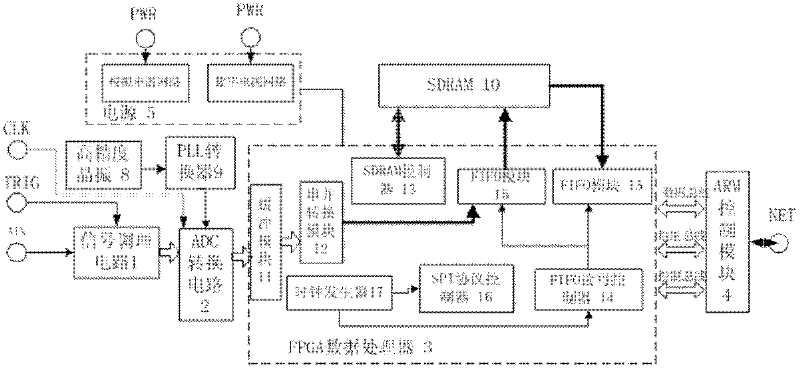

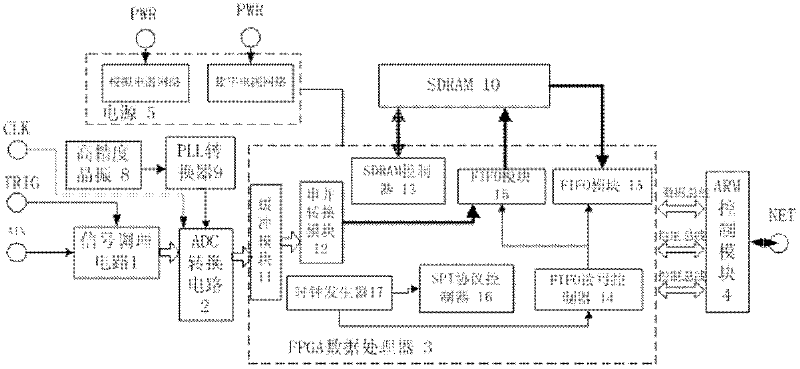

[0016] The present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

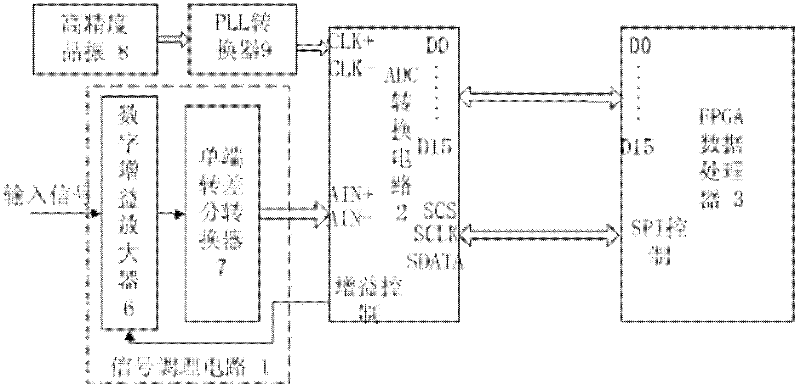

[0017] Such as figure 1 , figure 2 As shown, the present invention includes a signal conditioning circuit 1 , an ADC conversion circuit (analog-to-digital conversion circuit) 2 , an FPGA (programmable gate array) data processor 3 , an ARM control module 4 and a power supply 5 .

[0018] The signal conditioning circuit 1 is composed of a digital gain amplifier 6 and a single-ended to differential converter 7. After the signal conditioning circuit 1 receives the test start signal TRIG, the input signal is sequentially converted into The differential signal is then input into the ADC conversion circuit 2 . Wherein, the operation of the digital gain amplifier 6 is controlled by the ADC conversion circuit 2 .

[0019] The ADC conversion circuit 2 collects the input signal under the control of the external clock signal and the sampling clock input signa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More