Low-cost electrically erasable programmable read only memory (EEPROM) array

A read-only memory, low-cost technology, applied in the field of memory arrays, can solve the problems of large area flash memory, inability to erase bit memory cells, and increase cost requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

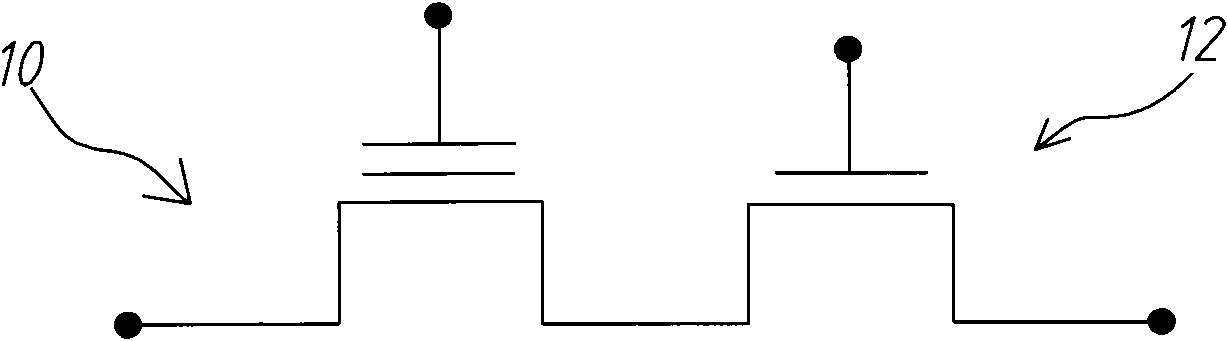

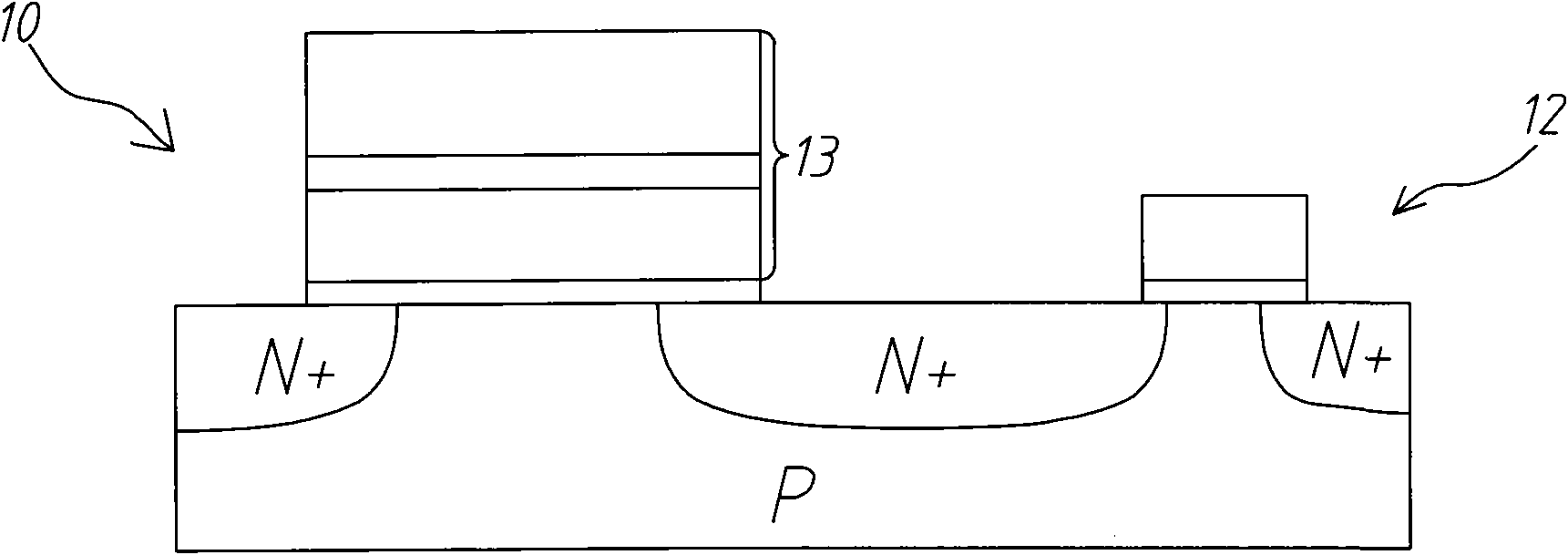

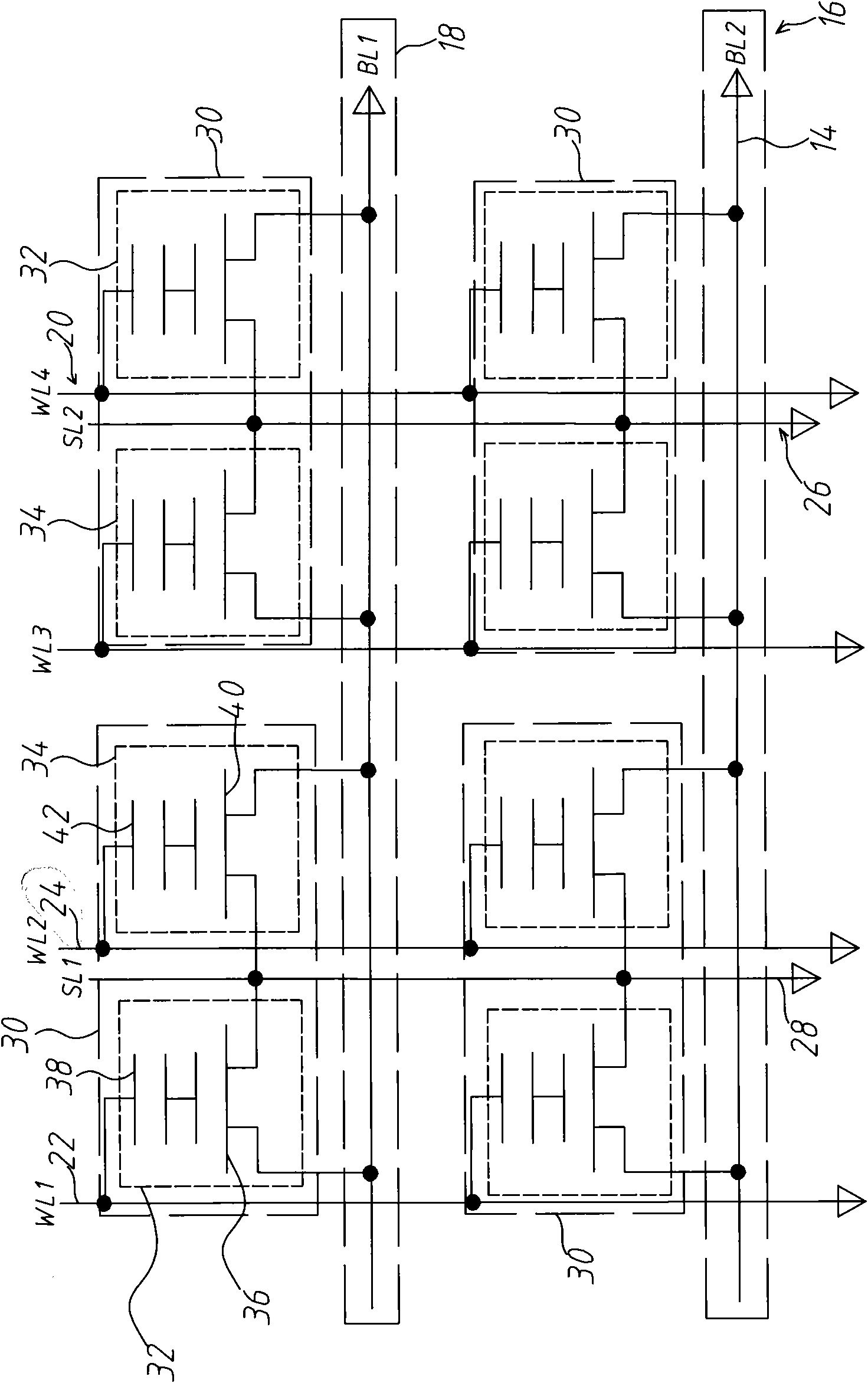

[0024] Please also refer to the following image 3 and Figure 4 , to introduce the first embodiment. The present invention includes a plurality of parallel bit lines 14, which are divided into a plurality of sets of bit lines 16, these sets of bit lines 16 include a first set of bit lines 18, and the first set of bit lines 18 includes a Bitline 14. There are also a plurality of parallel word lines 20 perpendicular to the bit line 14 , which include a first and a second word line 22 , 24 . There are a plurality of parallel common source lines 26 parallel to the word line 20 , which includes a first common source line 28 . The above-mentioned bit lines 14 , word lines 20 and common source lines 26 are connected to a plurality of sub-memory arrays 30 , that is, 2×1 bit memory unit cells. Each sub-memory array 30 is connected to a group of bit lines 16 , two word lines 20 and a common source line 26 . Since the connection relationship between each sub-memory array 30 and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More