Unit structure of MTP (Multi-Time Programmable) device

A cell structure and device technology, applied in the NVM field, can solve the problems of increasing the erasing voltage, increasing the memory cell area of MTP devices, and punching through.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

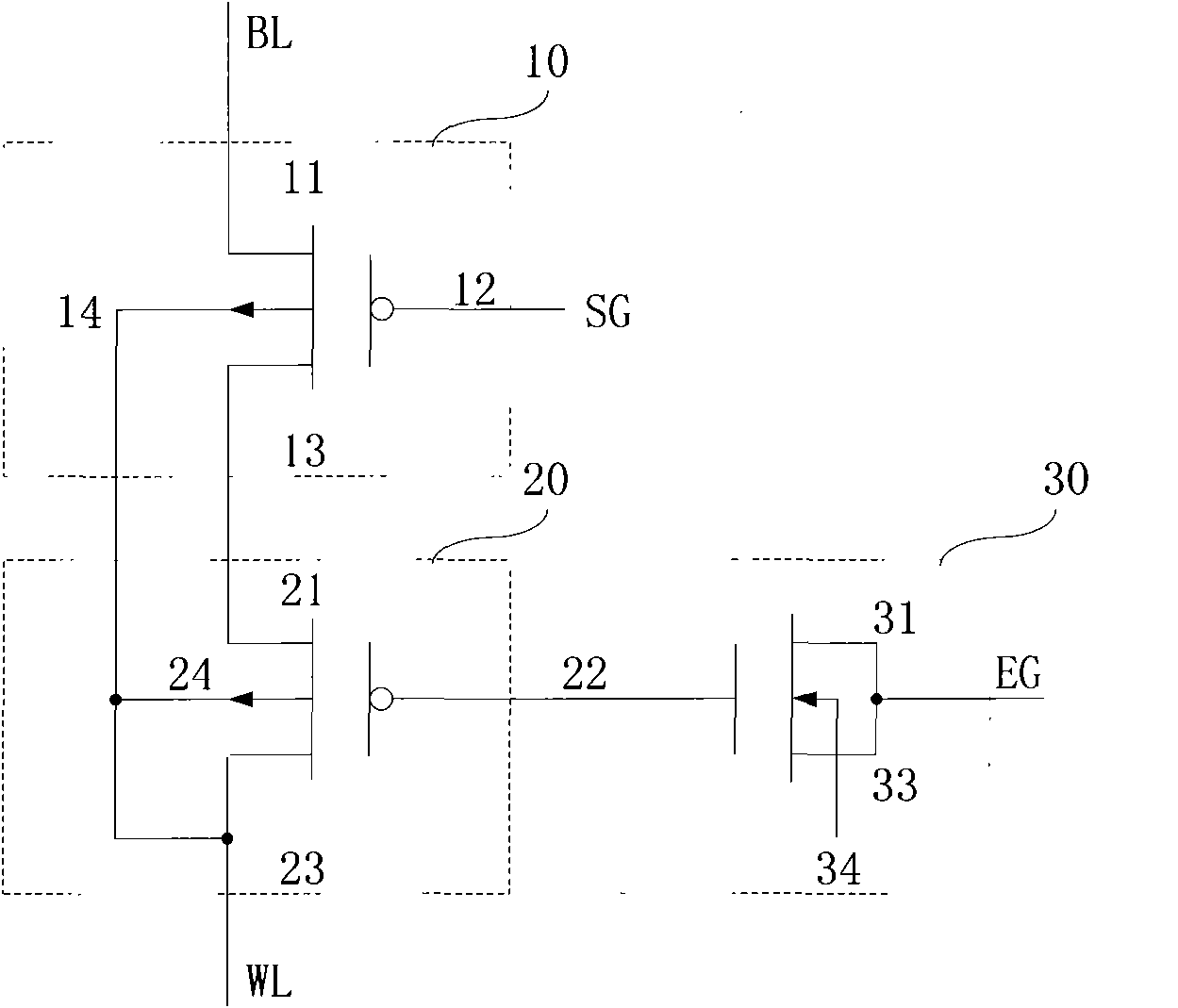

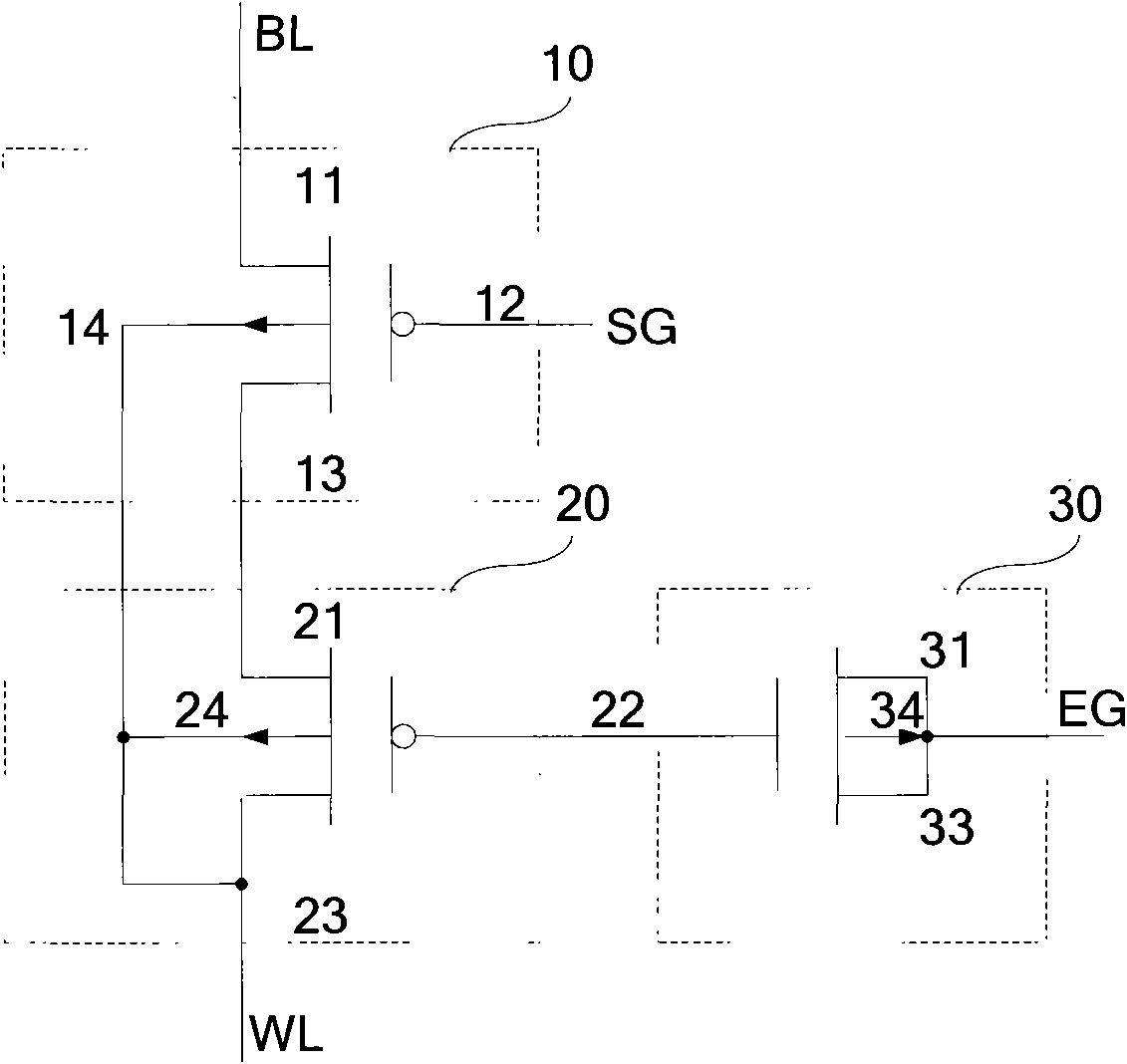

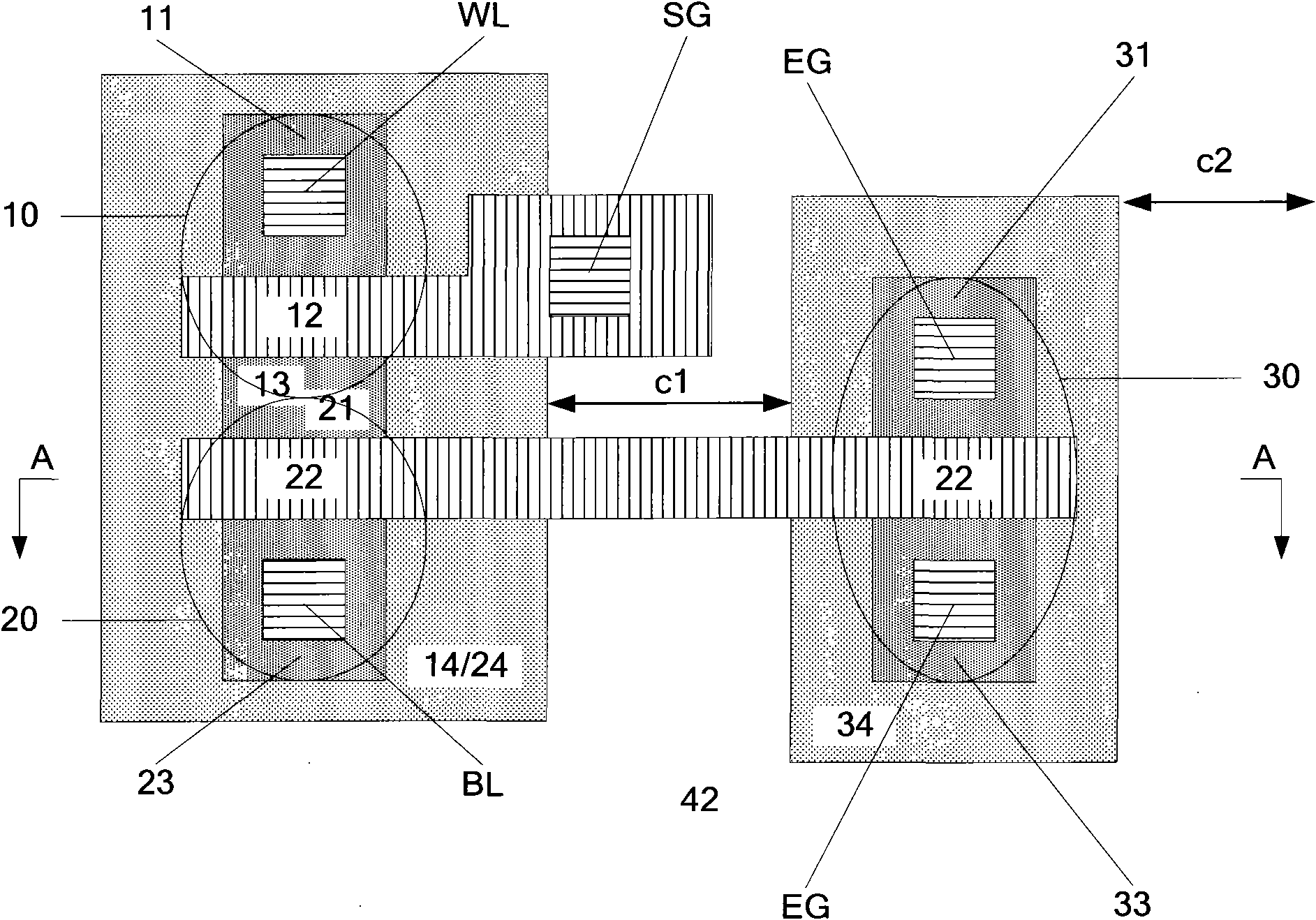

[0025] see Figure 5 , the unit structure of the MTP device of the present invention includes a selection transistor 10 , a programming transistor 20 and an erasing capacitor 50 . The selection transistor 10 and the programming transistor 20 are located in the same n-well 24 . The source 11 of the selection transistor 10 is used as the drain BL, the gate 12 of the selection transistor 10 is used as the selection terminal SG, and the drain 13 of the selection transistor 10 is connected to the source 21 of the programming transistor 20 . The gate 22 of the programming transistor 20 extends outward to form a floating gate, and the floating gate 22 serves as the lower plate of the erasing capacitor 50 . The drain 23 of the programming transistor 20 is connected to the n-well 24 as the programming terminal WL. The upper plate 51 of the erasing capacitor 50 is made of metal, and the metal upper plate 51 of the erasing capacitor 50 serves as the erasing terminal EG.

[0026] The m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More