Peak value sampling retaining circuit and method thereof used for switch power supply

A technology of peak hold circuit and peak sampling, which is applied in the direction of logic circuit coupling/interface, logic circuit connection/interface layout, etc. using field effect transistors, which can solve the problem that the speed of the sample hold circuit decreases and the output voltage cannot reproduce the input signal very well Voltage and other issues to achieve the effect of enhancing load driving capability and avoiding charge accumulation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

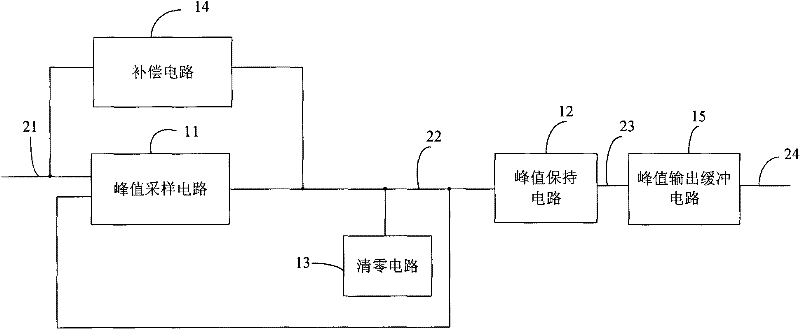

[0055] The content of the present invention will be further described below in conjunction with the accompanying drawings.

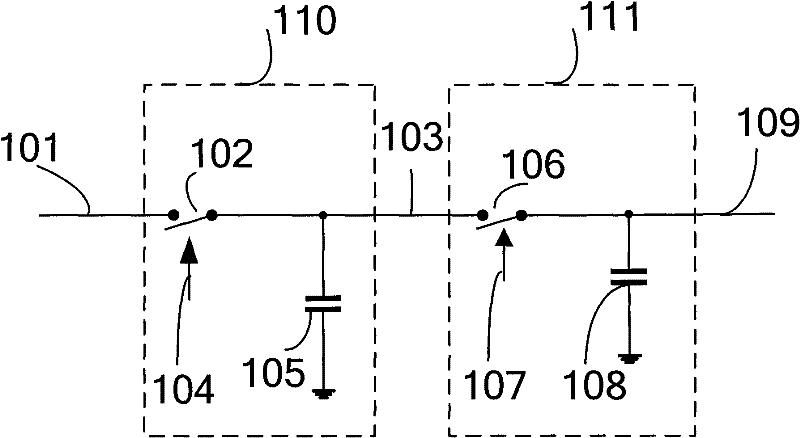

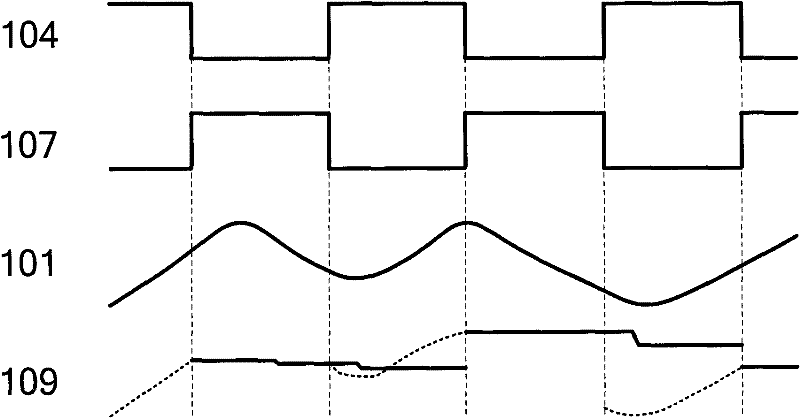

[0056] peak sample-and-hold circuits, such as image 3 , Figure 4 As shown, it includes a peak sampling circuit 11, a compensation circuit 14, a peak hold circuit 12, a peak output buffer circuit 15 and a clearing circuit 13:

[0057] The peak sampling circuit 11 samples the peak voltage 22 of each time point of the input signal 21;

[0058] The compensation circuit 14 is to compensate the charging current of the sampling capacitor 37 of the peak sampling circuit 11, so that the speed of the peak sampling circuit will be accelerated;

[0059] The peak hold circuit 12 holds the peak voltage 22;

[0060] The peak output buffer circuit 15 enhances the output load driving capability of the peak hold circuit 12;

[0061] The clearing circuit 13 clears the peak voltage of the previous period output by the peak sampling circuit 11 to zero in time after the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More