Method and system for reducing trace length and capacitance in a large memory footprint background

A storage module and storage channel technology, applied to static memory, backplanes for installing orthogonal PCBs, instruments, etc., can solve problems such as low speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

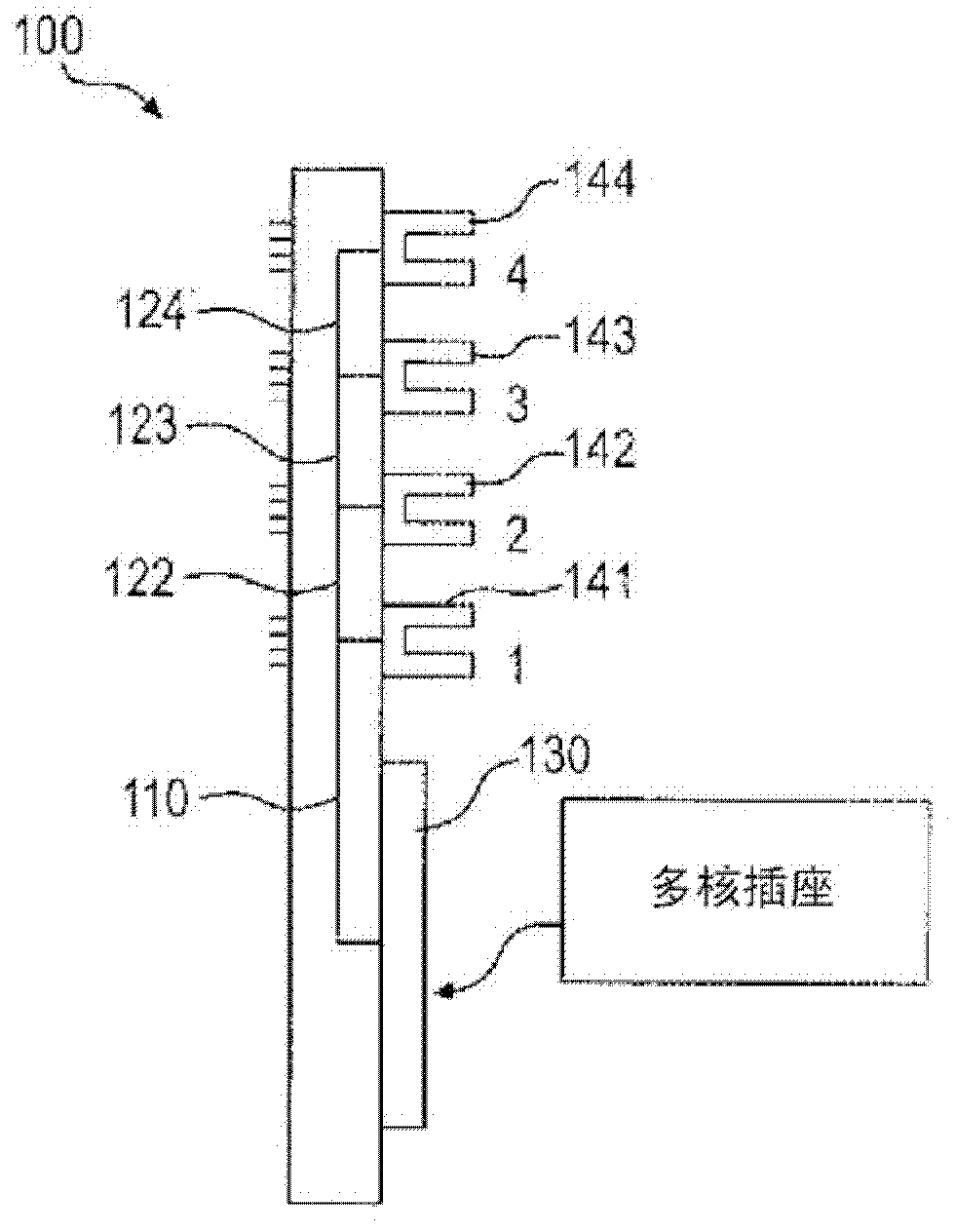

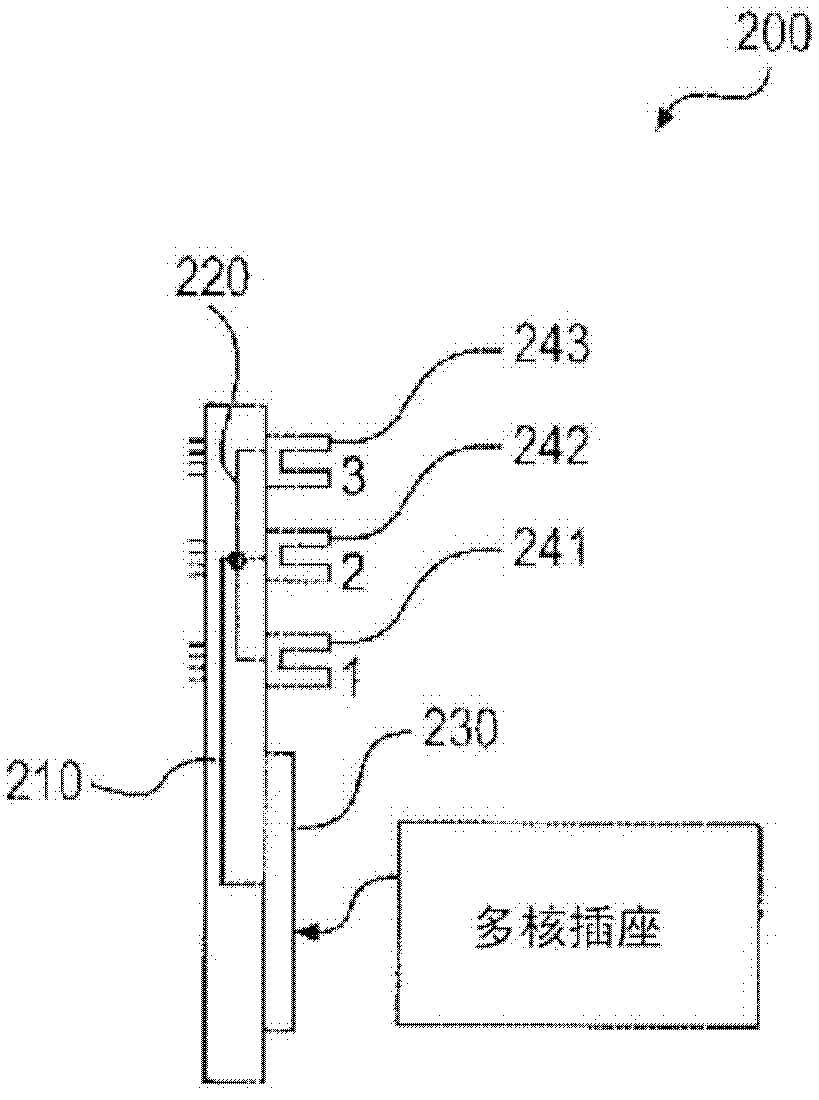

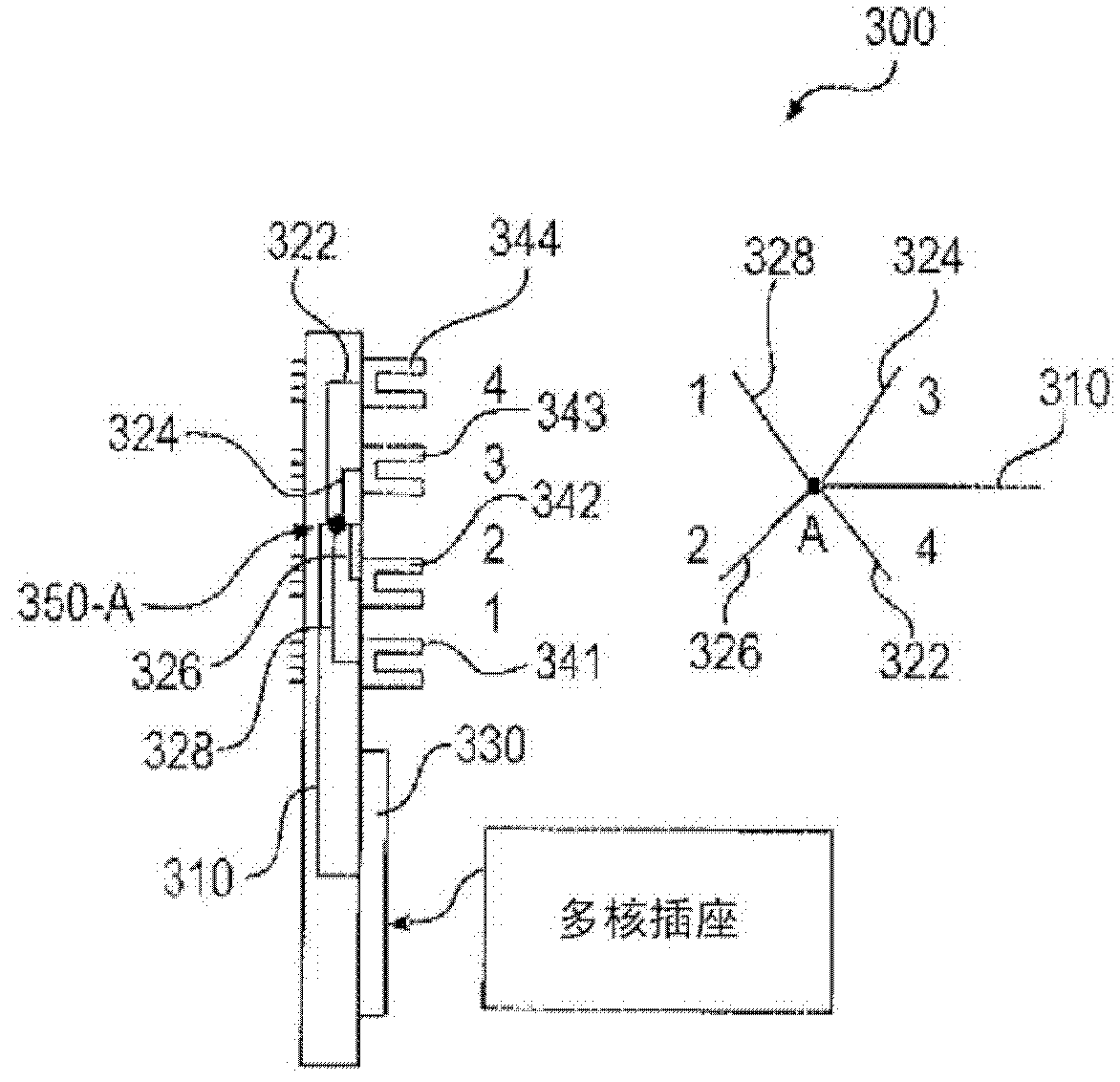

[0011] Systems and methods for reducing trace length and capacitance in large memory footprints are described. As noted above, it is desirable to maximize the number of dual in-line memory module (DIMM) connectors per memory channel while operating at the highest possible frequency that the memory channel can support. As more DIMM connectors are used per memory channel, the total bus bandwidth is affected by trace length and trace capacitance. To reduce overall trace length and trace capacitance, the system and method use a palm tree topology, ie, a back-to-back DIMM layout, to mirror surface mount technology (SMT) DIMM connectors (rather than through-hole connectors) Arranged back-to-back on each side of the printed circuit board (PCB). The system and method can improve signal propagation time compared to conventional topologies such as daisy-chain, T-shaped and star topologies that place all DIMM connectors (or through-hole DIMM sockets) on one side of the PCB.

[0012] f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More